Fターム[5F140BF14]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 2層目材料 (3,048) | 半導体 (411)

Fターム[5F140BF14]に分類される特許

241 - 260 / 411

半導体装置及びその製造方法

【課題】低い閾値電圧のnチャネル型MISトランジスタを含む半導体装置を実現する。

【解決手段】半導体装置は、半導体基板と、半導体基板の主面に形成されたn型半導体領域とp型半導体領域と、半導体基板上に形成され、n型半導体領域とp型半導体領域を露出するように形成された第1と第2のトレンチを有する第1の絶縁層と、第1と第2のトレンチの側壁と底部に沿って形成されたゲート絶縁膜と、第1のトレンチの側壁と底部に沿って形成されゲート絶縁膜を介して内張りされた第1の金属層と、第2のトレンチの側壁と底部に沿って形成されゲート絶縁膜を介して1モノレイヤー以上で1.5nm以下の厚さに内張りされた第2の金属層と、第2の金属層上に内張りされたアルカリ土類金属元素、III族金属元素の単体、窒化物、炭化物、酸化物の内の少なくとも1つの金属元素を含む第3の金属層と、第1と第2のソース/ドレイン領域を具備することを特徴とする。

(もっと読む)

半導体素子

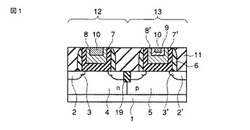

【課題】インバータ回路など、電気接続された2つの半導体スイッチによるスイッチング動作を行なうための電気回路において、寄生インダクタンスおよびオン抵抗を抑制することができる構造の半導体素子を提供すること。

【解決手段】この半導体素子は、基板1と、基板1の一方側に形成される半導体積層構造部2とを備える。半導体積層構造部2は、n型層5、このn型層5の一方側(下面側)に積層されたp型層4、およびこのp型層4に積層されたn型層3からなる縦型npn構造の第1半導体積層構造8と、n型層5をこの第1半導体積層構造8と共有し、n型層5、このn型層5の他方側(上面側)に積層されたp型層6、およびこのp型層6に積層されたn型層7からなる縦型npn構造の第2半導体積層構造9とを備える。

(もっと読む)

ストレッサ層を有するデュアル仕事関数デバイスおよびその製造方法

【課題】高誘電率ゲート誘電体を有するMOSFETトランジスタの製造方法の提供。

【解決手段】デュアル仕事関数半導体デバイスの製造方法であって、第1領域と第2領域とを有する基板を提供する工程と、第1領域と第2領域とを覆うようにゲート誘電体2を形成する工程と、該ゲート誘電体2を覆うように金属ゲート層3を形成する工程であって、歪を導入することにより変調可能な(堆積したままの)第1仕事関数を有する金属ゲート層3を形成する工程と、第1領域の上の金属ゲート層3の(堆積したままの)第1仕事関数に、第1の予め決められた仕事関数シフト(ΔWF1)を導入するように第1歪を選択し、第1領域の上の金属ゲート層3を覆うように第1歪導電層4を選択的に形成して、第1歪導電層が金属ゲート層に選択された第1歪を働かせる工程とを含む方法を提供する。この方法により得られるデュアル仕事関数半導体デバイスも記載される。

(もっと読む)

半導体デバイスを形成する方法

【課題】 ボイドフリーかつシームフリーの金属ゲート導体層が比較的薄い高kゲート誘電体層の上に位置決めされている少なくとも1つの高アスペクト比ゲート構造を有する相補型金属酸化膜半導体(CMOS)デバイスを形成する方法を提供する。

【解決手段】 これらの方法実施形態は、高アスペクト比ゲート・スタック開口部を下から上に金属ゲート導体層で充填するために電気メッキ・プロセスを使用するゲート交換戦略を取り入れている。電気メッキ・プロセス用の電子の発生源は、基板の裏面を直接通過する電流である。これは、シード層の必要性を排除し、ボイドまたはシームなしで金属ゲート導体層が形成されることを保証するものである。さらに、実施形態次第で、電気メッキ・プロセスは、所与の領域への電子流を増強するために(すなわち、メッキを増強するために)照明を受けて実行され、所与の領域への電子流を防止するために(すなわち、メッキを防止するために)暗闇で実行される。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 大幅なプロセスコスト増を伴うことなく、チャネルに歪を発生させることが可能な半導体装置の製造方法を提供する。

【解決手段】 (a)半導体基板の一部の表面上に、半導体膜と、該半導体膜よりも密度の高いブロック膜とがこの順番に積層されたゲートパターンを形成する。(b)ゲートパターンをマスクとして、半導体基板の表層部に、ソース及びドレイン用の不純物を注入する。(c)ゲートパターンをマスクとして、半導体基板内に、ソース及びドレイン用の不純物とは異なる歪形成用の不純物を注入する。(d)半導体基板を熱処理し、歪形成用の不純物が注入された領域を再結晶化させる。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極、ソース電極またはドレイン電極にタングステン膜を用いた半導体装置において、nMOSとpMOS間での抵抗差を低減可能な半導体装置の製造方法を提供する。

【解決手段】シリコン基板10上に、ゲート電極14a,14bとソース/ドレイン拡散層16a,16bとを有するnMOS及びpMOSを形成し、ゲート電極14a,14b及びソース/ドレイン拡散層16a,16b上に、タングステン膜17を選択的に形成し、タングステン膜17を覆うように、絶縁膜(エッチングストップシリコン酸化膜18、シリコン窒化膜19)を形成し、pMOS領域12bの絶縁膜を除去し、pMOS領域12bのタングステン膜17上に、タングステン膜20を選択的に形成する。

(もっと読む)

フィン型トランジスタ

【課題】フィン内部のチャネル部に垂直応力を与える事が可能なフィン型トランジスタを提供する。

【解決手段】基板と、前記基板上に形成される複数の半導体フィンと、前記半導体フィン内のチャネル領域を覆い金属または導電性を持つ化合物や、ポリシリコンで形成されるゲート電極と、前記ゲート電極の内部に含まれその両側に存在する前記半導体フィンに対し応力源となるよう格子定数の異なる材料や密度の異なるアモルファスシリコン、または線膨張係数の異なる材料で形成される埋め込み部材とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】歪み発生層に緩和が生じにくい半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板11の上に形成されたゲート電極15と、ゲート電極15の両側面上に形成され、断面L字状の内側サイドウォール17Bと、半導体基板11におけるゲート電極15の両側方の領域に埋め込まれた歪み発生層19とを備えている。内側サイドウォール17Bは、5×1019/cm3以上の炭素を含む炭素含有シリコン酸化膜からなる。歪み発生層19は、1%以上の炭素を含む炭素含有シリコンエピタキシャル層を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】高誘電率膜をゲート絶縁膜として用い、pチャネル型MISFETおよびnチャネル型MISFETのそれぞれに要求されるしきい値電圧を容易に実現できる相補型MISFETおよびその製造技術を提供する。

【解決手段】n型ウエル3およびp型ウエル4のそれぞれの表面に清浄な酸化シリコン膜5を形成した後、酸化シリコン膜5上に2A族元素の酸化物、3A族元素の酸化物、3B族元素の酸化物、4A族元素の酸化物、および5A族元素の酸化物等からなる酸素欠損調整層6と、高誘電率膜8と、水素に対する還元触媒効果を有する導電性膜12とを順次堆積し、H2を含む雰囲気中にて基板1に対して熱処理を施すことで酸素欠損調整層6と酸化シリコン膜5との間にダイポールを形成する。その後、導電性膜12、高誘電率膜8、酸素欠損調整層6および酸化シリコン膜5等をパターニングしてゲート電極およびゲート絶縁膜を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】それぞれが最適なゲート絶縁膜及びゲート電極を有するp型MISFET及びn型MISFETを備え且つ不良の原因となるポリシリコン膜残渣が発生することがない半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板10の第1領域10Aの上に形成された第1のゲート絶縁膜13Aと、第1のゲート絶縁膜13Aの上に形成された第1のゲート電極14Aと、半導体基板10の第2領域10Bの上に形成された第2のゲート絶縁膜13Bと、第2のゲート絶縁膜13Bの上に形成された第2のゲート電極14Bとを備えている。第1のゲート絶縁膜13Aは、第1の金属を含む第1の材料からなる第1の絶縁膜を有し、第2のゲート絶縁膜13Bは、第1の材料と第2の金属を含む第2の材料とが混合された第2の絶縁膜を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】nチャネル及びpチャネルのゲート構造が異なり且つメタルゲート電極を有する半導体装置において、ゲート電極パターン形成時のドライエッチングでゲート絶縁膜の突き抜けが発生しないようにする。

【解決手段】ゲート絶縁膜105と接する第2ゲート電極材料膜(TiN膜)111がゲート電極151の一部として形成されないnチャネル領域103上に、第2ゲート電極材料膜(TiN膜)111のエッチング時にオーバーエッチング吸収層として機能する第1ゲート電極材料膜(ポリシリコン膜)107を予め形成しておく。

(もっと読む)

半導体装置及びその製造方法

【課題】駆動能力を低下させることなく、半導体装置内部の高電界が与える影響によって生じるGIDLを低減する。

【解決手段】ゲート電極108は、ゲート電極108のチャネル長方向の中央部に位置し且つ高誘電率膜107つまりゲート絶縁膜と接する第1の導電部108Aと、ゲート電極108のチャネル長方向の両端部に位置し且つ高誘電率膜107つまりゲート絶縁膜と接する第2の導電部108Bとを含む。第1の導電部108Aの第1の仕事関数と第2の導電部108Bの第2の仕事関数とが異なっている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】仕事関数が所望の値に制御されたメタルゲート電極を備える半導体装置を提供する。

【解決手段】半導体基板2上に、ゲート絶縁膜4を介して、N等を含有する仕事関数制御層5、SiまたはAlを含んだ中間層6、およびMoN層等の低抵抗層7が積層された構造を有するメタルゲート電極を形成する。その形成時には、ゲート絶縁膜4上に仕事関数制御層5、中間層6および低抵抗層7の各層の積層後、ゲート加工を行い、LDD領域9、サイドウォール8およびソース・ドレイン領域10を順に形成して、半導体基板2に導入した不純物の活性化アニールを行う。仕事関数制御層5と低抵抗層7との間に中間層6を設けたことにより、仕事関数制御層5へのあるいは仕事関数制御層5からのN等の拡散が抑制され、その仕事関数の変動が抑制されるようになる。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化されても、EOTの増膜が抑制され、且つ、良好な品質を有する高誘電率膜を備えた信頼性の高い半導体装置及びその製造方法を提供すること。

【解決手段】半導体装置は、半導体基板1内に形成された第1導電型の第1の領域3及び第2導電型の第2の領域4と、半導体基板1上であって、第1の領域3及び第2の領域4の上に形成されたゲート絶縁膜5と、ゲート絶縁膜5上に形成された保護膜6と、保護膜6のうち第1の領域3の上に設けられた部分上に形成され、金属からなる第1のゲート電極9と、保護膜6のうち第2の領域4の上に設けられた部分上に形成された第2のゲート電極12とを備えている。ゲート絶縁膜5及び保護膜6は、高誘電率膜からなる。

(もっと読む)

半導体装置およびその製造方法

【課題】高誘電率ゲート絶縁膜を有するCMISFETにおいて、nMISとpMISの双方で閾値電圧(絶対値)の低下を実現する。

【解決手段】pMISの領域においてシリコン酸化膜6に接するようにゲート絶縁膜6の真上にアルミニウム酸化膜(Al2O3)4を形成し、nMIS領域においてシリコン酸化膜2に接するようにシリコン酸化膜2の真上に高誘電率ゲート絶縁膜10を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、FIN状の半導体部やゲート電極を精度良く形成すること、又は素子間の特性バラツキを改善することで、特性の優れたFIN型トランジスタを備える半導体装置を提供することを目的とする。

【解決手段】本発明は、一方にソース領域、他方にドレイン領域が形成されたFIN状の半導体部10と、ソース領域とドレイン領域との間で、FIN状の半導体部10をゲート絶縁膜を介して囲むように形成されたゲート電極17とを備える半導体装置である。そして、本発明に係る1つ解決手段は、ゲート電極17が、ウェットエッチング可能なメタル材料又はシリサイド材料を用いている。

(もっと読む)

半導体装置の製造方法

【課題】 ゲート絶縁膜が大気やメタル電極のエッチング液等に曝されて劣化することなく、仕事関数の異なるnMOS、pMOSに適したメタルゲートMISFETを含む半導体装置の製造方法を提供する。

【解決手段】 メタル電極を有するn型MISトランジスタ及びp型MISトランジスタを備えた半導体装置の製造方法であって、単結晶シリコン基板100上に設けられたゲート絶縁膜102と、ゲート絶縁膜102上に設けられた第一の金属膜103、第二の金属膜104、第三の金属膜105、導電層106を備えたゲート電極108とを備えた構造であって、熱工程によって第二の金属膜104の構成元素を第一の金属膜103を通してゲート絶縁膜102中へ拡散させることによって、n型MISトランジスタ及びp型MISトランジスタそれぞれに適した仕事関数に変化させる。

(もっと読む)

半導体装置

【課題】電流駆動能力が高いMOSFETを備えた半導体装置を提供する。

【解決手段】半導体装置1において、シリコン基板2の表面にNMOS3を形成し、NMOS3のチャネル領域7の直上域に、内部に圧縮応力を有する圧縮応力膜8を設け、シリコン基板2上における少なくともチャネル領域7の直上域の周囲に、内部に引張応力を有する引張応力膜9を設ける。

(もっと読む)

半導体デバイス、半導体デバイスを形成する方法、および集積回路

【課題】 相互に異なるしきい値電圧要件を有する複数のトランジスタを結合するための技法を提供する。

【解決手段】 一態様では、半導体デバイスは、第1および第2のnFET領域と第1および第2のpFET領域とを有する基板と、第1のnFET領域の上の基板上のロジックnFETと、第1のpFET領域の上の基板上のロジックpFETと、第2のnFET領域の上の基板上のSRAM nFETと、第2のpFET領域の上の基板上のSRAM pFETとを含み、そのそれぞれが、高K層の上の金属層を有するゲート・スタックを含む。ロジックnFETゲート・スタックは、高K層から金属層を分離するキャッピング層をさらに含み、キャッピング層は、ロジックpFET、SRAM nFET、およびSRAM pFETのうちの1つまたは複数のしきい値電圧に対してロジックnFETのしきい値電圧をシフトするようにさらに構成される。

(もっと読む)

半導体装置の製造方法

【課題】所望の形状を有するゲート電極を形成することのできる半導体装置の製造方法を提供する。

【解決手段】本発明の実施の形態に係る半導体装置の製造方法は、半導体基板上に形成された半導体膜を加工してゲート電極を形成する工程と、HBr、Cl2、CF4、SF6若しくはNF3のうち少なくとも1つおよびO2を含み、O2の流量が全体の流量の合計の80%よりも大きいガス、または、HBr、Cl2、CF4、SF6若しくはNF3のうち少なくとも1つ、O2およびN2を含み、O2およびN2の流量の合計が全体の合計の80%よりも大きいガスのプラズマ放電により、前記ゲート電極の側面に保護膜を形成する工程と、前記保護膜を形成した後、前記半導体基板上の前記半導体膜の残渣を除去する工程と、を含む。

(もっと読む)

241 - 260 / 411

[ Back to top ]