Fターム[5F140BF14]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 2層目材料 (3,048) | 半導体 (411)

Fターム[5F140BF14]に分類される特許

181 - 200 / 411

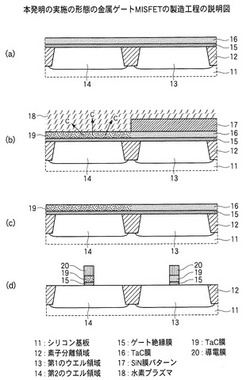

絶縁ゲート型半導体装置及びその製造方法

【課題】 絶縁ゲート型半導体装置及びその製造方法に関し、炭化タンタル膜の仕事関数を適正に選択的に制御する。

【解決手段】 半導体基板上にゲート絶縁膜を形成する工程と、前記ゲート絶縁膜上に炭化タンタル膜を成膜する工程と、前記炭化タンタル膜の一部を露出する開口を有するマスクパターンを形成したのち、水素プラズマ処理を行う工程とを設ける。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の絶縁膜の上に形成される金属配線または金属電極の接着力を向上させる。

【解決手段】窒化タングステン6bをタングステン6cの側面にまで設けて、タングステン6cと窒化タングステン6bとが接触している面積を増やす。ゲート絶縁膜2上に、ゲート絶縁膜2との接着力が強いポリシリコンサイドウォール5を配置する。タングステン6cの側面にある窒化タングステン6bにはポリシリコンサイドウォール5を密着させる。

(もっと読む)

半導体装置

【課題】コンタクトの位置ずれが回路の特性に与える影響を低減した半導体装置を提供する。

【解決手段】この半導体装置は、半導体層10に設けられた素子分離膜20と、素子分離膜20により区画された素子形成領域と、素子形成領域上及び素子分離膜20上を延伸しているゲート配線140と、ゲート配線140の側壁に形成されたサイドウォール150と、素子分離膜20上に位置するゲート配線140に接続するコンタクト200とを備える。ゲート配線140の側壁は、少なくとも上部においてコンタクト200に接触してる領域144を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化に対応でき、High−kゲート絶縁膜を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101と、p型層103上に設けられた第1のゲート絶縁膜115、TiNからなる第1のゲート電極116と、及び不純物を含む半導体からなる第1の上部ゲート電極117を有するNチャネル型MOSトランジスタ106と、n型層102上に設けられた第2のゲート絶縁膜109、TiN結晶からなり、(111)配向/(200)配向が1.5以上となるTiN層を少なくとも一部に含む第2のゲート電極110、及び不純物を含む半導体からなる第2の上部ゲート電極111を有するPチャネル型MOSトランジスタ105とを備えている。

(もっと読む)

デュアル仕事関数半導体デバイスの製造方法および製造されたデバイス

【課題】デュアル仕事関数半導体デバイスの製造方法を提供する。

【解決手段】半導体基板100上に、これと接触するゲート誘電体層104を形成する工程と、ゲート誘電体層の上に、これと接触する金属層105を形成する工程と、金属層の上に、これと接触するゲート充填材料の層106を形成する工程と、ゲート誘電体層、金属層、およびゲート充填層をパターニングして、第1ゲートスタックと第2ゲートスタックとを形成する工程と、半導体基板中に、ソースおよびドレイン領域109を形成する工程と、第1および第2ゲートスタックの少なくとも片側の第1および第2領域中に誘電体層を形成する工程と、その後に第2ゲートスタックのみからゲート充填材料を除去し、下層の金属層を露出させる工程と、露出した金属層を金属酸化物層1051に変える工程と、第2ゲートスタックを他のゲート充填材料115を用いて再形成する工程とを含む。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】金属層にノッチ形状が形成されず、多結晶シリコン層から金属層へのシリコンの拡散を防止したMIPSゲート構造を有する半導体装置を提供する。

【解決手段】MIPSゲート構造を有する半導体装置の製造方法において、MIPSゲートの作製工程は、半導体基板上に、ゲート絶縁膜、メタル層、および多結晶シリコン層を順次堆積する工程と、多結晶シリコン層の上に形成したエッチングマスクを用いて、多結晶シリコン層をエッチングする工程と、メタル層を選択的にエッチングして、下方に向かって側壁がテーパ状に張り出したメタル層を残す工程と、多結晶シリコン層の側壁を含む平面から外方に突出したメッキ層のテーパ部を酸化して、酸化テーパ部とする酸化工程と、酸化テーパ部をエッチングで除去する除去工程とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】良好な形状のsingle metal/dual high−k構造を形成し、nMOS、pMOSそれぞれに適したフラットバンド電圧を得ることができる半導体装置を得ること。

【解決手段】本発明の一実施形態における半導体装置100は、第1導電型のMOSFET10と、第2導電型のMOSFET20を有する。第1および第2導電型のMOSFET10,20は、半導体基板1上に形成された第1の絶縁膜2と、第1の絶縁膜2上に形成され、第1の絶縁膜2よりも誘電率の高い絶縁材料からなる第2の絶縁膜4と、第2の絶縁膜4上に形成され、第2の絶縁膜4に拡散して仕事関数を制御する材料を含むメタル層5を下層に有するゲート電極7と、を備える。また、第2導電型のMOSFET20は、第1の絶縁膜2と第2の絶縁膜4との間に形成され、仕事関数を制御する材料が第1の絶縁膜2界面に拡散するのを防止する拡散防止膜3をさらに備える。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル幅が狭い場合においても、eWFが十分に低減された閾値電圧が低い半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板11と、半導体基板11の上に形成され、第1の元素と第2の元素とを含むゲート絶縁膜26と、ゲート絶縁膜26の上に形成されたゲート電極27とを備えている。ゲート絶縁膜26は、半導体基板11側においてゲート電極27側と比べて第1の元素の含有量が多く、ゲート電極27側において半導体基板11側と比べて第2の元素の含有量が多い。

(もっと読む)

半導体装置およびその製造方法

【課題】耐圧を向上できる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板11上の素子領域に設けられるゲート絶縁膜13と、ゲート絶縁膜上に設けられるゲート電極14と、ゲート電極を挟むように半導体基板中に隔離して設けられるソースSまたはドレインDと、半導体基板中に形成される素子分離溝35中の底部および所定の深さDpの側面部にわたって設けられるp型絶縁層15−1と、絶縁層15−1と共に素子分離溝の底部および所定の深さDpの側面部を挟むように半導体基板中に設けられ、素子分離溝の側壁方向に沿ってソースまたはドレインと所定の距離(dS,dD)をもってオフセットするp型不純物拡散層15−2と、絶縁層上おける素子分離溝中の所定の深さDpに設けられる第1素子分離絶縁膜12−1と、第1素子分離絶縁膜上に設けられる第2素子分離絶縁膜12−2とを具備する。

(もっと読む)

半導体装置及びその製造方法

【課題】バルク基板を用いてもショートチャネル効果の抑制を効果的に発揮することができるFinFET構造を有する半導体装置及びその製造方法を得る。

【解決手段】Si基板1上にSiCエピタキシャル層2が形成され、SiCエピタキシャル層2の突出部2t上にSiエピタキシャル層3が形成される。突出部2t及びSiエピタキシャル層3は共に第1の方向に延びて、一方向延在形状を呈している。Siエピタキシャル層3の上面上及び両側面上には酸化膜8,窒化膜9及びゲート酸化膜20が形成される。酸化膜8,窒化膜9及びゲート酸化膜20を介して、Siエピタキシャル層3の上面上及び側面上にゲート電極G2が形成される。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】NMOSFET及びPMOSFET等のNMOS及びPMOSを有する半導体装置において、ゲート電極の実効仕事関数を、Siバンドギャップのmid-gap付近の値に安定的に設定することが可能な半導体装置及びその製造方法を提供する。

【解決手段】素子分離膜によって分離されてなる、p型拡散層及びn型拡散層を有する半導体基板と、前記半導体基板の、前記p型拡散層及びn型拡散層それぞれの上に形成されてなるゲート絶縁膜と、前記ゲート絶縁膜上に形成された金属膜を含むゲート電極と、前記ゲート絶縁膜と前記金属膜との界面に形成されたGe介在物と、前記金属膜上に形成されたシリコン含有層と、を具えるようにして半導体装置を構成する。

(もっと読む)

半導体装置

【課題】動作特性の劣化を抑えつつ、それぞれ適切な閾値電圧を設定された、メタルゲート電極を用いたn型およびp型のMISFETを混載する半導体装置を提供する。

【解決手段】半導体基板上に第1のゲート絶縁膜を介して形成された、第1の金属層および前記第1の金属層上の第1の導電層を含む第1のゲート電極を含むn型トランジスタと、半導体基板上に第2のゲート絶縁膜を介して形成された、前記第1の金属層よりも厚さが厚く、前記第1の金属層と構成元素の同一な材料からなる第2の金属層、および前記第2の金属層上の第2の導電層を含む第2のゲート電極を含むp型トランジスタと、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】オフセットスペーサが除去されることを防止する。

【解決手段】第1導電型の半導体領域10x上に形成されたゲート絶縁膜13Aと、ゲート絶縁膜上に形成されたゲート電極15Aと、ゲート電極の側面上に形成されたオフセットスペーサ17Aと、ゲート電極の側面上にオフセットスペーサを介して形成された断面形状がL字状の内側サイドウォール19と、ゲート電極15A、オフセットスペーサ17A、内側サイドウォール19、及び半導体領域10xにおける内側サイドウォール19の外側方に位置する領域を覆うように形成された絶縁膜24とを備え、オフセットスペーサ17Aは、ゲート電極の側面上に形成された内側オフセットスペーサ16と、ゲート電極の側面上に内側オフセットスペーサ16を覆うように形成された外側オフセットスペーサ17とを有し、外側オフセットスペーサは、内側オフセットスペーサの上端及び外側面に接して形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】高誘電率膜をゲート絶縁膜として用いたCISトランジスタの信頼性を向上する。

【解決手段】基板1の主面には、素子分離領域2によって互いに絶縁分離されたpMISトランジスタの活性領域およびnMISトランジスタの活性領域が設けられている。素子分離領域2に係るようにnMISトランジスタの活性領域上にnMISトランジスタのゲート絶縁膜を構成するハフニウム系酸化膜5が設けられており、そのハフニウム系酸化膜5と素子分離領域2上で接触し、pMISトランジスタの活性領域上にハフニウム系酸化膜5と異なる材料から構成されるpMISトランジスタのゲート絶縁膜を構成するハフニウム系酸化膜9が設けられている。

(もっと読む)

分離溝ライナを有する半導体デバイス、及び関連する製造方法

【解決手段】

半導体デバイス(300)を製造する方法がここに提供され、結果として得られる半導体デバイス(300)においては幅効果が低減されている。方法は、半導体材質(202)を有する基板(200)を提供することと、半導体材質(202)内に分離溝(212)を形成することと、その上への高k材質の形成を実質的に阻止するライナ材質(214)で分離溝(212)をライニングすることとを含む。内側を覆われた溝(216)は次いで絶縁材質(218)で充填される。その後、絶縁材質(218)の少なくとも一部分を覆い且つ半導体材質(202)の少なくとも一部分を覆うように高kゲート材質(232)の層が形成される。ライナ材質(214)は高kゲート材質(232)の層を分割し、それにより半導体材質(202)の能動領域上での酸素の泳動が防止される。

(もっと読む)

半導体装置の製造方法

【課題】急峻な不純物濃度のプロファイルを有するソース領域およびドレイン領域を形成することのできる半導体装置の製造方法を提供する。

【解決手段】この半導体装置の製造方法は、半導体基板の表面近傍に不純物を注入して不純物注入領域を形成する工程と、前記半導体基板にエッチングを施すことにより前記不純物注入領域の底部よりも深い溝を形成し、前記不純物注入領域を分断してソース領域およびドレイン領域を形成する工程と、前記溝の内部にSi系単結晶をエピタキシャル成長させてエピタキシャル結晶層を形成する工程と、前記エピタキシャル結晶層の上部にゲート絶縁膜およびゲート電極を形成する工程と、を含む。

(もっと読む)

半導体加工方法

【課題】高誘電率絶縁膜上に金属膜及び多結晶Siを堆積した構造の半導体を垂直にかつ微細に加工する。

【解決手段】半導体基板上に形成されたHfあるいはZrを含む絶縁膜102、該絶縁膜上に並置して形成された互いに仕事関数が異なる第1および第2の金属膜103,104、該第1および第2の金属膜上に堆積して形成した多結晶シリコン膜105を有し、該多結晶シリコン膜上に形成したレジスト108を用いて、プラズマ雰囲気中で前記多結晶シリコン膜並びに前記第1および第2の金属膜をエッチング加工する半導体加工方法において、前記前記複数種の金属膜上の多結晶シリコン膜のうちエッチング終了が早い方である第2の金属膜上の多結晶シリコン膜のエッチング終了後は、前記処理ガスとして、HBrおよび酸素を含むガスを用いる。

(もっと読む)

デュアル金属ゲートのコーナー部

【課題】 デュアル金属ゲートのコーナー部を有する改良された電界効果トランジスタを提供する。

【解決手段】 上記を鑑みて、改善された電界効果トランジスタ(FET)構造体、及び該構造体を形成する方法の実施形態が開示される。このFET構造体の実施形態の各々は、固有のゲート構造体を組み込む。具体的には、このゲート構造体は、FETチャネル領域の中央部分の上方の第1のセクションと、チャネル幅のエッジの上方(すなわち、チャネル領域と隣接する分離領域との間の界面の上方)の第2のセクションとを有する。第1のセクション及び第2のセクションは、これらが異なる有効仕事関数(すなわち、それぞれ第1の有効仕事関数及び第2の有効仕事関数)を有する点で異なる(すなわち、これらは、異なるゲート誘電体層及び/又は異なるゲート導体層を有する)。チャネル幅のエッジにおける閾値電圧が上昇することを確実にするように、異なる有効仕事関数が選択される。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】ゲート絶縁膜に高誘電率膜を用いたMISトランジスタのトランジスタ特性を向上する。

【解決手段】基板の主面上に形成した酸化シリコン(SiO2)膜上に、ハフニウムおよび酸素を含むベース絶縁膜を形成する。次いで、ベース絶縁膜上に、ベース絶縁膜より薄く、かつ、金属元素のみからなる金属薄膜を形成し、その金属薄膜上に、耐湿性および耐酸化性を有する保護膜を形成する。その後、保護膜を有する状態で、ベース絶縁膜に金属薄膜の金属元素をすべて拡散することによって、酸化シリコン膜上に、酸化シリコン膜より厚く、かつ、酸化シリコンより誘電率が高く、ベース絶縁膜のハフニウムおよび酸素と、金属薄膜の金属元素とを含む混合膜(高誘電率膜)を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】互いに異なる金属膜厚からなるゲート電極を有するn型及びp型MISトランジスタを備えた半導体装置において、ゲートリークによる劣化を抑制する。

【解決手段】半導体装置は、第1のMISトランジスタと第2のMISトランジスタとを備える。第1のMISトランジスタは、第1の活性領域12a上に形成された第1のゲート絶縁膜13aと、第1のゲート絶縁膜13a上に形成された第1の金属膜14a、及び、第1の金属膜14a上に形成された第1のシリコン膜17aを含む第1のゲート電極24Aとを備える。第2のMISトランジスタは、第2の活性領域12b上に形成された第2のゲート絶縁膜13bと、第2のゲート絶縁膜上に形成された第1の金属膜14b、第1の金属膜14b上に形成された第2の金属膜15b、及び、第2の金属膜15bの上に形成された第2のシリコン膜17bを含む第2のゲート電極24Bとを備えている。

(もっと読む)

181 - 200 / 411

[ Back to top ]