Fターム[5F140BF14]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 2層目材料 (3,048) | 半導体 (411)

Fターム[5F140BF14]に分類される特許

261 - 280 / 411

半導体装置およびキャパシタの製造方法、成膜装置

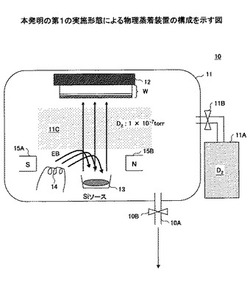

【課題】MOSトランジスタあるいはMIMキャパシタにおいて、導体膜からなる電極に、多量の重水素をドープすることにより、絶縁膜との界面の欠陥を終端し特性劣化を抑制する。

【解決手段】電子ビームEBによりシリコンソース13を加熱し、重水素ガス雰囲気中11Cにシリコン原子を放出することにより、シリコン膜を基板W上に堆積する。このシリコン膜はCVD法による堆積よりも高濃度に重水素ドープされ、ダングリングボンドなどの欠陥が重水素で終端されている。

(もっと読む)

半導体装置の製造方法

【課題】応力源となるSiGe混晶層のエピタキシャル成長の際に生じる、ポリシリコンゲート電極パターン上のSiGe混晶異常成長を抑制する半導体装置製造方法の提供。

【解決手段】pチャネルMOSトランジスタの製造方法は、(A)シリコン単結晶基板表面に、ゲート絶縁膜22A,22Bを介してポリシリコンゲート電極23A,23Bを、上面に絶縁膜が形成された状態で形成する工程と、(B)ゲート電極の合対向する側壁面に、側壁絶縁膜を形成する工程と、(C)基板表面を、各側壁面外側においてエッチングし、溝部を形成する工程と、(D)溝部にそれぞれSiGe領域を、基板に対してエピタキシャルに成長させる工程と、を含み、さらに工程(B)の後で工程(D)の前に、ポリシリコンゲート電極に不純物元素をイオン注入法により導入し、ポリシリコンゲート電極の少なくとも上部をアモルファス状態に変化させる工程(E)を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】ホウ素(B)のゲート絶縁膜の突き抜けや金属シリサイド膜による不純物の吸収によって生じるポリシリコン膜中の不純物の空乏化を防止する。

【解決手段】半導体装置100は、ゲート絶縁膜13と、ゲート絶縁膜13上に形成されたゲート電極14とを備える。ゲート電極14は、ドープドポリシリコン膜21a、21b、21cと、金属シリサイド膜22aとを備えている。ドープドポリシリコン膜21a、21cは、第1の不純物を含んでおり、ドープドポリシリコン膜21bは、反対の導電型を有する第2の不純物を含んでいる。これにより、ポリシリコン中の不純物の拡散工程やその後の熱負荷工程において、第2のドープドポリシリコン膜中の不純物の過度な拡散が抑制され、金属シリサイド膜が不純物を吸収することによるポリシリコン膜中の不純物の空乏化が防止される。

(もっと読む)

半導体装置

【課題】ゲート電極と高誘電率ゲート絶縁膜の間に生じる反応を抑制でき、高集積化および高速化に適した素子構造を有する半導体装置を提供する。

【解決手段】絶縁ゲート電界効果トランジスタを有する半導体装置であって、この絶縁ゲート電界効果トランジスタは、高誘電率膜を含むゲート絶縁膜と、第1の導電層およびこの第1の導電層より抵抗率の低い第2の導電層を含む積層構造をもつゲート電極を有し、第1の導電層は、前記高誘電率膜上に接して設けられ、密度5g/cm3以上の窒化チタンからなる半導体装置。

(もっと読む)

ピン電界効果トランジスタ及びその製造方法

【課題】ピン電界効果トランジスタ及びその製造方法を提供する。

【解決手段】ピン電界効果トランジスタは、基板100上に具備されるアクティブピン102と、アクティブピン102の表面に具備されるゲート酸化膜パターン104と、ゲート酸化膜パターン104上に具備され、アクティブピン102と交差するように延長される第1電極パターン106bと、第1電極パターン106b上に積層され、第1電極パターン106bに対して広い線幅を有する第2電極パターン108a及び第1電極パターン106b両側のアクティブピン102表面下に具備されるソース/ドレイン拡張領域110を含む。このようなピン電界効果トランジスタは、優れた性能を有するのみならず、GIDL電流が減少される。

(もっと読む)

MOSトランジスタの製造方法、および、これにより製造されたMOSトランジスタ

【課題】MOSトランジスタの製造方法、およびこれにより製造されたMOSトランジスタを提供する。

【解決手段】半導体基板100上にゲートパターン120を形成する工程と、前記ゲートパターンの側壁を覆うスペーサ134を形成する工程と、を含み、前記ゲートパターンを形成する工程は、順に積層されるゲート電極112a、キャッピング膜パターン118、を備えるように形成し、前記キャッピング膜パターンは、順に積層される下部キャッピング膜パターン114b、上部キャッピング膜パターン116a、を備えるように形成し、前記下部キャッピング膜パターンは前記上部キャッピング膜パターンよりも小さい幅を有するように形成する、ことを含む。

(もっと読む)

半導体装置

【課題】 ゲート電極上のシリサイド膜の断線を抑制する。

【解決手段】 ソース・ドレイン領域をデュアルシリサイド構造とし、ゲート電極の仕事関数はn型MISトランジスタ、p型MISトランジスタそれぞれの有するメタルゲート電極により定める構造とし、且つ、メタルゲート電極上の多結晶シリコン層は共通のn+ドーピング層とし、ゲート上シリサイド膜はn型領域に対しショットキー障壁が低くなる材料で形成する。

(もっと読む)

半導体装置、およびその製造方法

【課題】表面にエクステンション層を形成したフィンを有し、十分に寄生抵抗を低減することのできる半導体装置、およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体基板と、前記半導体基板上に形成されたフィンと、ゲート絶縁膜を介して前記フィンの両側面を挟むように形成されたゲート電極と、前記ゲート電極の両側の前記フィンの側面に形成され、前記半導体基板の表面と鋭角に対向する面を有するエクステンション層と、前記半導体基板の表面と鋭角に対向する前記面の表面に形成されたシリサイド層と、を有する。

(もっと読む)

金属ゲート及び高K誘電体を有する回路構造体

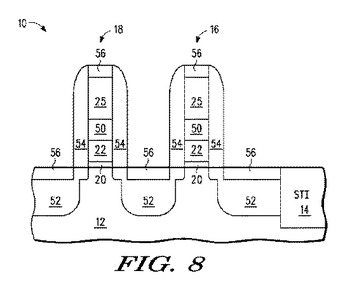

【課題】 高k材料含有ゲート誘電体及び金属含有ゲートを有する回路構造体を提供する。

【解決手段】 高k誘電体のゲート絶縁体及び金属含有ゲートを有するPFETデバイス及びNFETデバイスを備えたFETデバイス構造体が、開示される。両方のNFETデバイス及びPFETデバイスにおけるゲート金属層が、単一の共通の金属層から製造された。単一の共通の金属であるために、デバイスの製造が簡単化され、必要とされるマスクの数が減少する。両方の型のデバイスのゲートのために単一の金属層を用いるさらなる結果として、PFET及びNFETの端子電極を、直接物理的に接触した状態で互いに付き合わせることができる。共通の金属材料を選択すること及び高k誘電体の酸素曝露によって、デバイスの閾値電圧が調整される。閾値は、低消費電力のデバイス動作を目的としている。

(もっと読む)

半導体装置およびその製造方法

【課題】素子分離領域にSOG(spin on glass)膜を用いる構成で、LDD(lightly doped drain)構造を採用するトランジスタを形成する場合に、活性領域に転位が形成されて接合リーク特性が悪化するのを抑制することができる構成の半導体装置及びその製造方法を提供する。

【解決手段】シリコン基板1にトレンチ4を形成してSOG膜6を埋め込む構成で、LDD構造形成のための高濃度不純物領域1bを形成するためのイオン注入をしてから、SOG膜6をそれよりも深くなるように落とし込む。その後、熱処理を行なって注入したイオンを活性化する。SOG膜6による引張応力がイオン注入した活性領域2に作用して転位が発生するのを抑制する。

(もっと読む)

半導体装置の製造方法

【課題】MOS構造の半導体装置において、ゲート電極をイオン注入のチャネリングに対して強い構造とする。

【解決手段】半導体基板上でゲート絶縁膜の上に半導体材料を堆積してゲート電極を形成する。このゲート電極の表面または内部に非晶質層を形成する。その後、ゲートサイドウォールを形成し、ゲート電極およびサイドウォールをマスクとして半導体基板に不純物をイオン注入し、ソース/ドレインを形成する。非晶質層としては、窒素を1×1020〜1×1022/cm3個含む層を形成する。これを、熱処理に対する不純物析出抑制層とし、イオン注入に対するチャネリング防止層とする。

(もっと読む)

半導体装置の製造方法

【課題】トリミングを用いず、プロセスの大幅な変更や工程数を大きく増加させずに、高精度に微細化してゲート電極または配線を形成できる半導体装置の製造方法を提供する。

【解決手段】チャネル形成領域を有する半導体基板10のチャネル形成領域上にゲート絶縁膜12を形成し、その上層に第1導電層20を形成し、第1導電層にゲート電極のパターンに対応し第1の幅20wを有する第1凹部20tを形成し、その内壁を被覆して、第1の幅より狭い第2の幅31wの第2凹部31tを有する第2導電層31を形成し、第2凹部を埋め込んでマスク層32を形成し、第1凹部の外部における第2導電層及びマスク層を除去し、第1凹部に残されたマスク層をマスクとして第2導電層及び第1導電層をパターン加工してゲート電極Gを形成し、ゲート電極Gの両側部における半導体基板中にソース・ドレイン領域13を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】nチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタを有する半導体装置において、nチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタ共にドレイン電流特性に優れた半導体装置を実現する。

【解決手段】nチャネル型電界効果トランジスタ10と、pチャネル型電界効果トランジスタ30とを有する半導体装置において、nチャネル型電界効果トランジスタ10のゲート電極15を覆う応力制御膜19には、膜応力が引張応力側の膜を用いる。pチャネル型電界効果トランジスタ30のゲート電極35を覆う応力制御膜39には、膜応力が、nチャネル型トランジスタ10の応力制御膜19より、圧縮応力側の膜を用いることにより、nチャネル型、pチャネル型トランジスタの両方のドレイン電流の向上が期待できる。このため、全体としての特性を向上させることができる。

(もっと読む)

ハフニウム酸化物に基づく薄膜部分を備えた集積電子回路

本発明は、ハフニウム酸化物に基づく薄膜(1)を含む集積電子回路に関連している。本発明によれば、前記部分は同様に、ハフニウムとマグネシウムの混合酸化物の形態においてマグネシウム原子を含有している。一つのそのような部分は高い誘電率、及び非常に低い漏れ電流を有している。本発明は特に、MOSトランジスタのゲート絶縁膜の部分、またはMIMキャパシタ誘電体の部分の形成に適している。  (もっと読む)

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】不純物を混ぜなくても立方晶(cubic)、正方晶(tetragonal)又は斜方晶(orthorhombic)のハフニウム酸化物を形成することができる半導体装置の製造方法及び半導体装置を提供する。

【解決手段】シリコン基板1上にHfO2膜3を形成する工程と、HfO2膜3上にゲート電極膜5を形成する工程と、HfO2膜3及びゲート電極膜5が形成されたシリコン基板1に熱処理を施して、HfO2膜3を結晶化する工程と、を含む。熱処理温度は例えば800℃である。

(もっと読む)

半導体装置およびその製造方法

【課題】対称フラットバンド電圧、同一ゲート電極材料かつ高誘電率誘電体層を有するCMISFETを提供する。

【解決手段】nMISFETは、半導体基板10の表面上に配置された第1ゲート絶縁膜16と、第1ゲート絶縁膜16上に配置されたM1xM2yO(M1=Y,La,Ce,Pr,Nd,Sm,Gd,Tb,Dy,Ho,Er,Tm,YbまたはLu,M2=Hf,Zr,Ta,x/(x+y)>0.12)で表される組成比を有する第1金属酸化物層20と、第2金属酸化物層24と、第2金属酸化物層24上に配置された第1導電層28とを備え、pMISFETは、半導体基板10表面上に配置された第2ゲート絶縁膜18と、第2ゲート絶縁膜18上に配置されたM3zM4wO(M3=Al,M4=Hf,Zr,Ta,z/(z+w)>0.14)で表される組成比を有する第3金属酸化物層22と、第4金属酸化物層26と、第4金属酸化物層26上に配置された第2導電層30とを備える半導体装置およびその製法。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】短チャネル特性を劣化させること無しに、トランジスタの閾値電圧を低下させることができる半導体装置の製造方法を提供する。

【解決手段】NMOS領域(またはPMOS領域)の半導体基板101に対して、窒素(またはハロゲン元素)を導入する。その後、熱処理を施すことにより、NMOS領域(またはPMOS領域)の半導体基板101上にゲート絶縁膜107N,107Pを形成する。

(もっと読む)

電界効果型トランジスタの修復方法、半導体装置の修復方法、半導体装置の作製方法、及び半導体装置

【課題】電界効果型トランジスタのリーク電流を低減し、寿命の向上を図るための簡便な修復方法を提供することを課題とする。また、作製コストの増加を抑え、消費電力が小さく、且つ信頼性の高い半導体装置を提供することを課題とする。

【解決手段】ソース電極又はドレイン電極の一方と、ゲート電極との間に、電気的な衝撃を加える。または、ソース電極又はドレイン電極の一方と、ソース電極又はドレイン電極の他方との間に、電気的な衝撃を加える。これにより、リークパスを絶縁化し、リーク電流を低減することができる。なお、上記の電気的な衝撃は、静電気等の電気パルスであっても良いし、直流電圧、交流電圧、直流電流、交流電流等であっても良い。

(もっと読む)

ゲート・ストレッサ及び半導体デバイスを特徴とする半導体デバイスの製造方法

半導体デバイス(10)は半導体層(12)に形成される。ゲート・スタック(16,18)は、半導体層の上にわたって形成され、第1の伝導層(22)及び、第1の層の上の第2層(24)を有する。第1の層は、より伝導性であり、第2の層よりインプラントに対して停止力を提供する。種(46)が、第2の層内にインプラントされる。ソース/ドレイン領域(52)は、ゲート・スタックの対抗する側の半導体層に形成される。ゲート・スタックの下の領域の半導体層にゲート・スタックが応力を働かせるインプラントのステップの後、ゲート・スタックは加熱される。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】P型MOSトランジスタにおいて優れたNBTI信頼性が得られ、また、簡易な工程で製造することができる半導体装置及びその製造方法を提供することを目的とする。

【解決手段】N型MOSトランジスタ4aとP型MOSトランジスタ4bを有する半導体装置において、P型MOSトランジスタ4bのゲート電極6bを、P型ドーパントを含有するポリシリコンを主材料とし、少なくともゲート絶縁膜5との界面近傍にN型ドーパントを含有するように構成する。このような半導体装置は、ゲート絶縁膜5が形成されたNMOSトランジスタ形成領域2a及びP型MOSトランジスタ形成領域2bに、ゲート電極となるポリシリコン層を、N型ドーパントを含有する第1ポリシリコン層とドーパントを実質的に含まない第2ポリシリコン層のスタック構造で形成し、各領域に、それぞれ、N型ドーパント、P型ドーパントをイオン注入する工程を用いて製造できる。

(もっと読む)

261 - 280 / 411

[ Back to top ]