Fターム[5F140BF14]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 2層目材料 (3,048) | 半導体 (411)

Fターム[5F140BF14]に分類される特許

401 - 411 / 411

半導体装置

【課題】 酸化膜と窒化膜の多層膜よりなるサイドウォールを有する半導体装置において、サイドウォールを構成する酸化膜がコンタクトエッチングの際にエッチングされてゲート電極の側面が露出するのを防ぐことができる半導体装置を得る。

【解決手段】 半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、ゲート電極上に形成された第1の窒化膜と、ゲート電極及び第1の窒化膜の側面に順番に形成された第1の酸化膜、第2の窒化膜、第2の酸化膜及び第3の窒化膜からなるサイドウォールとを有し、第1の窒化膜は、上部の外径が下部の外径よりも小さく、第1の酸化膜のゲート電極の側面にある部分は、上面から見て第2の窒化膜で覆われ、第2の酸化膜のゲート電極の側面にある部分は、上面から見て第3の窒化膜で覆われている。

(もっと読む)

高誘電率のゲート絶縁膜を有する半導体装置及びそれの製造方法

【課題】 本発明はゲート構造物として高誘電率を有する物質として、高誘電率を有する物質からなるゲート絶縁膜を含む半導体装置及びその製造方法に関する。

【解決手段】 半導体装置及びその製造方法において、基板上に形成され、ハフニウムシリコン酸化物含有固体物質を含むゲート絶縁膜パターンと前記ゲート絶縁膜パターン上に形成される第1ゲート導電膜パターンを含むゲート構造物及び前記ゲート構造物と隣接する基板の表面部位に配置されており、n型不純物がドーピングされたソース/ドレイン領域を含むことを特徴とする。

(もっと読む)

High−k誘電材料をエッチングするための方法及びシステム

【課題】high−k(高誘電率)誘電材料をエッチングするための方法及びシステム

【解決手段】本発明のある実施形態では、エッチ反応剤が、high−k層と反応したときに揮発性エッチ製品を形成するために利用される。代わりに、high−k層はパターン化されたフォトレジストまたはハードマスクに従って異方エッチングすることができ、中性原子のハイパーサーマルビームがhigh−k層とのエッチ反応剤の反応を助けるために使用される。代わりに、中性原子のハイパーサーマルビームまたはプラズマ処理はhigh−k層を修正し、その後、該修正されたhigh−k層と反応するエッチ反応剤を活用して該修正されたhigh−k層をエッチングするために使用することができる。

(もっと読む)

ニッケルゲルマノシリサイド化したゲートを組み込んだMOSFETおよびこれらのMOSFETを形成する方法

MOSFETのゲートまたはMOSFETのソースまたはドレイン領域は、シリコンゲルマニウムまたは多結晶シリコンゲルマニウムを含む。好ましくはニッケルシリサイドのモノシリサイドフェーズを含むニッケルゲルマノシリサイド(62、64)を形成すべく、ニッケルでのシリサイデーションを実行する。

ニッケルモノシリサイドによって呈される優れたシート抵抗を実質的に保持する一方、シリサイド中にゲルマニウムを含むことは、モノシリサイドフェーズが形成され得るより温度領域をより広くする。その結果、ニッケルゲルマノシリサイドは、後続のプロセスの間、ニッケルモノシリサイドよりも、より高い温度に耐えることができる。しかしながら、ニッケルモノシリサイドとほぼ同一のシート抵抗および他の有益な特性を提供する。  (もっと読む)

(もっと読む)

金属ゲート集積化のためのゲートスタック及びゲートスタックのエッチングシーケンス

【課題】本発明は半導体デバイス(205)における金属ゲートスタック(200)を製作するためのプロセスを提供する。

【解決手段】本願の方法は、半導体基板(220)上に位置するゲート誘電体層(215)の上に金属層(210)を堆積させる段階を含む。本方法は、金属層(210)上にポリシリコン層(225)を形成する段階と、そのポリシリコン層(225)上に保護層(230)を生成する段階とを更に含む。本方法はは、また、保護層(230)上に無機反射防止被覆(235)を配置する段階を含む。他の実施形態では、金属ゲートスタックの前駆構造体及び集積回路の製造方法を含む。

(もっと読む)

選択的堆積プロセスを使用したMOSFETデバイスの作製方法

本発明の実施形態により、高ドーパント濃度を含有するエピタキシャルシリコンゲルマニウム材料を選択的に堆積するなど、シリコン含有材料を堆積するためのプロセスが提供される。一実施例において、1つの層を別の層の上部に堆積するために、少なくとも2つの異なるプロセスガスに基板が曝される。1つのプロセスガスは、ジクロロシラン、ゲルマニウム源、およびエッチャントを含有し、次のプロセスガスは、シランおよびエッチャントを含有する。他の実施例において、プロセスガスが、ジクロロシラン、メチルシラン、および塩化水素、またはシラン、メチルシラン、および塩化水素を含有する。一態様において、堆積された層が、結晶格子内に格子間部位を有し、格子間部位内に約3at%以下の炭素を含有し、引き続き、結晶格子の置換部位内に炭素を包含するようにアニーリングされる。別の態様において、シリコンゲルマニウム積層体が、約25at%以下、約25at%以上、および約5at%以下のゲルマニウム濃度を含有する第1、第2、および第3の層を有する。 (もっと読む)

ゲート電極構造のトリミングを制御する方法

ゲート電極構造の第1寸法の決定によりゲート電極構造のトリミングをコントロールする方法および処理ツールであって、目標トリム寸法を選択し、プロセスパラメータのセットを生成するためにプロセスモデルに対して第1寸法および目標トリム寸法をフィードフォワードし、ゲート電極構造上にトリミングプロセスを実行する。トリミングプロセスを実行する際には、プロセスパラメータをコントロールし、ゲート電極構造をトリミングし、ゲート電極構造のトリム後の寸法を計測する。目標トリム寸法が得られるまで、トリミングプロセスは少なくとも1回は繰り返し行われる。トリム後寸法は、新たなプロセスパラメータのセットを生成するために、フィードバックされる。  (もっと読む)

(もっと読む)

切り欠き制御電極及び当該電極の構造を有する半導体素子の製造方法

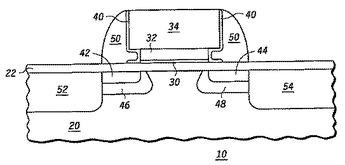

半導体素子(10)を形成する方法では、一の表面を有する基板(20)を設け、絶縁層(22)を基板(20)の表面の上に形成し、第1パターニング済み導電層(30)を絶縁層(22)の上に形成し、第2パターニング済み導電層(32)を第1パターニング済み導電層(30)の上に形成し、パターニング済み非絶縁層(34)を第2パターニング済み導電層(32)の上に形成し、そして第1及び第2パターニング済み導電層(30,32)の一部分を選択的に除去して、半導体素子(10)の切り欠き制御電極を形成する。  (もっと読む)

(もっと読む)

高誘電率集積用のシリコンゲルマニウム表面層

高誘電率層(180)を半導体装置中に集積するためにシリコンゲルマニウム(SiGe)表面層(160)を使用する方法である。この方法は、基板(150)上にSiGe表面層(160)を形成し、前記SiGe表面層(160)上に高誘電率層(180)を堆積する。酸化層(170)は、前記高誘電率層(180)とSiGe表面層(160)の未反応部位との間に位置し、前記高誘電率層(180)の堆積中とその後のアニーリング処理中とのいずれか、又はいずれもの間に形成される。前記方法は、前記高誘電率層(180)上に電極層(190)を形成する。  (もっと読む)

(もっと読む)

ゲート電極をトリミングする方法

第1寸法を有するゲート電極層を備えたゲート電極構造をトリミングする方法および処理ツールを提供する。反応層は、ゲート電極構造と反応することによって形成される。そして、この反応層は、化学エッチングによって、ゲート電極構造の未反応部分から選択的に除去される。これにより、第1寸法よりも小さい第2寸法を有するトリミングされたゲート電極構造が形成される。トリミング処理は、反応層の形成が実質的に自己制限的となるプロセス条件にて実行される。トリミング処理は、ゲート電極構造の寸法をさらに減少させるために繰り返し行うことができる。  (もっと読む)

(もっと読む)

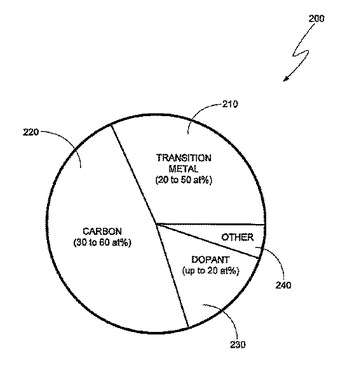

ゲート電極として使用される遷移金属合金およびこれらの合金を取り入れた装置

高温で顕著に変化しないn型またはp型の仕事関数を有する遷移金属合金の実施例を示した。示された遷移金属合金は、トランジスタのゲート電極として使用しても良く、ゲート電極の一部を構成しても良い。これらの遷移金属合金を用いて、ゲート電極を形成する方法についても示した。  (もっと読む)

(もっと読む)

401 - 411 / 411

[ Back to top ]