Fターム[5F140BF46]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 形状、配置 (2,388) | 直列複数ゲート (66)

Fターム[5F140BF46]に分類される特許

1 - 20 / 66

半導体装置

【課題】ノーマリオフで動作するとともに、高い耐圧と低いオン抵抗を具備した半導体装置を提供すること。

【解決手段】 半導体装置1では、ドレイン電極21が第1ヘテロ接合面32に形成される2次元電子ガス層に対して電気的に接続可能に構成されており、ソース電極29が第1ヘテロ接合面32に形成される2次元電子ガス層から電気的に絶縁可能に構成されているとともに第2ヘテロ接合面34に形成される2次元電子ガス層に対して電気的に接続可能に構成されており、ゲート部28が第2ヘテロ接合面34に対向しており、導通電極25が第1ヘテロ接合面32及び第2ヘテロ接合面34に形成される2次元電子ガス層の双方に対して電気的に接続可能に構成されている。第1ヘテロ接合面32に形成される2次元電子ガス層の電子濃度は、第2ヘテロ接合面34に形成される2次元電子ガス層の電子濃度よりも濃い。

(もっと読む)

半導体装置およびその製造方法

【課題】仕事関数の異なる複数の電極層を有し、ゲート抵抗が低く、作製が容易なゲート電極を備える半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、基板と、前記基板上に形成されたゲート絶縁膜とを備える。さらに、前記装置は、前記ゲート絶縁膜の上面に形成され、第1の仕事関数を有する第1の電極層と、前記ゲート絶縁膜の上面と前記第1の電極層の上面に連続して形成され、前記第1の仕事関数と異なる第2の仕事関数を有する第2の電極層と、を有するゲート電極と、前記ゲート電極の側面に形成された側壁絶縁膜とを備える。さらに、前記装置では、前記第1の電極層の上面の高さは、前記側壁絶縁膜の上面の高さよりも低い。

(もっと読む)

窒化物系半導体装置

【課題】ダイオード部とトランジスタ部の面積比率を自由に設定することが可能な窒化物系半導体装置を提供することを目的とする。

【解決手段】第1HEMT部30及び第2HEMT部31から成るトランジスタ部1と、第1電極24と電気的に短絡された第1ショットキー電極28及び第1ゲート電極26と電気的に第2ショットキー電極29から成るダイオード部2と、を備えて構成されている。また、第1電極24と第2電極25との間の領域に第1電極24に沿って、第1ゲート電極26及び第1ショットキー電極28が交互に形成され、かつ、第2電極25に沿って、第2ゲート電極27及び第2ショットキー電極29が交互に形成されている。さらに、第1ゲート電極26と第2ゲート電極27とは、対向して形成されており、第1ショットキー電極28と第2ショットキー電極29とは対向して形成されている。

(もっと読む)

スイッチ装置

【課題】GaNトランジスタを理想的な還流ダイオードとして動作させ、低損失のスイッチ装置を実現できるようにする。

【解決手段】スイッチ装置は、窒化物半導体素子301と、窒化物半導体素子301を駆動する駆動部302とを備えている。窒化物半導体素子301は、第1のオーミック電極、第2のオーミック電極及び第1のゲート電極を有している。駆動部302は、第1のゲート電極にバイアス電圧を印加するゲート回路311と、第1のゲート電極と第1のオーミック電極との間に接続され、双方向に電流を流すスイッチ素子312とを有している。駆動部302は、第1のオーミック電極から第2のオーミック電極への電流を通電し且つ第2のオーミック電極から第1のオーミック電極への電流を遮断する動作を行う場合には、スイッチ素子312をオン状態とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】フィンがバルク半導体上に形成されている場合においても、電流駆動力増大を図りつつ、オフリーク電流を低減させる。

【解決手段】フィン型半導体層1の両側面には、チャネル領域7のポテンシャルを制御するゲート電極4が配置され、チャネル領域7には、フィン型半導体層1のソース層2側から根元BM側にかけてポテンシャルバリアPB1、PB2が形成されている。

(もっと読む)

半導体装置

【課題】トランジスタの電流駆動力増大を図りつつ、オフリーク電流を低減させる。

【解決手段】半導体突出部2は、半導体基板1上に形成されている。ソース/ドレイン層5、6は、半導体突出部2の上下方向に設けられている。ゲート電極7、8は、半導体突出部2の側面にゲート絶縁膜4を介して設けられている。チャネル領域3は、半導体突出部2の側面に設けられ、ドレイン層6側とソース層5側とでポテンシャルの高さが異なっている。

(もっと読む)

二重ゲート電極構造を含む半導体装置及びその製造方法

【課題】漏洩電流発生を最小化すると同時にオン電流(On current)を増加させ得る二重ゲート電極構造を含む半導体装置及びその製造方法が提供される。

【解決手段】本発明による半導体装置は、基板に配置されるゲート電極と、前記ゲート電極の両端に各々隣接するように前記基板に配置される第1不純物注入領域及び第2不純物注入領域と、前記第1不純物注入領域と前記第2不純物注入領域との間に配置されるチャンネル領域を含み、前記ゲート電極は前記第1不純物注入領域に隣接する第1サブゲート電極と前記第2不純物注入領域に隣接する第2サブゲート電極と、を含み、前記第1サブゲート電極と前記第2サブゲート電極とは前記チャンネル領域の上に配置される。この半導体装置では1つのチャンネル領域が2つのサブゲートによって独立的に制御されて漏洩電流発生を最小化できる。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】FETのソース領域にショットキー電極を形成し、内部にオミックパターン電極を備え、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成することによって、ノーマリ−オフ動作すると共に高耐圧及び高電流で動作可能な、半導体素子及び製造方法を提供する。

【解決手段】内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50と離間され、窒化物半導体層30にショットキー接合されるソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上及びソース電極60の少なくとも一部上にかけて形成された誘電層40と、ドレイン電極50と離間されるように誘電層40上に配設され、一部が誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上部に形成されたゲート電極70とを含む。

(もっと読む)

電子装置

【課題】 信頼性及び色再現性の高い電子装置を提供する。

【解決手段】 単結晶半導体基板11上にスイッチング用FET201及び電流制御用FET202を形成し、電流制御用FET202にEL素子203が電気的に接続された画素構造とする。電流制御用FET202は画素間での特性ばらつきが極めて小さく、色再現性の高い画像を得ることができる。電流制御用FET202にホットキャリア対策を施すことで信頼性の高い電子装置が得られる。

(もっと読む)

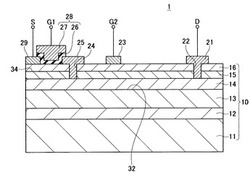

化合物半導体装置及びその製造方法

【課題】ピンチオフ特性を維持しながら動作効率を向上することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】基板11と、基板11上方に形成された電子走行層12と、電子走行層12上方に形成された電子供給層13と、電子供給層13上方に形成されたソース電極15s及びドレイン電極15dと、電子供給層13上方で、ソース電極15s及びドレイン電極15dの間に形成された第1のゲート電極15g−1及び第2のゲート電極15g−2と、が設けられている。ゲート電極15g−1の仕事関数は、第2のゲート電極15g−2の仕事関数よりも低い。

(もっと読む)

窒化物半導体装置

【課題】定電流動作が可能な窒化物半導体装置を提供する。

【解決手段】窒化物半導体を含む半導体層30と、ソース電極40と、ドレイ電極50と、第1ゲート電極10と、第2ゲート電極20と、を備えた窒化物半導体装置111が提供される。ソース電極40とドレイン電極50は、主面上に設けられ、半導体層とオーミック性接触を形成し、互いに離間する。第1ゲート電極10は、主面上においてソース電極40とドレイン電極50との間に設けられる。第2ゲート電極20は、主面上においてソース電極40と第1ゲート電極10との間に設けられる。ソース電極40と第1ゲート電極10との間の電位差が0ボルトのときに、半導体層30のうちの第1ゲート電極に対向する部分は導通する。第1ゲート電極10は、第2ゲート電極20に印加される電圧に応じた定電流をスイッチングする。

(もっと読む)

半導体装置

【課題】しきい値を電気的に調整可能な半導体装置を提供する。

【解決手段】半導体装置10では、チャネル領域14は対向する第1、第2の面14a、14bを有している。第1、第2不純物領域15、16が、チャネル領域14の両側に配設されている。第1ゲート電極18は、第1ゲート絶縁膜19を介して第1の面14aに、第1ゲート電圧Vg1が印加されると生じる第1反転層23の一側が第1不純物領域15に接触し、他側が第2不純物領域16から離間するように配設されている。第2ゲート電極20は、第2ゲート絶縁膜21を介して第2の面14bに、第2ゲート電圧Vg2が印加されると生じる第2反転層24の一側が第2不純物領域16に接触し、他側が第1不純物領域15から離間するように配設されている。第1、第2ゲート電圧Vg1、Vg2に応じて、第1、第2反転層23、24が接触し、第1、第2不純物領域15、16間が導通する。

(もっと読む)

MOSトランジスタおよびその製造方法

【課題】ドレイン端側においてゲート絶縁膜の膜厚を増大させる構成のMOSトランジスタにおいて、オン抵抗を低減し、耐圧を向上させる。

【解決手段】高電圧トランジスタ10のゲート電極構造をチャネル領域CHを第1の膜厚で覆う第1のゲート絶縁膜12G1と、第1の膜厚よりも大きい第2の膜厚で覆う第2のゲート絶縁膜12G2とし、第1のゲート絶縁膜12G1上の第1のゲート電極13G1と、第2のゲート絶縁膜12G2上の第2のゲート電極13G2の構成とする。更に、第1のゲート電極13G1と前記第2のゲート電極13G2とは、前記第1のゲート絶縁膜12G1から延在する絶縁膜12HKで隔てられる。

(もっと読む)

半導体装置及びその製造方法

【課題】構造が簡単なトランジスタにより、サステイン耐圧を改善し且つサステイン耐圧のばらつきの抑制及びトランジスタ形成後のドレイン抵抗及び接合プロファイルの調整が可能な、自由度が高い半導体装置を実現できるようにする。

【解決手段】半導体装置は、p型ウェル102に形成され、互いに並行に延びると共に、ゲート長方向の幅が比較的に大きい第1ゲート電極125と、ゲート長方向の幅が比較的に小さい第2ゲート電極126と、p型ウェル102における第1ゲート電極125及び第2ゲート電極126同士の間に形成されたLDD低濃度領域135と、該p型ウェル102における第1ゲート電極125及び第2ゲート電極126のそれぞれの外側に形成されたLDD中濃度領域134とを有している。LDD低濃度領域135の不純物濃度は、LDD中濃度領域134の不純物濃度よりも低い。

(もっと読む)

半導体装置およびその制御方法

【課題】リカバリ損失の低減が図れ、かつ、ノイズによるセルフターンオンが生じ難い構造の半導体装置を提供する。

【解決手段】ゲート電極8を深さの異なる第1、第2ゲート電極8a、8bを備えたダブルゲート構造とする。このような構造では、第1、第2ゲート電極8a、8bのうちの第1ゲート電極8aのみをオンさせることで、p型ベース領域3に対して反転層を形成しながらも、その反転層がn-型ドリフト層2とn+型不純物領域4とを繋ぐ深さまでは形成されないようにすることができる。この第1ゲート電極8aを過剰キャリア注入抑制ゲートとして機能させる。

(もっと読む)

高電圧動作電界効果トランジスタとそのバイアス回路およびその高電圧動作回路要素

【課題】 ICまたはLSIの標準電源電圧用のトランジスタ構成部分ないしはプロセス技術を活用して高電圧動作電界効果トランジスタを該IC中に作りこむ。

【解決手段】 電界効果トランジスタの動作電圧を大きくするために、ゲートにドレイン電位に応じて変化する電位分布を設ける手段をとる。

(もっと読む)

電界効果トランジスタの高電圧動作方法とそのバイアス回路

【課題】 ICないしLSIの標準電源電圧用のトランジスタ構成部分ないしはプロセス技術を活用して高電圧動作電界効果トランジスタを該ICないしLSI中に作りこむ。

【解決手段】 電界効果トランジスタの動作電圧を大きくするために、ゲートを分割してドレインにより近い分割ゲートへドレイン電位により近い電位でかつドレイン電位に応じて変化する電位を供給する手段をとる。

(もっと読む)

半導体装置およびその製造方法

【課題】トランジスタが設計より低い閾値電圧で動作し始めるという寄生トランジスタ動作を抑制する。

【解決手段】半導体装置100は、基板102の素子形成領域に形成されたトレンチ162、トレンチ162の側壁および底面に形成されたゲート絶縁膜120、トレンチ162を埋め込むようにゲート絶縁膜120上に形成されたゲート電極122、基板102表面のゲート長方向の一方の側に形成されたソース領域112、およびゲート長方向の他方の側に形成されたドレイン領域113、を有するトランジスタを含む。ここで、ゲート電極122は、トレンチ162外部の基板102上にも露出して形成され、ゲート電極122は、ゲート長方向における、トレンチ162の両端部上部が覆われるとともに、中央部に少なくとも一つ深さが基板まで達する凹部が形成されるように設けられている。

(もっと読む)

スイッチング素子、高周波信号スイッチ及び高周波信号増幅モジュール

【課題】高周波信号経路を切り替えるために半導体基板上に形成された、小型でかつ低歪特性を実現するスイッチング素子を提供する。

【解決手段】スイッチング素子の一例であるFET100は半導体基板109上に形成された櫛型の2つのソース・ドレイン電極101と、2つのソース・ドレイン電極101の間を這うように配置された少なくとも2本のゲート電極102と、隣り合うゲート電極102の間に挟まれ、かつ、隣り合うゲート電極102に沿って配置された導電層103とを備え、ゲート電極102の2つのソース・ドレイン電極101の指状部と平行な部分である直線部108の直下に位置する層が、ゲート電極102の隣り合う一対の直線部108をつなぐ部分である屈曲部107の直下に位置する層から、電気的に分離されている。

(もっと読む)

半導体装置

【課題】MISFETにおけるAvt(Vtばらつき)のゲート幅依存性を考慮し、Vtミスマッチ及びVtばらつきを低減できるようにする。

【解決手段】半導体装置は、それぞれが半導体基板に形成され、ソースドレインを構成する拡散層205及び該拡散層205の上に形成されたゲート203を有し、且つ互いに並列接続された複数の単位MISFETから構成される複数のMISFET201、202を含む。MISFET201、202同士の間の閾値電圧のばらつきの標準偏差は、各MISFETにおける単位MISFETのそれぞれのゲート長とゲート幅との積の総和であるチャネル面積と同一の面積を有する単一のMISFET同士の間の閾値電圧のばらつきの標準偏差よりも小さい。

(もっと読む)

1 - 20 / 66

[ Back to top ]