Fターム[5F140BG03]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ダミーゲートを用いたゲート電極の製造 (506) | ダミーゲート材料(レジスト、ポリイミド) (470) | 無機物 (413)

Fターム[5F140BG03]の下位に属するFターム

Fターム[5F140BG03]に分類される特許

21 - 40 / 112

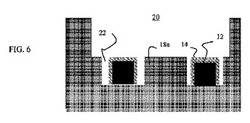

置換ゲート構造体を有するFET及びその製造方法

【課題】 マルチゲート型FETの置換ゲート構造体及びマルチゲート型FETの置換ゲート構造体の製造方法を提供する。

【解決手段】 MUGFET及びMUGFETを製造する方法が示される。MUGFETを製造する方法は、複数の活性領域の周りに一時的スペーサ・ゲート(図3の16)を形成することと、複数の活性領域の間を含む、一時的スペーサ・ゲートの上に誘電体材料(18a及び空間20内)を堆積させることとを含む。この方法は、誘電体材料(空間20内)の部分をエッチングして一時的スペーサ・ゲート(16)を露出させることと、一時的スペーサ・ゲートを除去して、活性領域と誘電体材料の残りの部分(18a)との間に空間を残すこととをさらに含む。この方法はさらに、活性領域と誘電体材料の残りの部分(18a)との間の空間(22)及び誘電体材料の残りの部分の上方をゲート材料で充填することを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極とコンタクト配線のショート不良を防止できる半導体装置の製造方法を提供する。

【解決手段】半導体基板32上にゲートハードマスク、ゲート電極34及びゲート絶縁膜33を形成する。ゲートハードマスクの線幅をゲート電極よりも狭くした後、S/Dエクステンション36を形成する。全面にシリコン酸化膜を堆積形成し、エッチバックしてゲート電極の側壁から上面の一部上に渡って連続的に残存させた絶縁部材37を形成する。ゲートハードマスクを除去した後、ゲート電極と絶縁部材をマスクにしてコンタクトジャンクション38を形成する。金属シリサイド膜を形成後、シリコン窒化膜40と層間絶縁膜41を順次堆積形成する。層間絶縁膜にコンタクトホールを形成し、続いてシリコン酸化膜との選択比が高い異方性エッチングによってシリコン窒化膜を除去することでコンタクトホールを開孔し、コンタクト配線43を形成する。

(もっと読む)

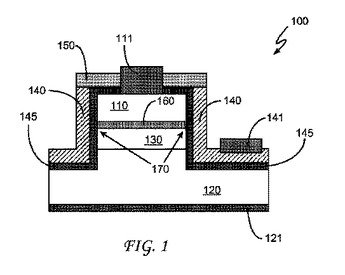

トンネル電界効果トランジスタ及びその製造方法

トンネル電界効果トランジスタ(TFET)は、ソース領域(110、210)、ドレイン領域(120、220)、ソース領域とドレイン領域との間のチャネル領域(130、230)、及びチャネル領域に隣接するゲート領域(140、240)を含む。ソース領域は、第1のIII族材料と第1のV族材料とを有する第1の化合物半導体を含み、チャネル領域は、第2のIII族材料と第2のV族材料とを有する第2の化合物半導体を含む。ドレイン領域は、第3のIII族材料と第3のV族材料とを有する第3の化合物半導体を含む。  (もっと読む)

(もっと読む)

可動ゲート型電界効果トランジスタの製造方法

【課題】ダメージを生じさせることなく、安価かつ短時間に犠牲層を除去する犠牲層プロセスを採用し、量産性を向上させる可動ゲート型電界効果トランジスタの製造方法を提供する。

【解決手段】第1犠牲層15と、第2犠牲層16と、を有する複合犠牲層の上に可動ゲートが形成される可動ゲート形成工程と、第2犠牲層16がエッチング除去される第2犠牲層除去工程と、第1犠牲層15がエッチング除去される第1犠牲層除去工程と、を備える可動ゲート型電界効果トランジスタの製造方法とした。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】ゲートラストプロセスの適用に際して、トランジスタのフリンジ容量及びゲート抵抗の低減と、実効的なゲート長の短縮を実現する。

【解決手段】本発明の半導体装置の製造方法は、半導体基板1上にゲート絶縁膜2、第1のダミーゲート部3及び第2のダミーゲート部4を順に積層して形成する工程と、それらをパターン加工するとともに、第1のダミーゲート部3をゲート長方向Xで第2のダミーゲート部4よりも後退させることにより、ノッチ部6を形成する工程と、ゲート絶縁膜2、第1のダミーゲート部3及び第2のダミーゲート部4の側方に絶縁材料からなる側壁7を形成し、かつ当該絶縁材料でノッチ部6を埋め込む工程と、第1,第2のダミーゲート部3,4を除去して、当該除去部分の底部にゲート絶縁膜2及びノッチ部6を残す工程と、除去部分を導電材料で埋め込むことによりゲート電極を形成する工程とを有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】チャネル部に対して効果的に応力を印加することが可能で、これによりキャリア移動度の向上を図ることが可能で高機能化が達成された半導体装置を提供する。

【解決手段】半導体基板3の表面を掘り下げた凹部3a内にゲート絶縁膜5を介して設けられたゲート電極7と、ゲート電極7の両脇における半導体基板3の表面側に設けられたソース/ドレイン拡散層11と、ソース/ドレイン拡散層11の表面を覆う状態で半導体基板3の表面よりも深く設けられたシリサイド膜(応力印加層)13とを備えた半導体装置1-1である。半導体基板3の表面に対するチャネル部chの深さ位置d2は、シリサイド膜(応力印加層)13の深さd1位置よりも浅い。

(もっと読む)

半導体装置およびその製造方法

【課題】MISトランジスタを有する半導体装置の性能を向上させる。

【解決手段】シリコン基板1の主面上に半導体層を積み上げて形成された一対のソース・ドレイン領域sdn,sdpと、その側壁を覆う側壁絶縁膜ISと、側壁絶縁膜ISに平面的に挟まれた位置のシリコン基板1の主面上に、ゲート絶縁膜IGを隔てて配置されたゲート電極GEと、ゲート電極GEの側方下部からソース・ドレイン領域sdn,sdpの側方下部に渡って形成されたエクステンション領域exn,expとを有する半導体装置であって、ソース・ドレイン領域sdn,sdpの側壁は順テーパ状の傾斜を有しており、側壁絶縁膜ISの側壁のうち、ゲート絶縁膜IGおよびゲート電極GEと隣り合う方の側壁は、順テーパ状の傾斜を有している。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】本発明は、ゲート構造の劣化を抑制した半導体装置の製造方法および半導体装置を提供することを目的とする。

【解決手段】本発明の一実施形態による半導体装置の製造方法は、Si基板1上にゲート絶縁膜3およびSiN4を積層して仮ゲートパターンを形成し、Si基板1に一部が埋め込まれたソース5およびドレイン5を仮ゲートパターンを挟んで離間して形成し、ソース5、ドレイン5、およびSiN4上にSiO24を形成し、SiO24を平坦化しSiN4を除去して形成されたゲート開口部の側面にSiN8を形成し、ゲート開口部にゲート電極材料9を埋め込むことを特徴とする。

(もっと読む)

半導体装置、およびその製造方法

【課題】良好な形状のキャップ層を形成して、容易に適した仕事関数に制御することができる半導体装置、およびその製造方法を得ることを目的とする。

【解決手段】本発明における半導体装置の製造方法は、high−k膜2および第1のゲート電極膜3が積層したゲートパターンが形成されるとともに、ゲートパターンをマスクとして、第1導電型および第2導電型のソース・ドレイン領域12を形成する。次に、ゲートパターンの周囲を含む全面に層間絶縁膜14を形成する。次に、第1導電型のMISFET形成領域8の第1のゲート電極膜を除去して溝部20aを形成する。次に、溝部20aの底面および側面を含む全面に積層するようにキャップ層15を形成する。次に、溝部20aを埋め込むように第2のゲート電極膜16を形成する。次に、第2導電型のMISFET形成領域9の第1のゲート電極膜3の表面が露出するように除去しキャップ層15を拡散する。

(もっと読む)

半導体装置の製造方法

【課題】組成の安定したゲート電極を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板11に、ゲート長に加工された、ゲート絶縁膜21、シリコン材料膜23a、ストッパ膜25、及びシリコン材料膜23bを順に有する第1の積層膜を備えたpMOS領域1、離間して、ゲート長に加工された、ゲート絶縁膜21、シリコン材料膜23a、及びシリコン材料膜23bを順に有する第2の積層膜を備えたnMOS領域2を形成し、第1及び第2の積層膜の側壁にオフセット膜33、サイドウォール35の形成、及びソース・ドレイン領域15の形成を行い、pMOS領域1のシリコン材料膜23b及びストッパ膜25を除去し、シリコン材料膜23a上、及びnMOS領域2のシリコン材料膜23b上にNiを堆積し、pMOS領域1にNi3Siを形成し、nMOS領域2にNiSi2を形成する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造歩留まりを向上することができるとともに、半導体装置の特性のばらつきを低減することができる半導体装置の製造方法を提供する。

【解決手段】凹凸を有する半導体の表面上に第1イオン注入マスクを形成する工程と、第1イオン注入マスクの表面上に第2イオン注入マスクを形成する工程と、第2イオン注入マスクの表面上にフォトレジストを形成する工程と、フォトレジストの一部を除去して第2イオン注入マスクの表面を露出させる工程と、第2イオン注入マスクの露出部分をエッチングにより除去することによって第1イオン注入マスクの表面を露出させる工程と、第1エッチング工程後に第1イオン注入マスクの露出部分上に残っているエッチング残部をエッチングにより除去する工程とを含む半導体装置の製造方法である。

(もっと読む)

画定された不純物勾配を有するひずみ材料層を使用する半導体構造、およびその構造を製作するための方法。

【課題】不純物の無い区域を有するひずみ材料層を含む半導体構造とデバイス、及びそれを製作するための方法を提供する。

【解決手段】ひずみ材料層104の特定の領域108は、半導体の隣接する部分から相互拡散することができる不純物を無い状態にしておく。不純物がひずみ材料層104の特定の領域108に存在する場合、デバイス性能の低下となる。説明された特徴を有する、又は説明されたステップに従って製作される半導体構造100とデバイス(例えば、電界効果トランジスタ、即ち「FET」)を使用することにより、デバイスの動作が向上する。

(もっと読む)

半導体デバイスを形成する方法

【課題】 ボイドフリーかつシームフリーの金属ゲート導体層が比較的薄い高kゲート誘電体層の上に位置決めされている少なくとも1つの高アスペクト比ゲート構造を有する相補型金属酸化膜半導体(CMOS)デバイスを形成する方法を提供する。

【解決手段】 これらの方法実施形態は、高アスペクト比ゲート・スタック開口部を下から上に金属ゲート導体層で充填するために電気メッキ・プロセスを使用するゲート交換戦略を取り入れている。電気メッキ・プロセス用の電子の発生源は、基板の裏面を直接通過する電流である。これは、シード層の必要性を排除し、ボイドまたはシームなしで金属ゲート導体層が形成されることを保証するものである。さらに、実施形態次第で、電気メッキ・プロセスは、所与の領域への電子流を増強するために(すなわち、メッキを増強するために)照明を受けて実行され、所与の領域への電子流を防止するために(すなわち、メッキを防止するために)暗闇で実行される。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 大幅なプロセスコスト増を伴うことなく、チャネルに歪を発生させることが可能な半導体装置の製造方法を提供する。

【解決手段】 (a)半導体基板の一部の表面上に、半導体膜と、該半導体膜よりも密度の高いブロック膜とがこの順番に積層されたゲートパターンを形成する。(b)ゲートパターンをマスクとして、半導体基板の表層部に、ソース及びドレイン用の不純物を注入する。(c)ゲートパターンをマスクとして、半導体基板内に、ソース及びドレイン用の不純物とは異なる歪形成用の不純物を注入する。(d)半導体基板を熱処理し、歪形成用の不純物が注入された領域を再結晶化させる。

(もっと読む)

半導体素子及びその製造方法

【課題】LDD領域がゲート電極の下部とオーバーラップするのを防止し、素子のパフォーマンスを向上させるようにした半導体素子及びその製造方法を提供する。

【解決手段】STI領域及びゲート領域が定義された下部構造物において、前記STI領域の内部に素子隔離膜を、前記ゲート領域の内部に犠牲層を形成する段階と、前記素子隔離膜及び前記犠牲層をバリア(barrier)とし、前記素子隔離膜と前記犠牲層との間にLDD領域を形成する段階と、前記ゲート領域の内部に形成された前記犠牲層を選択的に除去する段階と、前記犠牲層が除去された前記ゲート領域の内部側壁にスペーサを形成する段階と、前記犠牲層が除去された前記ゲート領域の内部下側にゲート絶縁膜を形成する段階と、前記ゲート絶縁膜の上部にゲート電極を形成する段階と、前記LDD領域の上部に接合領域を形成する段階と、前記LDD領域を前記ゲート領域の下部両側端まで拡散させる段階と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】 金属ゲート電極への熱負荷を低減可能であるとともに、高誘電率ゲート絶縁膜に対する高温での熱処理が可能である半導体装置の製造方法を提供する。

【解決手段】 半導体基板上に高誘電率ゲート絶縁膜及びダミーゲート電極を形成する工程と、少なくとも高誘電率ゲート絶縁膜及びダミーゲート電極をマスクとして半導体基板上にソース及びドレイン領域を形成する工程と、半導体基板上に層間絶縁膜を形成してその一部を除去することでダミーゲート電極上方を露出させる工程と、高誘電率ゲート絶縁膜上のダミーゲート電極を除去して溝を形成する工程と、溝の内部を被覆又は埋め込むように高誘電率ゲート絶縁膜上に金属ゲート電極を形成する工程と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】MOSFETにおいて、ショートチャネル効果の抑制と移動度向上を両立させることを可能とする。

【解決手段】半導体基板13上にダミーゲート絶縁膜31を介してダミーゲート34を形成する工程と、ダミーゲート34の両側の半導体基板13にソース・ドレイン不純物領域23,24を形成する工程と、ダミーゲート34の両側の半導体基板13上にエクステンション領域25,26を形成する工程と、ダミーゲート34直下のソース側にソース不純物領域23のオーバーラップ領域27を形成する工程と、ダミーゲート34を除去し、該除去領域に露出したダミーゲート絶縁膜31を除去する工程と、除去領域に露出した半導体基板13にリセス形状15を形成する工程と、リセス形状15を形成した半導体基板13上にゲート絶縁膜21とゲート電極22とを順次形成する工程とを備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】金属シリサイド膜の膜厚が薄くなってきたり、拡散層幅が小さくなってくると、拡散層上の金属シリサイドが凝集反応を起こしやすくなる、という問題があった。

【解決手段】半導体装置100は、半導体基板2と、半導体基板内に設けられた拡散層4と、半導体基板上に設けられたゲート絶縁膜12と、ゲート絶縁膜上に設けられたゲート電極14と、拡散層上に選択的に設けられたNiシリサイド層8と、を含み、Niシリサイド層8上にはCoを主成分とするメタルキャップ膜18が選択的に設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】 シリサイドの異常成長によるリーク電流の増加を抑制できる半導体装置を提供すること。

【解決手段】 半導体装置は、半導体基板100と、半導体基板100に形成されたMIS型FETであって、半導体基板100上に形成されたゲート絶縁膜106と、ゲート絶縁膜106上に形成されたゲート電極107と、前記MIS型FETのチャネル領域を挟むように形成され、半導体基板100とは格子間隔が異なり、かつ、高さが一定のSiC層103で構成されたソース/ドレイン層と、SiC層103の上面を含む領域上に形成され、かつ、前記チャネル領域には形成されていない金属シリサイド層110とを備えた前記MIS型FETとを具備している。

(もっと読む)

半導体装置の製造方法

【課題】ダマシンゲートプロセスにおいて、ゲート電極用溝形成時に層間絶縁膜が後退せず、短絡の原因となる導電層の残渣が発生しない半導体装置の製造方法を提供する。

【解決手段】チャネル形成領域を有する半導体基板10にダミーゲート絶縁膜12とダミーゲート電極13を形成し、ダミーゲート電極をマスクとして基板にソース・ドレイン領域19を形成し、酸化シリコンよりフッ酸耐性を有する絶縁性材料によりダミーゲート電極より厚い膜厚でダミーゲート電極を被覆して第1絶縁膜21を形成し、その上に第1絶縁膜と異なる絶縁性材料で第2絶縁膜22を形成し、第2絶縁膜の上面から第1絶縁膜の頂部、さらにダミーゲート電極が露出するまで第1絶縁膜と第2絶縁膜とを平坦化除去し、ダミーゲート電極及びダミーゲート絶縁膜を除去し、得られるゲート電極用溝の底部にゲート絶縁膜を形成し、その上にゲート電極を形成し、電界効果トランジスタとする。

(もっと読む)

21 - 40 / 112

[ Back to top ]