Fターム[5F140BG27]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート電極の形成処理 (7,666) | 堆積 (2,821)

Fターム[5F140BG27]の下位に属するFターム

Fターム[5F140BG27]に分類される特許

541 - 553 / 553

半導体デバイス製造のためのゲート材料

電子デバイスを形成する際、半導体層を予めドープして、ドーパント分布アニールをゲート画定前に行う。場合によっては、ゲートは金属から形成されている。したがって、続いて形成される浅いソースおよびドレインは、ゲートアニールステップの影響を受けない。  (もっと読む)

(もっと読む)

半導体コンポーネントとその製造方法

ソース側のハロー領域を有する絶縁ゲート電界効果半導体コンポーネント(100)と、半導体コンポーネント(100)の製造方法である。ゲート構造(112)は半導体基板(102)に形成される。ソース側のハロー領域(120)は半導体基板(102)に形成される。ソース側のハロー領域形成後、スペーサ(127、128、152、154)が、ゲート構造(112)の対辺に隣接して形成される。ソースエクステンション領域(136A)及びドレインエクステンション領域(138A)は、傾斜注入を用いて半導体基板(102)に形成される。ソースエクステンション領域(136A)は、ゲート構造(112)の下に延在する。一方で、ドレインエクステンション領域(138A)は、ゲート構造(112)の下に延在してもよく、あるいは、ゲート構造(112)から横方向に離間してもよい。ソース領域(156)及びドレイン領域(158)は、半導体基板(102)に形成される。  (もっと読む)

(もっと読む)

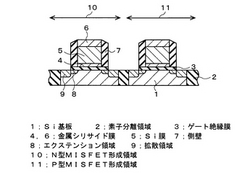

半導体装置及びその製造方法

【課題】 低コストで歩留り良く製造でき、ゲート絶縁膜の信頼性が高く、しきい値電圧のばらつきが小さい半導体装置及びその製造方法を提供する。

【解決手段】 金属シリサイド膜4は、ゲート絶縁膜3上にアモルファスSi膜、金属膜及びSi膜5を順次形成し、熱処理によって金属膜をシリサイド化することにより得られる。金属膜の上にSi膜5を形成し、ゲート電極のゲート絶縁膜3側からのシリサイド化反応により金属シリサイド膜4を形成するため、不純物イオンがゲート電極とゲート絶縁膜3との界面に濃縮することが無い。これにより、不純物イオンのゲート絶縁膜3中又はチャネル領域への拡散を抑制し、MISFETのしきい値のばらつきを低減できる。また、ゲート絶縁膜3とゲート電極との界面における不純物の偏析を抑制し、ゲート電極の剥離を防止することができるため、ゲート絶縁膜3の信頼性が高い。

(もっと読む)

半導体装置およびその製造方法

【課題】厚み均一で且つ低抵抗のシリサイド層をゲート電極に有する半導体装置およびその製造方法を提供する。

【解決手段】シリサイド化する高融点金属の堆積前に、ゲート電極上面に角が発生しないように端部丸めを実施した後にシリサイド化を行ことで、熱処理時に発生する膜応力の集中を緩和し、均一でかつ十分な厚さのシリサイド層を形成する。

(もっと読む)

高誘電率のゲート絶縁膜を有する半導体装置及びそれの製造方法

【課題】 本発明はゲート構造物として高誘電率を有する物質として、高誘電率を有する物質からなるゲート絶縁膜を含む半導体装置及びその製造方法に関する。

【解決手段】 半導体装置及びその製造方法において、基板上に形成され、ハフニウムシリコン酸化物含有固体物質を含むゲート絶縁膜パターンと前記ゲート絶縁膜パターン上に形成される第1ゲート導電膜パターンを含むゲート構造物及び前記ゲート構造物と隣接する基板の表面部位に配置されており、n型不純物がドーピングされたソース/ドレイン領域を含むことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 ゲート絶縁膜に生じるリーク電流を抑制でき、高いトランジスタ特性を維持したまましきい値電圧の制御を個々のトランジスタごとに実行することができる相補型MISFETを提供することである。

【解決手段】 相補型のトランジスタのうちのn型トランジスタのゲート絶縁膜8とp型トランジスタのゲート絶縁膜9との対比において、膜厚および組成のうち少なくともいずれか一方が異なる。それにより、ゲート絶縁膜のしきい値電圧が個々のトランジスタごとに異なる。

(もっと読む)

改善されたしきい電圧およびフラットバンド電圧の安定性を有する相補型金属酸化膜半導体(CMOS)構造およびそれを形成する方法(高k誘電体によるCMOSデバイス形成におけるしきい電圧制御を達成するためのバリア層の選択的実装)

【課題】 改善されたしきい電圧およびフラットバンド電圧の安定性を有するCMOS構造を形成する方法およびそれにより生産されたデバイスを提供することにある。

【解決手段】 発明の方法は、nFET領域とpFET領域とを有する半導体基板を設けるステップと、高k誘電体の上に絶縁中間層を含む誘電体スタックを半導体基板の上に形成するステップと、pFET領域から絶縁中間層を除去せずに、nFET領域から絶縁中間層を除去するステップと、pFET領域内に少なくとも1つのゲート・スタックを設け、nFET領域内に少なくとも1つのゲート・スタックを設けるステップとを含む。絶縁中間層はAlNまたはAlOxNyにすることができる。高k誘電体は、HfO2、ハフニウム・シリケート、またはハフニウム酸窒化シリコンにすることができる。絶縁中間層は、HCl/H2O2過酸化水素溶液を含むウェット・エッチングによりnFET領域から除去することができる。

(もっと読む)

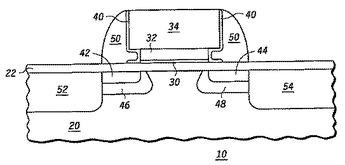

切り欠き制御電極及び当該電極の構造を有する半導体素子の製造方法

半導体素子(10)を形成する方法では、一の表面を有する基板(20)を設け、絶縁層(22)を基板(20)の表面の上に形成し、第1パターニング済み導電層(30)を絶縁層(22)の上に形成し、第2パターニング済み導電層(32)を第1パターニング済み導電層(30)の上に形成し、パターニング済み非絶縁層(34)を第2パターニング済み導電層(32)の上に形成し、そして第1及び第2パターニング済み導電層(30,32)の一部分を選択的に除去して、半導体素子(10)の切り欠き制御電極を形成する。  (もっと読む)

(もっと読む)

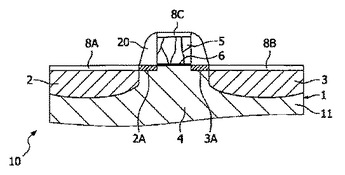

半導体デバイスを製造する方法およびそのような方法で得られる半導体デバイス

本発明は、半導体デバイス(10)を製造する方法であって、シリコンの半導体本体(1)がその表面に第1導電型の半導体領域(4)を備え、その領域に、第1導電型とは逆の第2導電型の第2半導体領域(2A、3A)が、第2導電型のドーパント原子の半導体本体(1)への添加によって第1半導体領域(4)とのpn接合を形成して形成され、前記ドーパント原子の添加の前に、不活性原子のアモルファス化注入によってアモルファス領域が半導体本体(1)内に形成され、アモルファス化注入後、半導体本体(1)に暫定的ドーパント原子が注入され、第2導電型のドーパント原子の添加後、半導体本体が、それに約500℃から約800℃までの、好ましくは550℃から750℃までの範囲の温度での熱処理を加えることによって、アニールされる方法に関する。第2導電型のドーパント原子はイオン注入によって半導体本体(1)に添加される。このようにして、非常に浅く、熱的に安定で、急峻で、低オーミックであるMOSFETのソースおよびドレイン拡張部(2A、3A)を形成するのに非常に適しているpn接合が形成される。  (もっと読む)

(もっと読む)

バイオコンポーネントを測定するための電解効果トランジスタ

生物細胞又は類似のバイオコンポーネントについて測定を実施するための装置であって、電界効果トランジスタ(1)を有しており、その電界効果トランジスタが基板上にソース、ドレイン及びそれらを互いに接続するチャネルエリア(4)を有しており、そのチャネルエリア上にゲート電極(8)が配置されている。ゲート電極(8)は、少なくとも2つの、側方に並べて配置された電極領域(10)を有しており、それらは、チャネルエリア(4)がソース(3a)をドレイン(3b)と接続する方向に対して直角方向に互いに対して隔たって、かつ電気的に互いに対して絶縁されている。 (もっと読む)

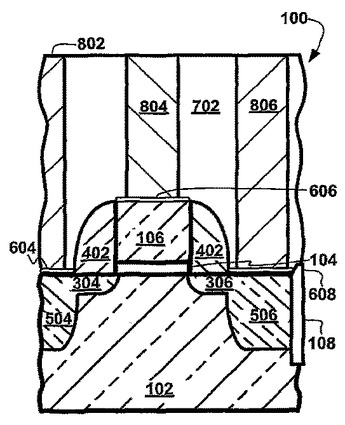

集積回路技術における低応力の側壁スペーサ

半導体基板(102)に集積回路の形成方法(900)を提供する。半導体基板(102)上にゲート絶縁膜(104)が形成され、このゲート絶縁膜(104)上にゲート(106)が形成される。半導体基板(102)にソース/ドレイン接合部(304)(306)が形成される。低出力プラズマ化学気相成長法プロセスを使用して、ゲート(106)の周りに側壁スペーサ(402)を形成する。ソース/ドレイン接合部(304)(306)およびゲート(106)に、シリサイド(604)(606)(608)を形成し、半導体基板(102)上に層間絶縁層(702)をたい積する。その後、層間絶縁層(702)中にシリサイド(604)(606)(608)へのコンタクト(802)(804)(806)が形成される。  (もっと読む)

(もっと読む)

格子定数の異なる材料を用いる半導体構造及び同構造の形成方法

半導体構造体(10)は、第1格子定数を有する第1緩和半導体材料から構成された基板を含む。半導体デバイス層(34)は基板を覆い、該半導体デバイス層は第1格子定数とは異なる第2格子定数を有する第2緩和半導体材料(22)を含む。加えて、誘電体層が基板と半導体デバイス層との間に介在され、該誘電体層は第1格子定数と第2格子定数間の遷移のため、誘電体層内に配置されたプログラムされた遷移帯を含む。該プログラムされた遷移帯は複数層を含み、該複数層の隣接する層は異なる格子定数を有し、隣接する層の1つが欠陥を形成するのに必要な第1限界厚さを超える第1厚さを有し、隣接する層の別の層が第2限界厚さを超えない第2厚さを有する。複数層の各隣接する層は、遷移帯内の欠陥を促進してプログラムされた遷移帯の縁部に移行させて終端させる境界面を形成する。また、該半導体構造を製造する方法も開示される。

(もっと読む)

(もっと読む)

半導体装置及びその製造方法

Si(100)基板の表面にシリコン酸化膜を形成した後、このシリコン酸化膜をプラズマ窒化して酸窒化シリコン膜にする。その後NOガス雰囲気中で770乃至970℃の温度条件下で熱処理することにより、ゲート絶縁膜における基板との界面部分の窒素濃度を1乃至10原子%にすると共に、基板と酸窒化シリコン膜との界面に存在する界面Si結合欠陥の結合手の方位角分布が、基板の[100]方位に対して25°以上の角度にピークをもつようにする。 (もっと読む)

541 - 553 / 553

[ Back to top ]