Fターム[5F140BG34]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート電極の形成処理 (7,666) | 熱処理 (1,248) | シリサイド化 (1,065)

Fターム[5F140BG34]の下位に属するFターム

雰囲気 (113)

Fターム[5F140BG34]に分類される特許

201 - 220 / 952

半導体装置および半導体装置の製造方法

【課題】半導体基板上に設けられる金属半導体化合物電極の界面抵抗を低減する半導体装置およびその製造方法を提供する。

【解決手段】半導体基板と、半導体基板上に形成され、Sを1×1020atoms/cm3以上含有する界面層と、界面層上に形成され、略全域にSを1×1020atoms/cm3以上含有する金属半導体化合物層と、金属半導体化合物層上の金属電極を有することを特徴とする半導体装置。半導体基板上に金属膜を堆積し、第1の熱処理により、金属膜を半導体基板と反応させて、金属半導体化合物層を形成し、金属半導体化合物層に、飛程が金属半導体化合物層の膜厚未満となる条件でSをイオン注入し、第2の熱処理により、Sを再配置することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】インパクトイオン化領域にてキャリアがゲート絶縁膜に入り込むことがない半導体装置とその製造方法を提供する。

【解決手段】トランジスタ部分22と、ダイオード部分23を具備し、トランジスタ部分22は、第1導電型又は真性の半導体領域であるチャネル形成領域6と、チャネル形成領域6に接するゲート絶縁膜7と、チャネルを形成させるゲート電極8と、第2導電型あり、チャネル形成領域6に接し、ドレイン電圧が供給されるドレイン領域4と、第2導電型であり、チャネル形成領域6を介してドレイン領域4に対向し、チャネル形成領域6にチャネルが形成されたときにチャネル形成領域6を介してドレイン電圧が供給されるソース領域5とを含み、ダイオード部分23は、ソース領域5に電気的に接続されており、ソース領域5にドレイン電圧が供給されたときに、ダイオード部分23はインパクトイオン化現象が発生する領域を含む。

(もっと読む)

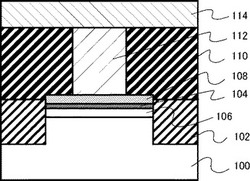

トランジスタにおいて進歩したシリサイド形成と組み合わされる凹型のドレイン及びソース区域

【解決手段】

洗練されたトランジスタ要素を形成するための製造プロセスの間、それぞれの金属シリサイド領域を形成するのに先立つ共通のエッチングシーケンスにおいて、ゲート高さが減少させられてよく、そして凹型のドレイン及びソース構造もまた得られてよい。対応する側壁スペーサ構造はエッチングシーケンスの間に維持され得るので、ゲート電極におけるシリサイド化プロセスの可制御性及び均一性を高めることができ、それにより、低減された程度のスレッショルドばらつきを得ることができる。更に、凹型のドレイン及びソース構造が、全体的な直列抵抗の低減及び応力転移効率の増大をもたらすことができる。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の製造工程においてストレッサー膜などから発生する水素によるp型MOSトランジスタの駆動力低下を防止する。

【解決手段】半導体装置は、n型活性領域13B上に形成されたゲート絶縁膜15と、ゲート絶縁膜15上に形成されたゲート電極16Bと、ゲート絶縁膜15及びゲート電極16Bの側面に形成された内側サイドウォール17及び外側サイドウォール20Bと、p型ソースドレイン領域21Bと、内側サイドウォール17の側面及び外側サイドウォール20Bの側面における少なくとも底部に形成され、水素に対してバリア性を有する絶縁性の水素バリア膜23とを備える。

(もっと読む)

半導体装置の製造方法

【課題】サリサイドプロセスで金属シリサイド層を形成した半導体装置の信頼性を向上させる。

【解決手段】ゲート電極GE1,GE2、ソース・ドレイン用のn+型半導体領域7b及びp+型半導体領域8bを形成してから、半導体基板1上にNi1−xPtx合金膜を形成し、第1の熱処理を行って合金膜とゲート電極GE1,GE2、n+型半導体領域7b及びp+型半導体領域8bとを反応させることで、(Ni1−yPty)2Si相の金属シリサイド層41aを形成する。この際、Niの拡散係数よりもPtの拡散係数の方が大きくなる熱処理温度で第1の熱処理を行ない、かつ、金属シリサイド層41a上に合金膜の未反応部分が残存するように、第1の熱処理を行なう。これにより、y>xとなる。その後、未反応の合金膜を除去してから、第2の熱処理を行って金属シリサイド層41aを更に反応させることで、Ni1−yPtySi相の金属シリサイド層41bを形成する。

(もっと読む)

半導体装置の製造方法

【課題】容易にコンタクト抵抗を低減することができる半導体装置の製造方法を提供する。

【解決手段】半導体基板1上に多結晶シリコン膜を形成し、その後、この多結晶シリコン膜の表面をエッチングする。そして、エッチングされた多結晶シリコン膜をシリサイド化して、シリサイド膜12を形成する。更に、シリサイド膜12に接するプラグ23s、23d及び23gを層間絶縁膜21内に形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】信頼性が高く良好な特性を有する半導体装置を提供する。

【解決手段】半導体基板101上に形成され、チャネル領域とチャネル領域を挟むソース/ドレイン・エクステンション領域108の少なくとも一部とを含むSiGe膜104aと、半導体基板の表面領域に形成され、ソース/ドレイン・エクステンション領域に接するソース/ドレイン・コンタクト領域110と、SiGe膜上に形成されたゲート絶縁膜105およびゲート電極106を有するゲート構造と、SiGe膜上に形成され、且つゲート構造の側面に形成された第1の側壁膜107と、SiGe膜上に形成され、且つ第1の側壁膜上に形成された第2の側壁膜109と、ソース/ドレイン・コンタクト領域上に形成され、且つSiGe膜の側面および第2の側壁膜上に形成された第3の側壁膜111と、ソース/ドレイン・コンタクト領域上に形成されたシリサイド膜112と、を備える。

(もっと読む)

半導体装置、およびその製造方法

【課題】製造工程におけるエピタキシャル結晶層への熱的負荷を低減することのできる半導体装置、およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体基板上に第1のゲート絶縁膜を介して形成された第1のゲート電極、前記半導体基板中の前記第1のゲート絶縁膜下に形成された第1のチャネル領域、前記半導体基板中の前記第1のチャネル領域の両側に形成された第1の結晶からなる第1のエピタキシャル結晶層、を含む第1のトランジスタと、前記半導体基板上に第2のゲート絶縁膜を介して形成された第2のゲート電極、前記半導体基板中の前記第2のゲート絶縁膜下に形成された第2のチャネル領域、前記半導体基板中の前記第2のチャネル領域の両側に形成された第2の結晶からなる第2のエピタキシャル結晶層、前記第2のエピタキシャル結晶層上に形成された前記第1の結晶からなる第3のエピタキシャル結晶層、を含む、前記第1のトランジスタと異なる導電型を有する第2のトランジスタと、を有する。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】NMOSFET及びPMOSFET等のNMOS及びPMOSを有する半導体装置において、ゲート電極の実効仕事関数を、Siバンドギャップのmid-gap付近の値に安定的に設定することが可能な半導体装置及びその製造方法を提供する。

【解決手段】素子分離膜によって分離されてなる、p型拡散層及びn型拡散層を有する半導体基板と、前記半導体基板の、前記p型拡散層及びn型拡散層それぞれの上に形成されてなるゲート絶縁膜と、前記ゲート絶縁膜上に形成された金属膜を含むゲート電極と、前記ゲート絶縁膜と前記金属膜との界面に形成されたGe介在物と、前記金属膜上に形成されたシリコン含有層と、を具えるようにして半導体装置を構成する。

(もっと読む)

高応力下にあるチャネルを有するMOSデバイスを製造するための方法

【解決手段】

シリコン含有基板を備えた半導体デバイスを形成するための方法が提供される。1つの例示的な方法は、シリコン含有基板を覆う多結晶シリコン層を堆積させることと、多結晶シリコン層をアモルファス化することと、アモルファス化された多結晶シリコン層をエッチングしてゲート電極を形成することと、ゲート電極を覆う応力誘起層を堆積させることと、シリコン含有基板を焼鈍してゲート電極を再結晶化することと、応力誘起層を除去することと、ゲート電極をエッチングマスクとして用いて基板内へ凹部をエッチングすることと、凹部内に不純物ドープのシリコン含有領域をエピタキシャル成長させることとを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】オフセットスペーサが除去されることを防止する。

【解決手段】第1導電型の半導体領域10x上に形成されたゲート絶縁膜13Aと、ゲート絶縁膜上に形成されたゲート電極15Aと、ゲート電極の側面上に形成されたオフセットスペーサ17Aと、ゲート電極の側面上にオフセットスペーサを介して形成された断面形状がL字状の内側サイドウォール19と、ゲート電極15A、オフセットスペーサ17A、内側サイドウォール19、及び半導体領域10xにおける内側サイドウォール19の外側方に位置する領域を覆うように形成された絶縁膜24とを備え、オフセットスペーサ17Aは、ゲート電極の側面上に形成された内側オフセットスペーサ16と、ゲート電極の側面上に内側オフセットスペーサ16を覆うように形成された外側オフセットスペーサ17とを有し、外側オフセットスペーサは、内側オフセットスペーサの上端及び外側面に接して形成されている。

(もっと読む)

金属シリサイド形成のための方法および装置

本明細書で述べられる実施形態は、無拡散アニールプロセスを使用して金属シリサイド層を形成する方法を包含する。一実施形態では、基板上に金属シリサイド材料を形成するための方法が、提供される。その方法は、基板のシリコン含有表面を覆って金属材料を堆積させるステップと、金属材料を覆って金属窒化物材料を堆積させるステップと、金属窒化物材料を覆って金属接点材料を堆積させるステップと、基板を無拡散アニールプロセスにさらして金属シリサイド材料を形成するステップとを含む。無拡散アニールプロセスの短い時間枠は、窒素がシリコン含有界面に拡散して窒化シリコンを形成する時間を低減し、それ故に界面抵抗を最小限にする。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】STI構造の素子分離を行う場合にソース/ドレイン領域の形成時点で半導体基板に対する転位の発生を抑制できるようにする。

【解決手段】素子分離絶縁膜3を活性領域2との間の接触領域においてシリコン基板1の表面の高さよりも深く且つソース/ドレイン領域1bのピーク濃度となる高濃度不純物拡散領域1bの形成深さd4(もしくはPN接合部)よりも浅い高さに位置し、当該領域よりも外方領域に遠ざかるに連れて深さd4よりも深い深さd2に位置するように形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】極浅接合の深さが精密制御された半導体装置およびその製造方法を提供する。

【解決手段】主面が第1面方位である第1導電型の第1半導体層11と、第1半導体層11上に直接接合され、主面が第1面方位と異なる第2面方位である第1導電型の第2半導体層12と、第2半導体層12に連接して第1半導体層11上に形成され、主面が第1面方位である第3半導体層13a、13bと、第2半導体層12上にゲート絶縁膜を介して形成されたゲート電極15と、ゲート電極15をゲート長方向に挟むように第2半導体層12に形成され、第1半導体層11と第2半導体層12との接合面16に至る第2導電型の第1不純物拡散領域17a、17bと、第1不純物拡散領域17a、17bをゲート長方向に挟むように第3半導体層13a、13bから第1半導体層11の上部にかけて形成された第2導電型の第2不純物拡散領域18a、18bと、を具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】寄生抵抗の低減に対して有利な半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板11と、前記半導体基板上にゲート絶縁膜12を介して設けられるゲート電極13と、前記半導体基板中に前記ゲート電極を挟むように隔離して設けられるエクステンション領域LDDと、前記エクステンション領域の両側を挟むように前記半導体基板中に設けられ、前記半導体基板とは異なる格子定数有し、前記半導体基板に歪みを付与する歪み付与層22と、前記エクステンション領域の両側の前記半導体基板中に前記ゲート電極を挟むように隔離して設けられるソース/ドレインS/Dと、前記ソース/ドレイン上に設けられるシリサイド層SS/Dとを具備し、前記歪み付与層と前記半導体基板との界面Si-Siは、少なくとも前記シリサイド層の底面の一部に一致する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】高誘電率膜をゲート絶縁膜として用いたCISトランジスタの信頼性を向上する。

【解決手段】基板1の主面には、素子分離領域2によって互いに絶縁分離されたpMISトランジスタの活性領域およびnMISトランジスタの活性領域が設けられている。素子分離領域2に係るようにnMISトランジスタの活性領域上にnMISトランジスタのゲート絶縁膜を構成するハフニウム系酸化膜5が設けられており、そのハフニウム系酸化膜5と素子分離領域2上で接触し、pMISトランジスタの活性領域上にハフニウム系酸化膜5と異なる材料から構成されるpMISトランジスタのゲート絶縁膜を構成するハフニウム系酸化膜9が設けられている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】閾値電圧が異なるトランジスタ毎に閾値電圧を調整する技術を提供する。

【解決手段】半導体装置は、半導体基板と、半導体基板上に設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられたゲート電極と、を含む閾値電圧が異なる複数種類の電界効果型トランジスタを備え、電界効果型トランジスタの少なくとも1種類は、ゲート絶縁膜に少なくとも1種類の金属が存在する。

(もっと読む)

半導体装置およびその製造方法

【課題】設計寸法に近い素子領域を形成可能で、GIDLと類似の現象の発生を抑制可能で、かつ導電膜の酸化により素子領域に印加される圧縮応力を抑制可能な半導体装置およびその製造方法を提供する。

【解決手段】半導体基板SBの主表面に溝TRが形成される。溝TRの壁面を酸化することにより壁面に第1の酸化膜TO1aが形成される。溝TR内を埋め込むように埋め込み導電膜BCが形成される。活性酸化種を含む雰囲気下にて埋め込み導電膜BCを酸化することにより第2の酸化膜TO1bが形成される。第2の酸化膜TO1b上に第3の酸化膜TO2が気相成長法または塗布法により形成される。

(もっと読む)

同一の能動領域内に形成されるトランジスタにおいて能動領域内に局所的に埋め込み歪誘起半導体材質を設けることによる駆動電流調節

【解決手段】

共通の能動領域内に少なくとも1つの埋め込み半導体合金を設けることによって得られる異なる歪レベルに基いて、その能動領域内に形成されるプルダウントランジスタ及びパストランジスタの駆動電流能力を調節することができ、それにより能動領域の単純化された全体的な幾何学的構造を提供することができる。従って、能動領域の単純化された構造を伴う最小のチャネル長に基きスタティックRAMセルを形成することができ、プルダウン及びパストランジスタに対する駆動電流の比を調節するためにトランジスタ幅の明白な変化が従来的に用いられている洗練されたデバイスで観察され得るような顕著な歩留まり低下を回避することができる。

(もっと読む)

半導体装置の製造方法

【課題】急峻な不純物濃度のプロファイルを有するソース領域およびドレイン領域を形成することのできる半導体装置の製造方法を提供する。

【解決手段】この半導体装置の製造方法は、半導体基板の表面近傍に不純物を注入して不純物注入領域を形成する工程と、前記半導体基板にエッチングを施すことにより前記不純物注入領域の底部よりも深い溝を形成し、前記不純物注入領域を分断してソース領域およびドレイン領域を形成する工程と、前記溝の内部にSi系単結晶をエピタキシャル成長させてエピタキシャル結晶層を形成する工程と、前記エピタキシャル結晶層の上部にゲート絶縁膜およびゲート電極を形成する工程と、を含む。

(もっと読む)

201 - 220 / 952

[ Back to top ]