Fターム[5F140BG34]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート電極の形成処理 (7,666) | 熱処理 (1,248) | シリサイド化 (1,065)

Fターム[5F140BG34]の下位に属するFターム

雰囲気 (113)

Fターム[5F140BG34]に分類される特許

161 - 180 / 952

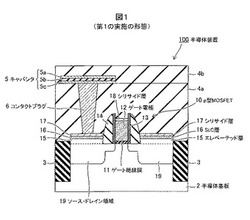

半導体装置およびその製造方法

【課題】耐熱性に優れたシリサイド層をソース・ドレイン領域に有するp型MOSFETを備える半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、半導体基板2上にゲート絶縁膜11を介して形成されたゲート電極12と、半導体基板2上のゲート電極12の両側に形成されたエレベーテッド層15と、エレベーテッド層15上に形成されたSi:C16層と、半導体基板2、エレベーテッド層15、およびSi:C16内のゲート電極12の両側に形成されたp型のソース・ドレイン領域19と、Si:C層16上に形成されたシリサイド層17と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】MIPS構造を有する電界効果トランジスタにおいて、金属ゲート電極とポリシリコンゲート電極との接触抵抗を低減することにより、AC動作を向上させる。

【解決手段】半導体装置1は、半導体基板10上に電界効果トランジスタを有する。電界効果トランジスタは、ゲート絶縁膜25、27とゲート電極63、71と、を備える。さらに、ゲート電極63、71は第1金属からなる第1電極層22と、第2金属からなる第2電極層26、34と、シリコン層からなる第3電極層62、70と、を含む積層構造である。第2金属は、シリコン層の多数キャリアに対する第1電極層22と第3電極層62、70とのバンド不連続を緩和する仕事関数を有する材料である。

(もっと読む)

半導体装置及びその製造方法

【課題】n型MISトランジスタとp型MISトランジスタとにおいてサイドウォール幅が同一である場合、n型MISトランジスタの高信頼性とp型MISトランジスタの高性能化を両立させることは難しい。

【解決手段】半導体装置は、n型MISトランジスタとp型MISトランジスタとを備えている。n型MISトランジスタは、半導体基板10における第1の活性領域10a上に順次形成された第1のゲート絶縁膜13a及び第1のゲート電極14aと、第1のゲート電極14aの側面上に形成された第1のサイドウォール16aとを備えている。p型MISトランジスタは、半導体基板10における第2の活性領域10b上に順次形成された第2のゲート絶縁膜13b及び第2のゲート電極14bと、第2のゲート電極14bの側面上に形成された第2のサイドウォール16bとを備えている。第2のサイドウォール16bは、第1のサイドウォール16aに比べてサイドウォール幅が小さい。

(もっと読む)

半導体装置

【課題】SiGeのチャネルを有する半導体装置の高性能化及び高信頼化をはかる。

【解決手段】シリコンを主成分とする半導体基板101の一主面に設けられ、素子分離絶縁膜102によって区画された素子形成領域103と、チャネル領域となるSi及びGeを主成分とし素子形成領域103上に設けられた半導体膜104と、半導体膜104上にゲート絶縁膜105を介して設けられたゲート電極106と、チャネル領域を挟んで半導体膜104及び基板101に形成されS/D領域110と、ゲート電極106の両側面に設けられた側壁絶縁膜109と、S/D領域110上の側壁絶縁膜109で区画されたS/Dコンタクト領域上に半導体膜104と金属との反応により形成され、且つS/Dコンタクト領域以外の半導体膜104よりも薄い膜厚に形成された金属化合物膜111とを備えた。

(もっと読む)

半導体装置の製造方法

【課題】

製造工程を簡略化しつつ、特性の優れた第1のMOSトランジスタと第2のMOSトランジスタとを製造する半導体装置の製造方法を提供する。

【解決手段】

半導体基板に、第1のMOSトランジスタ領域、第2のMOSトランジスタ領域を画定する素子分離領域を形成し、第1のMOSトランジスタ領域、第2のMOSトランジスタ領域に第1導電型の不純物をイオン注入し、第1導電型のウェルを形成し、第1のMOSトランジスタ領域、第2のMOSトランジスタ領域上に絶縁ゲート電極を形成し、第2のMOSトランジスタのドレイン領域を覆うマスクを介して、半導体基板法線方向から傾いた複数方向から第1導電型の不純物をイオン注入し、第1のMOSトランジスタ領域の前記絶縁ゲート電極下方に対称的なチャネルドーズ領域、第2のMOSトランジスタ領域の前記絶縁ゲート電極下方に非対称なチャネルドーズ領域を形成し、半導体装置を製造する。

(もっと読む)

ソース/ドレインゾーンに沿って調節したポケット部分を具備する非対称的電界効果トランジスタを有する半導体構成体の構成及び製造

【課題】 半導体ボディの上部表面に沿って設けられている非対称的絶縁ゲート電界効果トランジスタ(100U又は102U)は、該トランジスタボディ物質のチャンネルゾーン(244又は284)によって横方向に分離された第1及び第2ソース/ドレインゾーン(240及び242又は280及び282)を包含している。

【解決手段】 ゲート電極(262又は302)がチャンネルゾーン上方でゲート誘電体層(260又は300)の上側に位置している。該ボディ物質の横方向に隣接した物質よりも一層高度にドープした該ボディ物質のポケット部分(250又は290)が該S/Dゾーンの内のほぼ第1のもののみに沿って該チャンネルゾーン内に延在している。該ポケット部分の垂直ドーパント分布は、互いに離隔されている夫々の位置(PH−1乃至PH−3)において複数個の局所的最大(316−1乃至316−3)に到達すべく調節されている。該調節は、典型的に、該ポケット部分の垂直方向ドーパント分布が上部半導体表面近くで比較的平坦であるように実施される。その結果、該トランジスタのリーク電流は減少されている。

(もっと読む)

半導体装置及びその製造方法

【課題】シェアードコンタクト形成時に、ゲート電極が溶解されて形状異常となるのを防止する。

【解決手段】半導体装置は、基板1上にゲート絶縁膜2を介して形成されたゲート電極31と、基板1のゲート電極31の両側方に形成された不純物領域32及び33とを有するトランジスタと、トランジスタ上を覆うように基板1上に形成された層間絶縁膜11及び12と、不純物領域32及び33及びゲート電極31に電気的に接続するシェアードコンタクト14とを備える。ゲート電極31の側面下部を覆うように第1のサイドウォール5、第1のサイドウォール5におけるゲート電極31とは反対側に第2のサイドウォール6、第1のサイドウォール5上に、ゲート電極31の側面上部と第2のサイドウォール6とに挟まれるように第3のサイドウォール9bが形成されている。第2及び第3のサイドウォール6及び9bは、第1のサイドウォール5とは異なる材料からなる。

(もっと読む)

L形状スペーサを使用した非対称的電界効果トランジスタの製造及び構成体

【課題】 非対称的電界効果トランジスタ(102)の製造は、半導体ボディのボディ物質のチャンネルゾーン(284)の上方でそれからゲート誘電体層(300)によって垂直方向に分離されているゲート電極(302)を画定することとなる。

【解決手段】 該ゲート電極をドーパント阻止用シールドとして使用して、半導体ドーパントを該ボディ物質内に導入させて、一層高度にドープしたポケット部分(290)を画定する。該ゲート電極に沿ってスペーサ(304T)を設ける。該スペーサは、(i)該ゲート電極に沿って位置されている誘電体部分、(ii)該半導体ボディに沿って位置されている誘電体部分、及び(iii)該他の2つのスペーサ部分の間の空間をほぼ占有するフィラー部分(SC)、を包含している。該ゲート電極及び該スペーサをドーパント阻止用シールドとして使用して、半導体ドーパントを該半導体ボディ内に導入させて、一対のソース/ドレイン部分(280M及び282M)を画定する。該フィラースペーサ部分を除去して該スペーサをL形状(304)へ変換させる。一対の電気的コンタクト(310及び312)を夫々該主要ソース/ドレイン部分に対して形成する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置内の埋め込みコンタクトホールを簡略な工程で形成するための半導体装置の製造方法を提供する。

【解決手段】シリコン基板101上に1又は複数の半導体素子が作り込まれてなる半導体装置に埋め込みコンタクトを形成するにあたり、半導体素子層の全面に層間絶縁膜109を形成する(第1工程)。次いで、半導体装置内のシリコン106、107、ポリシリコン104A、104B、又は金属シリサイド108A,108Bからなる2つの領域が露出するように層間絶縁膜にコンタクトホール109aを形成する(第2工程)。そして、コンタクトホールから露出しているシリコン106、107、ポリシリコン104A、104B、又は金属シリサイド108A,108Bの表面に無電解めっき法により選択的に金属膜111を形成する(第3工程)。

(もっと読む)

半導体装置の製造方法

【課題】配線層に銅配線を使用する半導体装置において、半導体基板の裏面に付着した銅原子が半導体基板の裏面から内部へと拡散することを抑制し、半導体基板の主面に形成されているMISFETなどの半導体素子の特性劣化を抑制できる技術を提供する。

【解決手段】半導体基板1Sの主面に形成される銅拡散防止膜を銅拡散防止膜DCF1aとし、半導体基板1Sの裏面に形成される銅拡散防止膜を銅拡散防止膜DCF1bとする。本実施の形態1の特徴は、半導体基板1Sの裏面に銅拡散防止膜DCF1bを形成する点にある。このように、銅配線の形成工程の前に、半導体基板1Sの裏面に銅拡散防止膜DCF1bを形成することにより、半導体基板1Sの裏面から銅原子(銅化合物を含む)が拡散することを防止できる。

(もっと読む)

ゲート・ダイオード構造及びゲート・ダイオード構造の製造方法

【課題】改善された特性と強化された機能とを備えたダイオード構造とその製造方法が望まれている。

【解決手段】ゲート・ダイオード構造及びSOI基板(SOI)等の上にゲート・ダイオード構造を製造する方法であって、緩和下地層(34‘)を用いる。緩和下地層は歪下地層(34)から形成される。歪下地層(34)は典型的にはゲート・ダイオード構造と同時に形成される電界効果型トランジスタに用いられる。緩和下地層は歪下地層(34)のイオン注入処理のような処理により形成される。反応性イオンエッチング方法を用いてゲート・ダイオード構造から歪下地層を除去するときのゲート・ダイオードの損傷がないので、歪下地層に比較して、緩和下地層はゲート・ダイオード構造の理想値を改善する。

(もっと読む)

半導体素子及びその製造方法

【課題】ソース・ドレイン電極及び/又はゲート電極の低抵抗化を図り、微細化・高集積化を損なうことなく、低消費電力で高速操作可能な半導体素子を提供する。

【解決手段】素子分離領域102によりシリコン基板101A表層に画成された素子領域に、チャネル領域を隔てて形成された一対のソース・ドレイン領域106と、ソース・ドレイン領域のそれぞれに導通するソース・ドレイン電極と、チャネル領域上にゲート絶縁膜103を介して形成されたゲート電極と、を備えた半導体素子において、ソース・ドレイン電極及び/又はゲート電極を、ソース・ドレイン領域表面又はゲートを構成するポリシリコン層表面に形成した第1金属膜がシリサイド化されてなるシリサイド層107bと、このシリサイド層上に無電解メッキ法により形成された第2金属膜108と、で構成する。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板の表面を均一にアニールする半導体装置の製造方法を提供する。

【解決手段】半導体基板に第1不純物元素を注入する工程と、前記半導体基板上に絶縁膜となる酸化膜または窒化膜を形成する膜成膜工程と、前記絶縁膜上にシリコン膜を形成するシリコン膜成膜工程と、前記シリコン膜に第2不純物元素を注入する注入工程と、前記第2不純物元素が注入された前記シリコン膜にシリコンの吸収端の波長よりも短い波長の光を照射する短波長光アニール工程と、前記短波長光アニール工程の後、前記シリコン膜にシリコンの吸収端の波長よりも長い波長の光を照射する長波長光アニール工程と、を有する半導体装置の製造方法により上記課題を解決する。

(もっと読む)

半導体装置の製造方法

【課題】王水等の薬液によるシリサイド膜表面における腐食発生を抑制し、良好なPt含有シリサイド膜を形成する半導体装置の製造方法を提供する。

【解決手段】シリコンを含む半導体層を有する基板上または基板上に形成されたシリコンを含む導電膜上に、貴金属を含む金属膜を形成する工程(a)と、工程(a)の後、基板に対して熱処理を行って前記貴金属とシリコンとを反応させ、基板上または導電膜上に前記貴金属を含むシリサイド膜を形成する工程(b)と、工程(b)の後、第1の薬液を用いて、シリサイド膜のうち未反応の貴金属11の下に位置する部分上に酸化膜12を形成する工程(c)と、第2の薬液を用いて未反応の貴金属を溶解する工程(d)とを備える。

(もっと読む)

半導体装置の製造方法

【課題】所望のシリサイド膜を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】第1の加熱温度の第1の加熱処理により、ソース・ドレイン拡散層3のシリコンとソース・ドレイン拡散層上の第1の金属とを反応させて、ソース・ドレイン拡散層の上部をシリサイド化してシリサイド膜を形成し、素子分離絶縁膜の上の第1の金属膜の表面上に第1の金属よりも融点が高い高融点金属である第2の金属を堆積して、少なくとも第1の金属膜の表面を被覆するように第2の金属膜を形成し、第2の加熱温度の第2の加熱処理により、少なくとも第1の金属膜の表面を第2の金属膜と反応させて、合金膜106aを形成し、第1の加熱温度および第2の加熱温度よりも高い第3の加熱温度の第3の加熱処理により、シリサイド膜のシリコンの濃度を増加させ、合金膜、第1の金属膜の未反応部分、および、第2の金属膜の未反応部分を選択的に除去する。

(もっと読む)

スタティック・ランダム・アクセス・メモリ

【課題】スタティックノイズマージンの低下を抑制できるスタティック・ランダム・アクセス・メモリを得ること。

【解決手段】スタティック・ランダム・アクセス・メモリのメモリセルにおける一対のロードトランジスタは、それぞれ、第1のSiGe膜がシリコン基板のソース領域と第1のシリサイド膜との間に存在し、第2のSiGe膜がシリコン基板のドレイン領域と第2のシリサイド膜との間に存在し、前記第1のSiGe膜ならびに前記第2のSiGe膜は、前記前記ソース領域と前記ドレイン領域の間のチャネル領域のシリコン基板の表面よりも低い位置に存在することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極をシリサイド化する際にゲート長方向の体積膨張が生じにくく、ゲート電極とコンタクトプラグ等との短絡不良が生じにくい半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板10の上にゲート絶縁膜15を介在させて形成され、上部がシリサイド化されたゲート電極17と、ゲート電極17の側面上に形成されたオフセットスペーサ20と、オフセットスペーサ20の側面上を覆う断面L字状のサイドウォール22Aとを備えている。オフセットスペーサ20は、ゲート電極17側に形成された内側オフセットスペーサ20Aと、内側オフセットスペーサ20Aの側面上に形成された外側オフセットスペーサ20Bとを有している。内側オフセットスペーサ20Aと、外側オフセットスペーサ20B及び内側サイドウォール22Aとは、エッチング選択性が異なる材料からなる。

(もっと読む)

半導体装置

【課題】ソース・ドレイン領域のエクステンション領域の不純物濃度プロファイルが急峻なp型トランジスタを有する半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置1aは、半導体基板2上に形成された結晶層13と、結晶層13上にゲート絶縁膜14を介して形成されたゲート電極15と、半導体基板2と結晶層13との間に形成された、ゲート電極15の下方の領域において第1の不純物を含むC含有Si系結晶からなる不純物拡散抑制層12と、半導体基板2、不純物拡散抑制層12、および結晶層13内のゲート電極15の両側に形成され、結晶層13内にエクステンション領域を有する、p導電型を有する第2の不純物を含むp型ソース・ドレイン領域17と、を有し、C含有Si系結晶は第2の不純物の拡散を抑制する機能を有し、第1の不純物は、C含有Si系結晶内の固定電荷の発生を抑制する機能を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極とコンタクト配線のショート不良を防止できる半導体装置の製造方法を提供する。

【解決手段】半導体基板32上にゲートハードマスク、ゲート電極34及びゲート絶縁膜33を形成する。ゲートハードマスクの線幅をゲート電極よりも狭くした後、S/Dエクステンション36を形成する。全面にシリコン酸化膜を堆積形成し、エッチバックしてゲート電極の側壁から上面の一部上に渡って連続的に残存させた絶縁部材37を形成する。ゲートハードマスクを除去した後、ゲート電極と絶縁部材をマスクにしてコンタクトジャンクション38を形成する。金属シリサイド膜を形成後、シリコン窒化膜40と層間絶縁膜41を順次堆積形成する。層間絶縁膜にコンタクトホールを形成し、続いてシリコン酸化膜との選択比が高い異方性エッチングによってシリコン窒化膜を除去することでコンタクトホールを開孔し、コンタクト配線43を形成する。

(もっと読む)

熱処理方法、半導体装置の製造方法、及びフラッシュランプアニール装置

【課題】 熱処理方法、半導体装置の製造方法、及びフラッシュランプアニール装置に関し、紫外線照射による絶縁膜/半導体界面における水素で終端されたダングリング・ボンドからの水素の乖離を抑制する。

【解決手段】 加熱源となるXeフラッシュランプの放出光を、前記放出光の内の紫外線の少なくとも一部を除去した状態で酸素を含む絶縁膜とSiを含む半導体基体との界面を有する試料に照射して熱処理を行う。

(もっと読む)

161 - 180 / 952

[ Back to top ]