Fターム[5F140BG34]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート電極の形成処理 (7,666) | 熱処理 (1,248) | シリサイド化 (1,065)

Fターム[5F140BG34]の下位に属するFターム

雰囲気 (113)

Fターム[5F140BG34]に分類される特許

141 - 160 / 952

半導体装置の製造方法

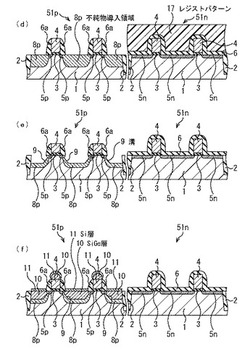

【課題】微細化が進んでも適切な歪を生じさせることができる半導体装置の製造方法を提供する。

【解決手段】nチャネルトランジスタ形成予定領域51nを覆う部分を残しながら絶縁膜6のエッチバックを行うことにより、pチャネルトランジスタ形成予定領域51p内のゲート電極4の側方にサイドウォール6aを形成する。サイドウォール6aをマスクとして半導体基板1の表面にp型不純物を導入してp型不純物導入領域8pを形成し、サイドウォール6aをマスクとしてp型不純物導入領域8pの表面に溝9を形成する。溝9内にSiGe層10を成長させる。絶縁膜6のエッチバックを行うことにより、nチャネルトランジスタ形成予定領域51n内のゲート電極4の側方にサイドウォールを形成し、nチャネルトランジスタ形成予定領域51n内において、このサイドウォールをマスクとして半導体基板1の表面にn型不純物を導入してn型不純物導入領域を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、最適な仕事関数を有するメタルゲート電極を持つ半導体装置及びその製造方法に関する。

【解決手段】n チャネルMIS トランジスタを含む半導体装置であり、n チャネルMIS トランジスタは、基板上に形成されたp 型半導体領域、p 型半導体領域に形成されたソース領域102及びドレイン領域104、ソース領域102及びドレイン領域104間のp 型半導体領域上に形成されたゲート絶縁膜106、ゲート絶縁膜106上に形成された金属層108及び化合物層110からなる積層構造を持つゲート電極を有する。金属層108は2 nm未満の厚さ及び4.3 eV以下の仕事関数を有し、化合物層110は4.4 eVを越える仕事関数を有しかつAl及び金属層108とは異なる金属を含んでいる。

(もっと読む)

半導体装置の製造方法

【課題】工程増を招くことなく、極めて高い歩留まりでゲート電極について均一で十分なフル・シリサイド化を確実に実現する。

【解決手段】ゲート電極104a,104b及びソース/ドレイン領域107a,107bのNiシリサイド化を行うに際して、1回目のNiシリサイド化の後に1回目のmsecアニール処理であるフラッシュランプアニール処理を行い、2回目のNiシリサイド化、更には必要であれば2回目のフラッシュランプアニール処理を行って、ソース/ドレイン領域107a,107b上には1回目のフラッシュランプアニール処理で形成されたNiSi層111bを維持した状態で、フル・シリサイドゲート電極115a,115bを形成する。

(もっと読む)

半導体装置の製造方法

【課題】チャネルに大きな歪を生じさせることができ、制御を容易に行うことができる半導体装置の製造方法を提供する。

【解決手段】半導体基板1上に、絶縁膜3、多結晶シリコン膜4及びアモルファスシリコン膜5を含む積層体を、ゲート電極の平面形状に形成する。多結晶シリコン膜4及びアモルファスシリコン膜5の側方にサイドウォール6を形成する。サイドウォール6をマスクとして半導体基板1の表面にp型不純物を導入して不純物導入領域7を形成する。サイドウォール6をマスクとして不純物導入領域7の表面に溝8を形成する。溝8内にSiGe層9を選択成長させる。アモルファスシリコン膜5を選択的に除去して、多結晶シリコン膜4を露出する。多結晶シリコン膜4上に導電層11を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】pMOSトランジスタにcSiGeとeSiGeを適用し、且つゲート絶縁膜におけるダメージ発生を防止でき、素子特性の向上及びしきい値制御性の向上をはかる。

【解決手段】pMOSトランジスタのチャネル部及びソース・ドレイン領域にSiGeを用いた半導体装置において、Si基板202上の一部に形成され、pMOSトランジスタのチャネルとなる第1のSiGe層205と、第1のSiGe層205上にゲート絶縁膜206を介して形成されたゲート電極208と、pMOSトランジスタのソース・ドレイン領域に埋め込み形成され、且つチャネル側の端部が基板表面よりも深い位置でチャネル側に突出するように形成された第2のSiGe層214と、第1のSiGe層205と第2のSiGe層214とを分離するように、基板の表面部でSiGe層205,214間に挿入されたSi層222とを備えた。

(もっと読む)

半導体装置およびその製造方法

【課題】ソース・ドレイン領域にエピタキシャル結晶を含み、エピタキシャル結晶上の金属シリサイドに起因する接合リークの発生を抑えた半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置1は、ファセット面13fを有するエピタキシャル結晶層13を有するMISFET10と、MISFET10を他の素子から電気的に分離し、上層3aのゲート電極12側の端部の水平方向の位置が下層3bのそれよりもゲート電極12に近く、上層3aの一部がファセット面13fに接する素子分離絶縁膜3と、エピタキシャル結晶層13の上面、およびファセット面13fの上層3aとの接触部よりも上側の領域に形成されたシリサイド層18と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】歪みの高いキャリア移動領域における寄生抵抗及びエネルギー障壁を小さくするための半導体装置を提供する。

【解決手段】半導体基板1上にゲート絶縁膜7を介して形成されたゲート電極13bと、半導体基板1のうちゲート電極13bの下方に形成されるチャネル領域6cと、チャネル領域6cの両側方に形成され、第1炭素濃度で炭素を含み、第1リン濃度でリンを含む第1の炭化シリコン層23と、第1の炭化シリコン層23上にチャネル領域6cに接合して形成され、第1リン濃度より多い第2リン濃度でリンを含み、第1炭素濃度以下の第2炭素濃度で炭素を含む第2の炭化シリコン層24とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル領域に印加される応力分布のピークとソース領域近傍に発生する電位分布のピークの位置を最適化することで、キャリア速度を向上させて飽和電流特性を向上させることを可能にする。

【解決手段】半導体基板11に形成されたチャネル領域12と、前記チャネル領域12の一方側に形成されたソース領域19と、前記チャネル領域12の他方側に形成されたドレイン領域20と、前記チャネル領域12上にゲート絶縁膜13を介して形成されたゲート電極14と、前記チャネル領域12に応力を印加する第1、第2応力導入層21、23を有し、前記チャネル領域12と前記ソース領域19とのpn接合境界と、前記チャネル領域12と前記ドレイン領域20とのpn接合境界の間に、前記ソース領域19側の応力分布のピークと前記ドレイン領域20側の応力分布のピークが位置する。

(もっと読む)

半導体装置及びその製造方法

【課題】PMISトランジスタのソースドレイン電極に高濃度のゲルマニウムを含むシリコンゲルマニウム層を用いても、シリコンゲルマニウム層に格子緩和を生じさせることなく、ソースドレイン電極の上部にシリコン層又は金属シリサイド層を形成できるようにする。

【解決手段】半導体装置は、n型半導体領域100の上にゲート絶縁膜101を介在させて形成されたゲート電極102と、その両側方に形成されたp型のソースドレイン電極150とを有している。ソースドレイン電極150は、n型半導体領域100に設けられた各リセス部100aに、その底部から少なくともチャネル領域の深さにまで形成されたシリコンゲルマニウム層111と、その上に形成され、炭素とシリコンゲルマニウム層のゲルマニウム濃度よりも低いゲルマニウムとを含むカーボンドープドシリコンゲルマニウム層112と、その上に形成された金属シリサイド層115とから構成される。

(もっと読む)

半導体装置およびその製造方法

【課題】メタルゲート電極を有するpチャネル型電界効果トランジスタにおいて、所望するしきい値電圧を安定して得ることのできる技術を提供する。

【解決手段】半導体基板1上に形成されたHfSiON膜からなるゲート絶縁膜5h上に、Me−O−Al−O−Me結合を含むMe1−xAlxOy(0.2≦x≦0.75、0.2≦y≦1.5)組成の導電性膜を一部に有するメタルゲート電極6、またはMe−O−Al−N−Me結合を含むMe1−xAlxN1−zOz(0.2≦x≦0.75、0.1≦z≦0.9)組成の導電性膜を一部に有するメタルゲート電極6を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】素子分離構造の面積を増大させることなく、素子分離構造の表面の後退量を低減させる。

【解決手段】半導体基板11の表面よりも低い位置に埋め込み絶縁層12を埋め込み、埋め込み絶縁層12と材料の異なるキャップ絶縁層13を半導体基板11と埋め込み絶縁層12と間の段差12aの肩の部分にかからないようにして埋め込み絶縁層12上に形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】基板上にヒューズ素子を備える半導体装置において、ヒューズを切断しやすくし、かつヒューズ切断状態を確実に得る。

【解決手段】半導体装置1は、基板10上に、MIPS構造を有するMOSトランジスタとヒューズ素子100を備える。ヒューズ素子100は、基板10の上に設けられた金属膜28と、金属膜28の上に設けられた絶縁膜30と、絶縁膜30の上に設けられたシリコン層34と、シリコン層34の上の少なくとも一部を覆うシリサイド層73と、からなる。

(もっと読む)

半導体装置の製造方法

【課題】 トランジスタのスイッチング速度低下を防止することが可能な半導体装置の製造方法を提供する。

【解決手段】 本発明では、半導体基板100上にゲート絶縁膜104を形成する工程と、ゲート絶縁膜104上に金属膜107を形成する工程と、金属膜107上に金属シリコン化合物膜108を連続して堆積する工程と、金属シリコン化合物膜108上にシリコン膜110を形成する工程と、金属膜107、金属シリコン化合物膜108及びシリコン膜110を加工する工程と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】所望のMOSトランジスタのみにチャネル領域に引っ張り応力を印加してキャリア移動度を向上させ、且つ、製造工程の複雑化を抑える。

【解決手段】シリコン基板10上にnMOSトランジスタのゲート絶縁膜13およびゲート電極14を非単結晶シリコンで形成し、ゲート電極14をマスクとして例えばAsやSb等の比較的質量数が大きい(質量数70以上)n型ドーパントを注入することで、nMOSトランジスタのソースドレイン領域を形成する。それにより、ゲート電極14は非晶質化する。そして、ゲート電極14が再結晶化する温度(約550℃)以下の温度条件でゲート電極14を覆うようにシリコン酸化膜40を形成し、その後1000℃程度の加熱処理を行う。それにより、ゲート電極14内に強い圧縮応力が残留すると共に、その下のチャネル領域には強い引っ張り応力が印加され、当該nMOSトランジスタのキャリア移動度は向上する。

(もっと読む)

半導体装置及びその製造方法

【課題】高い仕事関数及び高温安定性を備えたメタルゲートを有する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上に形成されたゲート誘電体層108と、ゲート誘電体層108上に形成された酸素を含む合金層110と、酸素を含む合金層110上に形成されたRe層112と、ゲート誘電体層108と酸素を含む合金層110との間に位置するRe酸化物層502を含むp 型電界効果トランジスタを具備する。

(もっと読む)

半導体装置の製造方法

【課題】短いゲート長を加工可能にする半導体装置の製造方法を提供すること。

【解決手段】半導体装置の製造方法の一形態は、シリコン基板2上にシリコン酸化膜34を形成し、酸化膜34上に所定幅T1を有する多結晶シリコン膜35aを形成し、少なくとも多結晶シリコン膜35aの両側部を酸化し、所定幅T1よりも狭い幅を有する酸化膜34の部分を多結晶シリコン膜35aの下に残すように、酸化膜34を、多結晶シリコン膜35aの酸化された部分と共にエッチングし、酸化された部分がエッチングされた多結晶シリコン膜35aをマスクとして、多結晶シリコン膜35aの両側のシリコン基板2の部分に不純物をイオン注入し、多結晶シリコン膜35aの両側に側壁絶縁膜14を形成し、側壁絶縁膜14が形成された多結晶シリコン膜35aをマスクとして、多結晶シリコン膜35aの両側のシリコン基板2の部分に不純物をイオン注入する、工程を有する。

(もっと読む)

半導体装置の製造方法

【課題】複数の同種の製造装置を用いて半導体装置を製造する場合に、製品間での寸法のばらつきの発生を抑制できる技術を提供する。

【解決手段】制御機器CDをそれぞれの露光機に対して個別に配置する。露光処理が完了した各ロットは、どの露光機で露光処理がなされたかによって分類され、露光機毎に、露光機を調整するためのパラメータが製品情報収集部CD1に収集され、最適製造条件計算部CD2にて処理条件が計算され、計算された処理条件が設定される。すべてのロットは、露光処理を行う露光機が予め割り当てられ、露光処理が済んでいないロットは、分類機CMによって割り当てられた露光機へ振り分けられ、制御機器CDによって求められた処理条件で露光処理が行われる。

(もっと読む)

MOSトランジスタ及びMOSトランジスタを備えた半導体装置の製造方法

【課題】縦型トランジスタにおいて、柱状半導体層上部のシリサイドの細線効果を低減すること、また、シリサイドと上部拡散層間の界面抵抗を低減することによりトランジスタ特性を改善すること、またコンタクトとゲート間のショートが発生しない構造を実現すること。

【解決手段】柱状半導体層と、前記柱状半導体層の底部に形成される第1のドレイン又はソース領域と、該柱状半導体層の側壁を包囲するように第1の絶縁膜を介して形成されるゲート電極と、前記柱状半導体層上面上部に形成されるエピタキシャル半導体層とを含み、前記第2のソース又はドレイン領域が少なくとも前記エピタキシャル半導体層に形成され、前記第2のソース又はドレイン領域の上面の面積は、前記柱状半導体層の上面の面積よりも大きいことを特徴とするMOSトランジスタ。

(もっと読む)

半導体デバイスとその形成方法(高k金属ゲートCMOS)

【課題】 金属酸化膜半導体電界効果トランジスタ内にデバイス性能を改善するゲート構造体を提供する。

【解決手段】 基板のp型デバイス領域の上にGe含有層を形成することを含む、半導体デバイスを形成する方法が提供される。その後、基板の第2の部分内に第1の誘電体層が形成され、基板の第2の部分内の第1の誘電層及び基板の第1の部分の上を覆うように、第2の誘電体層が形成される。次に、基板のp型デバイス領域及びn型デバイス領域の上にゲート構造体を形成することができ、n型デバイス領域へのゲート構造体は希土類金属を含む。

(もっと読む)

半導体装置の製造方法

【課題】ソース、ドレインの低抵抗化及び寄生容量の低減化のための構造、所望のゲート長、ソース、ドレイン形状、柱状半導体の直径が得られるSGTの製造方法を提供する。

【解決手段】第1の平面状半導体層上に第1の柱状半導体層を形成する工程と、第1の柱状半導体層の下部と第1の平面状半導体層に第1の第2導電型半導体層を形成する工程と、第1の柱状半導体層の底部及び第1の平面状半導体層上に第1の絶縁膜を形成する工程と、第1の柱状半導体層の周囲にゲート絶縁膜およびゲート電極を形成する工程と、ゲート電極の上部且つ第1の柱状半導体層の上部側壁と、ゲート電極の側壁に第2の絶縁膜をサイドウォール状に形成する工程と、第1の第2導電型半導体層と第2の第2導電型半導体層との間に第1導電型半導体層を形成する工程と、第1の第2導電型半導体層の上部表面と、第2の第2導電型半導体層の上部表面に金属と半導体の化合物を形成する工程とを含む。

(もっと読む)

141 - 160 / 952

[ Back to top ]