Fターム[5F140BH27]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ソース、ドレイン領域及びSD近傍領域 (10,828) | ソース、ドレイン材料 (598)

Fターム[5F140BH27]の下位に属するFターム

多結晶 (39)

Fターム[5F140BH27]に分類される特許

541 - 559 / 559

半導体装置及びその製造方法

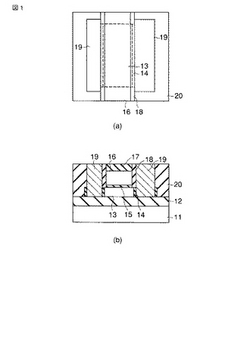

【課題】フェルミ・レベル・ピンニング効果を抑制するとともに、トランジスタの微細化を図ること。

【解決手段】シリコン基板または支持基板11上に形成された島状のチャネル層13と、チャネル層13上に形成されたゲート絶縁膜15と、ゲート絶縁膜15上に形成されたゲート電極16と、チャネル層13の一方向に対向する両側面上に形成されたシリコン窒化膜14と、シリコン窒化膜14の側面上に形成された金属材料からなるソース電極及びドレイン電極19とを具備する。

(もっと読む)

半導体素子及びその製造方法

【課題】素子の電流駆動力を向上させ、ショットチャンネル効果を改善させることができる半導体素子及びその製造方法を提供する。

【解決手段】本発明は、Si−エピ層20,120を食刻して下部の埋込絶縁膜50,200を露出させ、一側のLDD40,180領域から他側のLDD領域40,180まで互いに平行して延長される開口部140を1つ以上形成し、ゲート電極がSi−エピ層20,120の表面を取り囲むようにした。

(もっと読む)

シリサイド化金属ゲートの形成のための方法

【課題】シリサイド化金属ゲートと、シリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物と、同ゲート構造物を製造する方法と、を提供する。

【解決手段】シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を提供する。詳しくは、広義に、第一の厚さを有する第一のシリサイド金属のシリサイド化金属ゲートと、隣接する第二の厚さを有する第二の金属のシリサイド化ソース領域およびドレイン領域とを含み、第二の厚さは第一の厚さより薄く、シリサイド化ソース領域およびドレイン領域は少なくともシリサイド化金属ゲートを含むゲート領域の端に位置合わせした半導体構造物を提供する。さらに、シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を製造する方法も提供する。

(もっと読む)

トランジスタ形成方法

金属酸化膜トランジスタなどの半導体デバイスを基板上に形成する際に材料を堆積するための方法が提供される。一実施形態では、本発明は概して、第1の導電性を有する基板上にゲート誘電体を形成するステップと、該ゲート誘電体上にゲート電極を形成するステップと、該ゲート電極の横方向に対向する側壁に沿って第1の対の側壁スペーサを形成するステップと、該電極の対向する側に1対のソース/ドレイン領域限定部をエッチングするステップと、該ソース/ドレイン領域限定部にシリコンゲルマニウム材料を選択的に堆積するステップと、該堆積されたシリコンゲルマニウム材料にドーパントを注入して、第2の導電性を有するソース/ドレイン領域を形成するステップと、を含む基板を処理する方法を提供する。 (もっと読む)

半導体装置及びその製造方法

【課題】 製造工程を簡略化することができ、低抵抗のソース、ドレインを具備した高性能かつ高信頼性の薄膜トランジスタを有する半導体装置、その製造方法、薄膜トランジスタアレイ基板及び液晶表示装置を提供する。

【解決手段】 導電型が異なる薄膜トランジスタを含んで構成される半導体装置であって、上記薄膜トランジスタは、基板上に半導体層を形成し、この半導体層上にゲート絶縁膜を介してゲート電極を形成し、ゲート電極をマスクにして半導体層に低濃度の不純物を注入して導電型が異なる低濃度不純物領域をそれぞれ形成し、ゲート電極の側面にサイドウォールスペーサーを形成した後に、ソース、ドレイン領域のみに高濃度不純物層としてSiGeを選択的に形成し、一方の導電型の低濃度不純物領域上のSiGeにのみ高濃度不純物層中の不純物とは異なる他の不純物をドーピングし、低濃度不純物領域上に同じ導電型の高濃度不純物領域を形成したものである半導体装置。

(もっと読む)

メモリデバイス、トランジスタ、メモリセル並びにそれらの製造方法

メモリデバイスはメモリセルのアレイと周辺デバイスを含んでいる。少なくとも一部の個別メモリセルはSiCを含む炭酸化部分を含んでいる。少なくとも一部の周辺デバイスは炭酸化部分を含まない。トランジスタは第1ソース/ドレーン、第2ソース/ドレーン、第1ソース/ドレーンと第2ソース/ドレーンとの間にSiCを含む半導体基板の炭酸化部分を含んだチャンネル、及びチャンネルの両側と作動式に関係するゲートを含んでいる。 (もっと読む)

半導体装置およびCMOS集積回路装置

【課題】 nチャネルMOSトランジスタにおいてチャネル領域に大きな圧縮応力を基板面に垂直方向に印加して特性を向上させると同時に、pチャネルMOSトランジスタにおいて、かかる圧縮応力による特性の劣化を軽減する。

【解決手段】 前記ゲート電極を覆うように、応力を蓄積した応力蓄積絶縁膜が形成し、その際、前記応力蓄積絶縁膜のうち、前記ゲート電極を覆う部分の膜厚を、その外側の部分よりも増大させる。

(もっと読む)

ソース/ドレイン部分絶縁部を有する電界効果トランジスタ、および、その製造方法

本発明は、ソース/ドレイン部分絶縁部を備えた電界効果トランジスタ、および、その製造方法に関するものである。間隔の空いたソース凹部(SV)とドレイン凹部(DV)とを半導体基板(1)の中に形成し、ソース・ドレイン凹部(SV・DV)の少なくとも下部領域に、凹部絶縁層(VI)を形成し、上記ソース・ドレイン凹部(SV・DV)に、導電性充填層(F)を配置することにより、ソース・ドレイン領域(S・D)を形成する。したがって、接合容量が低減された電界効果トランジスタが、ゲート誘電体(3)およびゲート層(4)とともに得られる。  (もっと読む)

(もっと読む)

勾配付き組み込みシリコン−ゲルマニウムのソース−ドレイン及び/又は延長部をもつ、歪みP型MOSFETの構造及びこれを製造する方法

【課題】歪みシリコンをもつP型MOSFETの構造及びこれを製造する方法を提供する。

【解決手段】P型MOSFETは、ゲート110を絶縁体で封止し、ゲルマニウム含有層を側壁105の外側に成層させ、次いで、アニーリング又は酸化により、ゲルマニウムを絶縁体上シリコン層又はバルクシリコンの中に拡散させて、勾配付き組み込みシリコン−ゲルマニウムのソース−ドレイン40及び/又は延長部(geSiGe−SDE)を形成する。SOIデバイスにおいては、geSiGe−SDEは、水平方向の(ゲート誘電面に対して平行な)圧縮応力と、垂直方向の(該ゲート誘電面に対して直角の)引張り応力とをPMOSFETのチャネルに生成し、これによって、PMOSFET性能を向上させる構造を形成する。

(もっと読む)

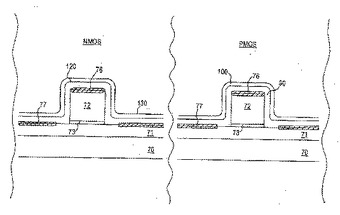

改良した歪みシリコンCMOSデバイスおよび方法

【課題】 デバイス・チャネルに一軸性歪みを生成してキャリア移動度を向上させた半導体デバイスを提供する。

【解決手段】 本発明は、半導体デバイスのデバイス・チャネルに一軸性歪みを生成する半導体デバイスおよびその形成方法を提供する。一軸性歪みは、引張り性または圧縮性とすることができ、デバイス・チャネルに平行な方向である。一軸性歪みは、歪み誘発ライナ、歪み誘発ウェル、またはそれらの組み合わせによって、二軸性歪み基板表面において生成することができる。一軸性歪みは、歪み誘発ウェルおよび歪み誘発ライナの組み合わせによって、緩和基板において生成することも可能である。また、本発明は、歪み誘発分離領域によって二軸性歪みを増大させるための手段も提供する。更に、本発明が提供するCMOSデバイスにおいては、CMOS基板のデバイス領域を別個に処理して、圧縮性または引張り性の一軸性歪み半導体表面を提供する。

(もっと読む)

半導体装置の製造方法

【課題】p型トランジスタの動作速度を高め、n型トランジスタとの動作速度の均衡がとれた半導体装置の製造方法を提供する。

【解決手段】p−MOS領域30aのソース/ドレイン領域にSiGe膜からなる圧縮応力印加部20を形成し、その後にp−MOS領域30aおよびn−MOS領域30bに不純物注入を行い、浅い接合領域22a、22bおよび深い接合領域23a、23bを形成する。SiGe膜を形成する際の加熱により浅い接合領域22a、22bの不純物がゲート絶縁膜15の直下に拡散することを防止し、短チャネル効果を防止すると共に、p−MOSトランジスタ13aのチャネル領域の正孔移動度を高め、n−MOSトランジスタ13bの動作速度との均衡により、相補型の半導体装置10の総合的な動作速度を高める。

(もっと読む)

半導体装置とその製造方法、及び半導体装置の評価方法

【課題】 チャネルに応力が印加されるMOSトランジスタの特性のばらつきを防ぐことができる半導体装置とその製造方法を提供すること、及び、MOSトランジスタのチャネルにおけるキャリア分布を直接測定することができる半導体装置の評価方法を提供すること。

【解決手段】 シリコン(半導体)基板10と、シリコン基板10の上に順に形成されたゲート絶縁膜13及びゲート電極14cと、ゲート電極14cの横のシリコン基板10のリセス(穴)10a、10bに形成されたソース/ドレイン材料層18a、18bと、を有し、リセス10a、10bのゲート電極14c寄りの側面10c、10dが、シリコン基板10の少なくとも一つの結晶面で構成されることを特徴とする半導体装置による。

(もっと読む)

インサイチュドープトエピタキシャルフィルム

インサイチュドープトエピタキシャル半導体層を堆積するための方法は、パターニングされた基板を収容する処理チャンバ内を約80torrより高圧に維持するステップを含む。本方法は更に、前記処理チャンバ内へジクロロシランのフローを提供するステップを含む。本方法は更に、前記処理チャンバ内へドーパント水素化物のフローを提供するステップを含む。本方法は更に、パターニングされた前記基板上の単結晶物質上に、約3nm min−1より速い速度で、前記エピタキシャル半導体層を選択的に堆積するステップを含む。  (もっと読む)

(もっと読む)

選択的堆積プロセスを使用したMOSFETデバイスの作製方法

本発明の実施形態により、高ドーパント濃度を含有するエピタキシャルシリコンゲルマニウム材料を選択的に堆積するなど、シリコン含有材料を堆積するためのプロセスが提供される。一実施例において、1つの層を別の層の上部に堆積するために、少なくとも2つの異なるプロセスガスに基板が曝される。1つのプロセスガスは、ジクロロシラン、ゲルマニウム源、およびエッチャントを含有し、次のプロセスガスは、シランおよびエッチャントを含有する。他の実施例において、プロセスガスが、ジクロロシラン、メチルシラン、および塩化水素、またはシラン、メチルシラン、および塩化水素を含有する。一態様において、堆積された層が、結晶格子内に格子間部位を有し、格子間部位内に約3at%以下の炭素を含有し、引き続き、結晶格子の置換部位内に炭素を包含するようにアニーリングされる。別の態様において、シリコンゲルマニウム積層体が、約25at%以下、約25at%以上、および約5at%以下のゲルマニウム濃度を含有する第1、第2、および第3の層を有する。 (もっと読む)

チャネルキャリア移動度向上のための高応力ライナーを備えたSi−Geに基づく半導体デバイス

応力ライナーを用いることで、Si−Geデバイスのトランジスタのチャネル領域のキャリア移動度が増加される。一実施形態においては、緩和ソース/ドレイン領域を覆う高圧縮膜あるいは高引っ張り応力膜を適用する。他の実施形態としては、ポストシリサイドスペーサを除去した後、P−チャネルトランジスタあるいはN−チャネルトランジスタのゲート電極(72)および歪みソース/ドレイン領域(71)にそれぞれ、高圧縮応力膜(90)あるいは高引っ張り応力膜(120)を適用する。  (もっと読む)

(もっと読む)

III族窒化膜双方向スイッチ

【課題】電力用デバイスにおいて双方向に電圧をブロックできるようにする。

【解決手段】大電流を搬送するチャンネルを得るAlGaN/GaNインターフェースを備えたIII族窒化物双方向スイッチであり、この双方向スイッチは、この双方向スイッチのために、電流を搬送するチャンネルを形成するための二次元電子ガスの発生を阻止したり、または可能にする少なくとも1つのゲートにより作動する。

(もっと読む)

大量にドープされたエピタキシャルSiGeを選択的に堆積させる方法

一実施形態においては、基板上にシリコン膜又はシリコンゲルマニウム膜を堆積させる方法であって、プロセスチャンバ内に基板を配置するステップと、基板表面を約600℃〜900℃の範囲の温度に、プロセスチャンバ内の圧力を約13Pa(0.1トール)〜約27kPa(200トール)の範囲に維持しつつ、加熱するステップと、を含む前記が提供される。堆積ガスは、プロセスチャンバに供給され、SiH4、任意のゲルマニウム源ガス、エッチング剤、キャリヤガス、任意に少なくとも1つのドーパントガスを含んでいる。シリコン膜又はシリコンゲルマニウム膜は、基板上に選択的且つエピタキシャル的に成長する。一実施形態は、シリコン含有膜とキャリヤガスとして不活性ガスを堆積させる方法を含んでいる。方法は、また、選択的シリコンゲルマニウムエピタキシャル膜を用いる電子デバイスの製造を含んでいる。 (もっと読む)

等方性エッチングプロセスを使ったショットキーバリアMOSFET製造方法

【課題】電流の流れを調整するトランジスタデバイスの組立て方法において、更なる駆動電流を可能にし、デバイスの動作を最適化するプロセスを提供すること。

【解決手段】本発明の一実施形態における方法は、チャンネル領域に対するショットキーバリア接合位置のより良い制御を与えるために、メタルソースドレイン接触の形成に先行して等方性エッチングプロセスを利用する。このショットキーバリア10接合の配置の制御性からの改善により、更なる駆動電流を可能にし、デバイスの動作を最適化する。

(もっと読む)

格子不整合のソースおよびドレイン領域を有する歪み半導体CMOSトランジスタを有する集積回路および製作方法

【課題】 p型電界効果トランジスタ(PFET)およびn型電界効果トランジスタ(NFET)を有する集積回路を提供することにある。

【解決手段】 第1の歪みは、NFETではなくPFETのみのソースおよびドレイン領域内に配置されたシリコン・ゲルマニウムなどの格子不整合半導体層を介してNFETではなくPFETのチャネル領域に加えられる。PFETおよびNFETを形成するプロセスが提供される。PFETのソースおよびドレイン領域になるためのエリア内にトレンチがエッチングされ、それに隣接するPFETのチャネル領域に歪みを加えるために、格子不整合シリコン・ゲルマニウム層をそこにエピタキシャル成長させる。シリコン・ゲルマニウム層の上にシリコンの層を成長させ、シリコンの層からサリサイドを形成して、低抵抗ソースおよびドレイン領域を提供することができる。

(もっと読む)

541 - 559 / 559

[ Back to top ]