Fターム[5F140CC08]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 層間膜、保護膜 (4,863) | 材料 (2,741) | SiN (860)

Fターム[5F140CC08]に分類される特許

841 - 860 / 860

半導体装置およびその製造方法

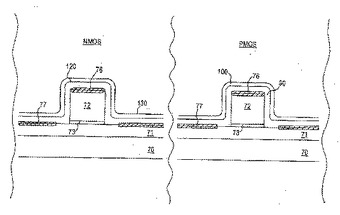

【課題】 メタルゲート及びhigh-kゲート絶縁膜を有するCMOSにおいて、nMOS及びpMOSトランジスタの低しきい値化を実現する。

【解決手段】 n型MISFET形成領域11のゲート絶縁膜3aはHfO2膜であり、メタルゲート電極4aは、TiN膜と、ゲート絶縁膜との界面に生成されたにゲート電極に含まれるIV族遷移金属と酸素を含むがシリコンは含まない界面層とからなり、その仕事関数はn型MISFETのゲート電極材料に適した4.0〜4.2eVである。p型MISFET形成領域12のゲート絶縁膜3bはHfSiO2/HfO2であり、メタルゲート電極4bはTiNと、ゲート絶縁膜との界面に形成されたにゲート電極に含まれるIV族遷移金属と酸素および金属的シリコン(Si0)からなる界面層とからなり、その仕事関数は、p型MISFETのゲート電極材料に適した4.9eVとなっている。

(もっと読む)

半導体装置およびCMOS集積回路装置

【課題】 nチャネルMOSトランジスタにおいてチャネル領域に大きな圧縮応力を基板面に垂直方向に印加して特性を向上させると同時に、pチャネルMOSトランジスタにおいて、かかる圧縮応力による特性の劣化を軽減する。

【解決手段】 前記ゲート電極を覆うように、応力を蓄積した応力蓄積絶縁膜が形成し、その際、前記応力蓄積絶縁膜のうち、前記ゲート電極を覆う部分の膜厚を、その外側の部分よりも増大させる。

(もっと読む)

半導体装置およびその製造方法

【課題】熱負荷をより小さく抑えて下地への影響なく成膜可能であると共に、十分に引っ張り応力を維持可能でかつパーティクルの発生を抑えた膜質良好な窒化シリコン膜によってMOSトランジスタを覆うことにより、トランジスタ特性の向上を図ることが可能な半導体装置およびこの半導体装置の製造方法を提供する。

【解決手段】半導体基板1の表面側に形成されたMOSトランジスタ11を覆う状態で窒化シリコン膜13が設けられた半導体装置において、窒化シリコン膜13は、両側の界面層における窒素濃度が中央部分の窒素濃度よりも高いことを特徴としている。窒化シリコン膜の界面層における窒素濃度は、化学量論的組成よりも高いことが好ましい。

(もっと読む)

半導体装置の製造方法

【課題】 安定した低抵抗のシリサイド膜を形成する技術を提供する。

【解決手段】 半導体基板1上にゲート絶縁膜5を形成する工程、ゲート絶縁膜5上にシリコン膜7を形成する工程、シリコン膜7と半導体基板1との表面にBF2イオンおよびBイオンを注入し、pチャネル型MISトランジスタQpのゲート電極11pと高濃度n型半導体領域15からなるソース/ドレインとを形成する工程、ゲート電極11pの上部に第1コバルトシリサイド膜を形成し、ソース/ドレインの上部に第2コバルトシリサイド膜を形成する工程を有する。

(もっと読む)

半導体装置

【課題】 高電圧駆動のMISトランジスタを有する半導体装置であって、耐圧の向上と、微細化の向上が図られた半導体装置を提供する。

【解決手段】 本発明の半導体装置は、半導体層10と、

前記半導体層10の上方に設けられたゲート絶縁層20と、

前記ゲート絶縁層20の上方に設けられたゲート電極22と、

前記半導体層10に設けられたソース領域またはドレイン領域となる不純物領域28a,bと、

前記ゲート電極22と電気的に接続されたフィールドプレート電極44と、

前記フィールドプレート電極44を覆う絶縁層と、を含み、

前記絶縁層は、比誘電率が異なる領域を有し、比誘電率が高い領域は、前記導電層の一の端部に接している。

(もっと読む)

半導体装置

【課題】

酸化シリコン層、窒化シリコン層の積層ライナを備えたSTIを有し、帯電を低減できる半導体装置およびその製造方法を提供する。

【解決手段】

半導体装置は、シリコン基板と、前記シリコン基板の表面から下方に向かって形成され、前記シリコン基板の表面に活性領域を画定するトレンチと、前記トレンチの内壁を覆う酸化シリコン層の第1ライナ層と、前記第1ライナ層の上に形成された窒化シリコン層の第2ライナ層と、前記第2ライナ層の上に形成され、前記トレンチを埋める絶縁物の素子分離領域と、前記活性領域に形成されたpチャネルMOSトランジスタと、前記pチャネルMOSトランジスタを覆って,前記シリコン基板上方に形成され,紫外光遮蔽能を有さない窒化シリコン層のコンタクトエッチストッパ層と、前記コンタクトエッチストッパ層の上方に形成され、紫外光遮蔽能を有する窒化シリコン層の遮光膜と、を有する。

(もっと読む)

改良した歪みシリコンCMOSデバイスおよび方法

【課題】 デバイス・チャネルに一軸性歪みを生成してキャリア移動度を向上させた半導体デバイスを提供する。

【解決手段】 本発明は、半導体デバイスのデバイス・チャネルに一軸性歪みを生成する半導体デバイスおよびその形成方法を提供する。一軸性歪みは、引張り性または圧縮性とすることができ、デバイス・チャネルに平行な方向である。一軸性歪みは、歪み誘発ライナ、歪み誘発ウェル、またはそれらの組み合わせによって、二軸性歪み基板表面において生成することができる。一軸性歪みは、歪み誘発ウェルおよび歪み誘発ライナの組み合わせによって、緩和基板において生成することも可能である。また、本発明は、歪み誘発分離領域によって二軸性歪みを増大させるための手段も提供する。更に、本発明が提供するCMOSデバイスにおいては、CMOS基板のデバイス領域を別個に処理して、圧縮性または引張り性の一軸性歪み半導体表面を提供する。

(もっと読む)

半導体装置

【課題】

活性領域と素子分離領域を別個の対象として応力を制御し,半導体装置の性能を向上する。

【解決手段】

半導体装置は、p−MOS領域を有する半導体基板と、半導体基板表面部に形成され、p−MOS領域内にp−MOS活性領域を画定する素子分離領域と、p−MOS活性領域を横断して,半導体基板上方に形成され、下方にp−MOSチャネル領域を画定するp−MOSゲート電極構造と、p−MOSゲート電極構造を覆って、p−MOS活性領域上方に選択的に形成された圧縮応力膜と、p−MOS領域の素子分離領域上方に選択的に形成され,圧縮応力膜の応力を解放している応力解放領域と、を有し、p−MOSチャネル領域にゲート長方向の圧縮応力とゲート幅方向の引張応力を印加する。

(もっと読む)

ドープ窒化膜、ドープ酸化膜、およびその他のドープ膜

【課題】一般に、半導体デバイスの製造に使用される被膜、特に窒化被膜および酸化被膜を提供すること。

【解決手段】窒化シリコン、酸化シリコン、酸窒化シリコン、または炭化シリコン被膜の形成中、少なくとも1つの非シリコン前駆体(ゲルマニウム前駆体や炭素前駆体など)を添加することによって、堆積速度が改善され、または被膜の応力を調整するなどこの被膜の特性を調整することが可能になり、あるいはその両方が可能になる。また、ドープ型酸化シリコンまたはドープ型窒化シリコンまたはその他のドープ型構造では、ドーパントが存在することを利用して、このドーパントに関連する信号(目印)をエッチング・ストップとして測定することができ、またはその他の場合にはエッチング中の制御を実現することができる。

(もっと読む)

半導体装置とその製造方法、及び半導体装置の評価方法

【課題】 チャネルに応力が印加されるMOSトランジスタの特性のばらつきを防ぐことができる半導体装置とその製造方法を提供すること、及び、MOSトランジスタのチャネルにおけるキャリア分布を直接測定することができる半導体装置の評価方法を提供すること。

【解決手段】 シリコン(半導体)基板10と、シリコン基板10の上に順に形成されたゲート絶縁膜13及びゲート電極14cと、ゲート電極14cの横のシリコン基板10のリセス(穴)10a、10bに形成されたソース/ドレイン材料層18a、18bと、を有し、リセス10a、10bのゲート電極14c寄りの側面10c、10dが、シリコン基板10の少なくとも一つの結晶面で構成されることを特徴とする半導体装置による。

(もっと読む)

半導体装置

【課題】 バイポーラトランジスタにおける高利得化および低雑音化を同時に実現できる技術を提供する。

【解決手段】 ベースパッド31およびコレクタパッド32の下部にエミッタ(基準(接地)電位)と電気的に接続された配線24が設けられた基板シールド構造とすることにより、ベースパッド31およびコレクタパッド32と配線24との間では容量が設けられた構造として電力消費をなくし、基板1からの熱雑音は、配線24を介して基準(接地)電位へと逃がし、ベースパッド31およびコレクタパッド32へは届かないようにする。

(もっと読む)

半導体構造、メモリ素子構造、及び半導体構造の形成方法

本発明は、垂直のソース/ドレイン領域(88)を囲むゲート線格子(94)を有する半導体構造(10)を含む。ある側面では、ソース/ドレイン領域は、ペアで提供され、各ペアのソース/ドレイン領域のうちの1つがディジットライン(120、122)に延伸し、もう1つのソース/ドレイン領域がキャパシタのようなメモリストレージ素子(145)に延伸してDRAMを形成することができる。ディジットラインに延伸するソース/ドレイン領域は、メモリストレージ素子(145)に延伸するソース/ドレイン領域とは同じ組成、または異なる組成を有することができる。本発明はさらに半導体構造を形成する方法を含む。典型的な方法では、第1の材料を含む格子は第2の材料の繰り返し領域を囲むように提供される。その後、前記第1の材料のうちの少なくとも一部はゲート線構造で置換去れ、また、本発明のうちの少なくとも一部は、垂直のソース/ドレイン領域を囲むゲート線格子を有する半導体構造を含む。ある側面では、ソース/ドレイン領域はペアで提供され、各ペアのソース/ドレイン領域のうちの1つはディジットラインまで延伸し、もう1つのソース/ドレイン領域はキャパシタのようなメモリストレージ素子まで延伸することができる。ディジットラインに延伸するソース/ドレイン領域は、メモリストレージ素子に延伸するソース/ドレイン領域とは同じ組成、または異なる組成を有することができる。本発明はさらに、第1の材料を含む格子が第2の材料の繰り返し領域を囲むように提供される方法を含む。その後、第1の材料のうちの少なくとも一部はゲート線構造で置換去れ、また、第2の材料のうちの少なくとも一部は垂直のソース/ドレイン領域で置換される。  (もっと読む)

(もっと読む)

チャネルキャリア移動度向上のための高応力ライナーを備えたSi−Geに基づく半導体デバイス

応力ライナーを用いることで、Si−Geデバイスのトランジスタのチャネル領域のキャリア移動度が増加される。一実施形態においては、緩和ソース/ドレイン領域を覆う高圧縮膜あるいは高引っ張り応力膜を適用する。他の実施形態としては、ポストシリサイドスペーサを除去した後、P−チャネルトランジスタあるいはN−チャネルトランジスタのゲート電極(72)および歪みソース/ドレイン領域(71)にそれぞれ、高圧縮応力膜(90)あるいは高引っ張り応力膜(120)を適用する。  (もっと読む)

(もっと読む)

複数の狭区画レイアウトを用いたひずみデバイス

大きな引張応力を有する半導体デバイスを提供することを目的とする。半導体デバイスは、ソース領域及びドレイン領域を備える基板を有する。ソース領域及びドレイン領域の各々は、それぞれ、複数の分離されたソース区画及びドレイン区画を含む。シャロートレンチ分離(STI)領域がソース領域の2つの分離されたソース区画間及びドレイン領域の2つの分離されたドレイン区画間に形成される。ゲート積層体が基板に形成される。引張誘起層が基板上に形成される。引張誘起層はSTI領域、ソース領域、ドレイン領域及びゲート積層体を覆っている。引張誘起層は基板に引張応力を生じさせることが可能な絶縁体である。

(もっと読む)

(もっと読む)

pFET中のボロン拡散係数の減少方法

半導体材料の構造物または本体(例えば基板または層)によって定められる境界を横切って加えられる応力を受ける膜は、境界の近傍の半導体材料中に引張り応力から圧縮応力への変化を提供し、アニーリングの間のホウ素拡散速度を変化させ、ひいては最終ホウ素濃度またはプロフィル/勾配あるいはその両方を変化させるために用いられる。電界効果トランジスターの場合、側壁の有無にかかわらず、ソース/ドレイン、拡張注入部またはハロ注入部、あるいはその両方に対する境界の位置を調節するために、ゲート構造物を形成させることができる。水平方向と垂直方向とで異なるホウ素拡散速度を作り出すことができ、ヒ素と同程度の拡散速度を実現することができる。同じプロセス工程で、nFETとpFETとの両方の接合キャパシタンスの減少を同時に実現することができる。

(もっと読む)

(もっと読む)

半導体装置および半導体集積回路装置

pチャネルMOSトランジスタおよびnチャネルMOSトランジスタの各々においてチャネル方向を<100>方向に設定し、STI型素子分離構造に、引っ張り応力を蓄積した第1の応力補償膜を形成し、さらにシリコン基板上に素子分離構造を覆うように引っ張り応力を蓄積した第2の応力補償膜を形成する。 (もっと読む)

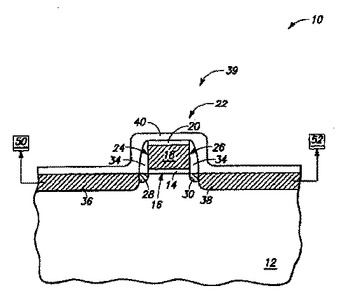

分離領域を有する半導体デバイスを形成するための方法

分離構造を有する半導体デバイス(10)を形成するための方法が漏れ電流を低減する。チャネル分離構造(32、30、34)がチャネル構造の中の漏れ電流を低減する。さらに、電流電極領域の下に電流電極誘電体分離構造(36)が形成され、電流電極(40)間の漏れを防ぐ。  (もっと読む)

(もっと読む)

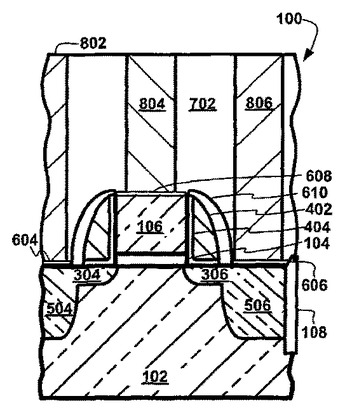

集積回路技術におけるシリサイド化スペーサ

集積回路(100)の形成方法(900)およびその構造を提供する。半導体基板(102)上にゲート誘電体(104)が形成され、ゲート誘電体(104)上にゲート(106)が形成される。半導体基板(102)に浅いソース/ドレイン接合部(304)(306)が形成される。ゲート(106)の周りに側壁スペーサ(402)を形成する。この側壁スペーサ(402)を使用して、半導体基板(102)中に深いソース/ドレイン接合部(504)(506)が形成される。浅いソース/ドレイン接合部および深いソース/ドレイン接合部(504)(506)を形成した後、側壁スペーサ(402)上にシリサイドスペーサ(610)を形成する。シリサイドスペーサ(610)に隣接する深いソース/ドレイン接合部(504)(506)上にシリサイド(604)(606)を形成し、半導体基板(102)上に誘電体層(702)をたい積する。その後、誘電体層(702)においてシリサイド(604)(606)へのコンタクトを形成する。  (もっと読む)

(もっと読む)

集積回路技術における超均一シリサイド

集積回路(100)の形成方法(900)およびその構造体が提供される。半導体基板(102)上にゲート誘電体(104)が形成され、半導体基板(102)上のゲート誘電体(104)上にゲート(106)が形成される。半導体基板(102)にソース/ドレイン接合部(504/506)が形成される。ソース/ドレイン接合部(504/506)上に超均一シリサイド(604/608)が形成され、半導体基板(102)の上方に誘電体層(702)が堆積される。次いで、誘電体層(702)に、超均一シリサイド(604/608/606)へのコンタクトが形成される。  (もっと読む)

(もっと読む)

ジュウテリウム置換窒化珪素含有材料の作製方法

少なくとも1種のジュウテリウム置換窒素化合物と水素同位体を含まない1または2以上の珪素含有化合物からのジュウテリウム置換窒化珪素含有材料作製方法を提供する。適するジュウテリウム置換窒素化合物として例えばNH2D、NHD2及びND3を用い、適する珪素含有化合物として例えばSiCl4及びSi2Cl6を用いる。本発明に従って得られるジュウテリウム置換窒化珪素含有材料は例えばトランジスタ装置中へ組み入れることができ、これにより得られたトランジスタ装置をDRAMセル中に用い、さらに得られたDRAMセルを電子システム中に用いることができる。

(もっと読む)

(もっと読む)

841 - 860 / 860

[ Back to top ]