Fターム[5F140CC10]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 層間膜、保護膜 (4,863) | 材料 (2,741) | 有機物 (55)

Fターム[5F140CC10]に分類される特許

1 - 20 / 55

半導体装置およびその製造方法

半導体装置

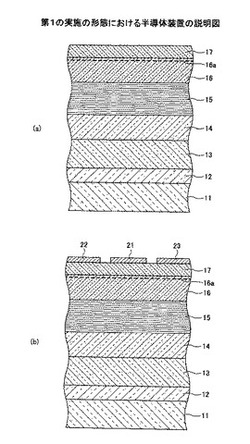

【課題】電子走行層にFeが入り込むことを抑制し、半導体層等にクラックの発生が抑制される電界効果型トランジスタを提供する。

【解決手段】基板11の上に形成された半導体材料に高抵抗となる不純物元素がドープされた高抵抗層14と、高抵抗層14の上に形成された多層中間層15と、多層中間層15の上に半導体材料により形成された電子走行層16と、電子走行層の上に半導体材料により形成された電子供給層17と、を有し、多層中間層15は、GaN層とAlN層とが交互に積層された多層膜により形成されていることを特徴とする半導体装置。

(もっと読む)

電界効果トランジスタ

【課題】ゲート電極とソース電極との間に印加される電圧がソース電極パッドの電気抵抗による電圧降下で低下することを防止でき、安定した動作を実現できる電界効果トランジスタを提供する。

【解決手段】このGaN HFETによれば、ボンディング部16Bの第2のパッド部16B‐2は、電極接続部16Aが含有する複数の接続部分19のうちの第2の方向(ソース電極12とドレイン電極11が対向している方向)の一端に配置された接続部分19の上記第2の方向の外端を電極延在方向へ延長した仮想延長線L1に関して第1のパッド部16B‐1とは反対側に位置している。第2のパッド部16B‐2に接続された第2のソース配線24のボンディング箇所の第2の方向の位置を電極接続部16Aのソース電極12との接続部分19の第2の方向の位置と重ならないようにして、ソース電極12からの電流が第2のソース配線24に流れにくくできる。

(もっと読む)

テラヘルツ波素子

【課題】テラヘルツ波を発生又は検出するテラヘルツ波素子において、単色性が良いテラヘルツ波を効率良く出射する。

【解決手段】テラヘルツ波素子は、基板101の上に形成された第1の半導体層102と、第1の半導体層102の上に形成された第2の半導体層104と、第2の半導体層104の上に形成されたゲート電極106と、第2の半導体層104の上にゲート電極106を挟んで対向するように形成されたソース電極107及びドレイン電極108と、第2の半導体層104の上におけるゲート電極106とソース電極107との間及びゲート電極106とドレイン電極108との間に形成され、複数の金属膜109が周期的に配置された周期構造を有する周期金属膜109A,109Bと、ゲート電極106及び複数の金属膜109の上方に配置された第1のミラー111と、基板101の下に形成された第2のミラー112とを備えている。

(もっと読む)

半導体装置およびその製造方法

【課題】リセスの下部に形成され不純物の注入量が異なる複数の領域を備える電界緩和層(リサーフ層)を備える半導体装置において、製造工程数の増加を抑えつつ、ディッシングの発生を防止する。

【解決手段】半導体装置は、半導体素子の外周領域であるPウェル2の外縁部に形成されたP型のリサーフ層10を備える。リサーフ層10は、P型不純物が第1面密度で注入された第1リサーフ領域11と、第1リサーフ領域11の外側に配設され、P型不純物が第1面密度よりも小さい第2面密度で注入された第2リサーフ領域12と、第2リサーフ領域12の外側に配設され、P型不純物が第2面密度よりも小さい第3面密度で注入された第3リサーフ領域13とを含む。このうち第1リサーフ領域11および第3リサーフ領域13は、半導体層の上面に形成されたリセス11r,13rの下に形成される。

(もっと読む)

電子装置

【課題】 信頼性及び色再現性の高い電子装置を提供する。

【解決手段】 単結晶半導体基板11上にスイッチング用FET201及び電流制御用FET202を形成し、電流制御用FET202にEL素子203が電気的に接続された画素構造とする。電流制御用FET202は画素間での特性ばらつきが極めて小さく、色再現性の高い画像を得ることができる。電流制御用FET202にホットキャリア対策を施すことで信頼性の高い電子装置が得られる。

(もっと読む)

半導体装置

【課題】nチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタを有する半導体装置において、nチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタ共にドレイン電流特性に優れた半導体装置を実現する。

【解決手段】nチャネル型電界効果トランジスタ10と、pチャネル型電界効果トランジスタ30とを有する半導体装置において、nチャネル型電界効果トランジスタ10のゲート電極15を覆う応力制御膜19には、膜応力が引張応力側の膜を用いる。pチャネル型電界効果トランジスタ30のゲート電極35を覆う応力制御膜39には、膜応力が、nチャネル型トランジスタ10の応力制御膜19より、圧縮応力側の膜を用いることにより、nチャネル型、pチャネル型トランジスタの両方のドレイン電流の向上が期待できる。このため、全体としての特性を向上させることができる。

(もっと読む)

パワーデバイス

【課題】ポリイミド膜上に設けた電極パッドに導体バンプなしにAlワイヤを確実に接合でき、ポリイミド膜からの電極パッドの剥離や電極パッドとAlワイヤとの接合不良を防止できるパワーデバイスを提供する。

【解決手段】絶縁基板1上に設けられた半導体素子(2,3,6)と、絶縁基板1上に形成され、半導体素子(2,3,6)を覆う軟質ポリイミド膜11と、軟質ポリイミド膜11上に形成された電極パッド9と、電極パッド9にワイヤボンディングにより一端が接合されたAlワイヤ12とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】耐圧を向上した半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、第1半導体領域、第2半導体領域、第3半導体領域、第4半導体領域、ゲート領域、ゲート絶縁膜及び電界緩和領域を備える。第1導電形の第1半導体領域は、第1部分と第1方向に延出した第2部分とを有する。第1導電形の第2半導体領域は、第1部分上の第3部分と第2部分と隣接する第4部分とを有する。第2導電形の第3半導体領域は、第3部分上の第5部分と第4部分と隣接する第6部分とを有する。第1導電形の第4半導体領域は、第5部分上で第6部分と隣接する。ゲート領域は、第2半導体領域、第3半導体領域及び第4半導体領域を第2方向に貫通するトレンチ内に設けられる。ゲート絶縁膜は、トレンチ内壁とゲート領域との間に設けられる。第2導電形の電界緩和領域は、第3部分と第5部分との間に設けられ、第3半導体領域よりも不純物濃度が低い。

(もっと読む)

ポータブル電気素子およびデータ処理センタのための低電圧MOSFETを形成する半導体素子および方法

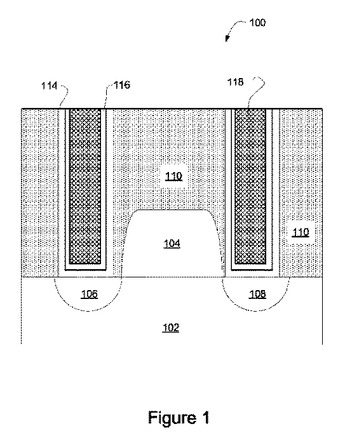

【課題】半導体素子を提供すること。

【解決手段】半導体素子であって、基板と、該基板内に形成された井戸領域と、該基板の表面の上方に形成されたゲート構造と、該ゲート構造に隣接して基板内に形成されたソース領域と、該ソース領域の反対側に該ゲート構造に隣接して該基板内に形成されたドレイン領域と、該ソース領域を通して形成されたトレンチと、該トレンチを通して形成されたプラグと、該トレンチを通して該プラグの上方に形成されたソースタイと、該ソース領域、該ドレイン領域、および該ゲート構造の上方に形成された相互接続構造とを備える、半導体素子。

(もっと読む)

自己整合コンタクト

トランジスタは、基板と、基板上の一対のスペーサと、基板上且つスペーサ対間のゲート誘電体層と、ゲート誘電体層上且つスペーサ対間のゲート電極層と、ゲート電極層上且つスペーサ対間の絶縁キャップ層と、スペーサ対に隣接する一対の拡散領域とを有する。絶縁キャップ層は、ゲートにセルフアラインされるエッチング停止構造を形成し、コンタクトエッチングがゲート電極を露出させることを防止し、それにより、ゲートとコンタクトとの間の短絡を防止する。絶縁キャップ層は、セルフアラインコンタクトを実現し、パターニング限界に対して一層ロバストな、より幅広なコンタクトを最初にパターニングすることを可能にする。  (もっと読む)

(もっと読む)

エピタキシャルソース/ドレインが自己整合したマルチゲート半導体デバイス

低寄生抵抗であるチャネル歪みされたマルチゲートトランジスタとその製造方法に係る。ゲートを連結したチャネル側壁の高さがHsiである半導体フィンのチャネル領域の上にゲートスタックを形成されてよく、ゲートスタックに隣接する半導体フィンのソース/ドレイン領域内に、エッチングレートを制御するドーパントを注入してよい。ドーピングされたフィン領域をエッチングして、半導体フィンの、略Hsiに等しい厚みを除去して、ゲートスタックの一部の下にある半導体基板の部分を露呈させるソース/ドレイン延長キャビティを形成してよい。露呈した半導体基板の上に材料を成長させて、再成長したソース/ドレイン・フィン領域を形成して、ソース/ドレイン延長キャビティを充填して、ゲートスタックからの長さを、チャネルの長さに実質的に平行な方向に離れる方向に延ばしてよい。 (もっと読む)

高kゲート誘電体のための、不純物酸素を捕捉する半導体構造および該構造を形成する方法(高kゲート誘電体のための捕捉金属スタック)

【課題】CMOS集積過程での高温処理の後であっても一定の閾値電圧を維持する高kゲート誘電体の提供。

【解決手段】高kゲート誘電体30と、下部金属層40、捕捉金属層50、および上部金属層60を含む金属ゲート構造とのスタックを提供する。該捕捉金属層は、次の2つの基準、1)Si+2/yMxOy→2x/yM+SiO2の反応によるギブス自由エネルギの変化が正である金属(M)であること、2)酸化物形成に対する酸素原子あたりのギブス自由エネルギが、下部金属層の金属および上部金属層の金属より大きな負である金属であること、を満たす。これらの基準を満たす捕捉金属層は、酸素原子がゲート電極を通って高kゲート誘電体に向け拡散するときに該酸素原子を捕捉する。さらに、該捕捉金属層は、高kゲート誘電体の下の酸化ケイ素界面層の厚さを遠隔から低減する。この結果、ゲート誘電体全体の等価酸化膜厚(EOT)の変動が抑制される。

(もっと読む)

金属−絶縁体−半導体トンネリングコンタクト

本発明はソース領域又はドレイン領域へのコンタクトに関する。コンタクトは導電性材料を有するが、その導電性材料は絶縁体によりソース領域又はドレイン領域から分離されている。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置の動作不良を防止し、半導体装置の製造工程を簡略化する。

【解決手段】本発明の例に関わる半導体装置は、半導体基板1と、半導体基板1内に設けられる一対の不純物拡散層2A,2Bと、不純物拡散層2A,2B間の半導体基板上に設けられるゲート絶縁膜3と、ゲート絶縁膜3上に設けられるゲート電極4と、一対の不純物拡散層2A,2B上にそれぞれ設けられる2つのコンタクト5A,5Bとを具備し、ゲート電極4とコンタクト5A,5Bは、同じ材料から構成され、ゲート電極4上端およびコンタクト5A,5B上端は、半導体基板1表面からの高さが一致する。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】急峻な不純物分布のhalo層を備える半導体素子及び半導体素子の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体素子1は、半導体基板10と、半導体基板10に設けられる凸領域12と、凸領域12上に設けられるゲート絶縁膜100と、ゲート絶縁膜100の下の凸領域12内に位置するチャネル領域101と、凸領域12の両側に設けられ、チャネル領域101の両側にエクステンション115aを有するソースドレイン領域115と、凸領域12とソースドレイン領域115との間に設けられ、凸領域12と接触する部分に境界を有して設けられるhalo層110とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】耐湿性(信頼性)及び高周波特性を両立することができる半導体装置及びその製造方法を提供する。

【解決手段】半絶縁性のSiC基板1上に化合物半導体領域2が形成されている。化合物半導体領域2上に、ゲート電極6、ソース電極4及びドレイン電極5が形成されている。シリコン窒化膜10上に、ソース電極4及びドレイン電極5から離れた位置においてゲート電極6を覆う低誘電率膜11が形成されている。低誘電率膜11の上面及び側面を覆うシリコン窒化膜12がシリコン窒化膜10上に形成されている。シリコン窒化膜12上に低誘電率膜13が形成されている。低誘電率膜13の比誘電率は低誘電率膜11のそれよりも高い。また、低誘電率膜13の耐湿性は低誘電率膜11のそれより高い。

(もっと読む)

半導体装置

【課題】半導体装置における配線等を溶液と接触しないように設けたパッシべーション膜及び絶縁膜に穴やクラック等が存在し、MOSトランジスタの配線などと、電位が印加された溶液が接触したとしても、このリークの生じている他のMOSトランジスタに対してリーク電流が流れ込まない素子分離構造を有する半導体装置を提供する。

【解決手段】 本発明の半導体装置は、第1の導電型の不純物が添加された半導体基板と、該半導体基板上に形成されており、第1の導電型と異なる導電型である第2の導電型のウェル層と、該半導体基板上に、ウェル層の周りに形成された第1の導電型の分離ウェル層と、分離ウェル層と、トランジスタ形成領域を除いたウェル層との表面に形成された素子分離膜とを有し、半導体基板と分離ウェルとにより、ウェル層の半導体基板内の外周面が覆われている。

(もっと読む)

導電性コンタクトの組み込みのための構造体及びプロセス

【課題】 キーホール・シームの形成を排除した信頼性が高い高アスペクト比のコンタクト構造体を含む半導体構造を提供する。

【解決手段】 キーホール・シームの形成は、本発明においては、誘電体材料内部に存在する高アスペクト比のコンタクト開口部内に高密度化貴金属含有ライナを設けることによって排除される。高密度化貴金属含有ライナは拡散バリアの上に配置され、これら両方の要素は、本発明のコンタクト構造体の導電性材料を、下層の半導体構造体の導電性材料から分離する。本発明の高密度化貴金属含有ライナは、第1の抵抗率を有する貴金属含有材料の堆積、及び、堆積した貴金属含有材料の抵抗率をより低い抵抗率に減少させる高密度化処理プロセス(熱又はプラズマ)を、堆積した貴金属含有材料に施すことによって形成される。

(もっと読む)

半導体装置およびその製造方法

【目的】ジャンクションブロックを不要とし、またワイヤーハーネスの占有スペースを縮小化し、過電流となった主電流を確実に遮断できて、電気経路を確実に開放できるヒューズ素子を半導体基板内に形成した半導体装置およびその製造方法を提供する。

【解決手段】p半導体基板1に形成したトレンチ18の内壁にシリコン酸化膜21を介してヒューズ素子22を形成し、トレンチ18の開口部を塞ぐようにポリイミド膜23を被覆することで、溶断したヒューズ素子22が再度固化したときに、固化したヒューズ材で第1表面端子aと第2表面端子bの間を短絡しないようにする。半導体装置内にヒューズ素子22を有することで、ジャンクションブロックを不要とし、またワイヤーハーネスの占有スペースを縮小化できる。

(もっと読む)

1 - 20 / 55

[ Back to top ]