Fターム[5F140CD00]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | その他の領域、その他の素子構造及び製造 (630)

Fターム[5F140CD00]の下位に属するFターム

埋込み領域 (255)

ライフタイムを制御しているもの (9)

内部ストレスの存在する領域 (31)

フィールドプレート(内部電界の緩和以外) (252)

製造方法 (48)

Fターム[5F140CD00]に分類される特許

21 - 35 / 35

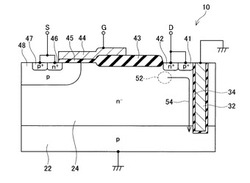

半導体装置

【課題】 サージ電圧等が印加されたときに、ドレイン領域の近傍で発生する正孔を早い段階で排出するための技術を提供すること。

【解決手段】 半導体装置10は、半導体活性層24の表面部分の一部であり、ドレイン領域42の近傍に形成されているp+型の半導体領域41を備えている。p+型半導体領域41は、半導体活性層24によってボディ領域48及び半導体基板22から隔てられており、ドレイン電極Dに電気的に接続している。半導体装置10はさらに、半導体活性層24のうちのp+型半導体領域41と半導体基板22の間に存在する部分に絶縁膜を34介して対向している導電体領域34を備えている。導電体領域34には、接地電圧が印加されていることを特徴としている。

(もっと読む)

窒化物半導体素子

【課題】 高アバランシェ耐量と低オン抵抗性とを有する窒化物半導体素子を提供する。

【解決手段】 窒化物半導体からなる第1の半導体層と、前記第1の半導体層の上に設けられ前記第1の半導体層よりもバンドギャップが大なるノンドープまたはn型の窒化物半導体からなる第2の半導体層と、を有する積層体と、前記積層体の主面上の第1の領域に直接もしくは絶縁膜を介して設けられた制御電極と、前記積層体の主面上の前記第1の領域の両端に隣接する第2及び第3の領域にそれぞれ設けられた第1及び第2の主電極と、前記積層体の主面上において前記第2の主電極を挟んで前記制御電極とは反対側に設けられた第3の主電極と、を備えたことを特徴とする窒化物半導体素子を提供する。

(もっと読む)

歪み超格子とその上の応力層とを含む半導体デバイス、及びその製造方法

半導体デバイスは、積層された複数の層群を有する歪み超格子層(325)、及び歪み超格子層の上方の応力層を含んでいる。歪み超格子層の各層群は、ベース半導体部分を画成する積層された複数のベース半導体モノレイヤーと、隣接し合うベース半導体部分の結晶格子内に拘束された少なくとも1つの非半導体モノレイヤーとを含んでいる。  (もっと読む)

(もっと読む)

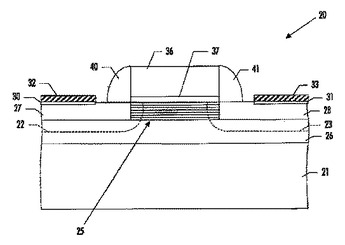

非半導体モノレイヤーを有するチャネルを含む半導体デバイス、及びその製造方法

半導体デバイスは、半導体基板及びその上の少なくとも1つのMOSFETを含んでいる。このMOSFETは、空間的に隔てられたソース領域及びドレイン領域、ソース領域とドレイン領域との間のチャネル、及びチャネルの上に位置しチャネルとの界面を画成するゲートを含んでいる。ゲートは、チャネルの上に位置するゲート誘電体と、ゲート誘電体の上に位置するゲート電極とを含んでいる。また、このチャネルは、積層された複数のベース半導体モノレイヤーと、隣接し合うベース半導体モノレイヤーの結晶格子内に拘束された少なくとも1つの非半導体モノレイヤーとを含んでいる。上記少なくとも1つの非半導体モノレイヤーは、チャネルとゲート誘電体との間の界面に対しておよそ4−100モノレイヤーの深さに位置付けられている。  (もっと読む)

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】配線形成のためのドライエッチングが進行しても、ゲート絶縁膜にチャージダメージを与えることを抑制できる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、ゲート絶縁膜3a,3bを形成する工程と、ゲート配線4a,4bを形成する工程と、絶縁膜8を形成する工程と、接続孔8a,8b,8cを形成する工程と、接続孔8a,8b,8cに導電体9a,9b,9cを埋め込む工程と、絶縁膜8上及び導電体9a,9b,9c上に、導電膜11,12,13を形成する工程と、ドライエッチングを用いて導電膜11,12,13をパターニングすることにより、絶縁膜8上に複数の配線10a,10b,10d、及びダミー配線10cを形成する工程とを具備する。ダミー配線10cと、ダミー配線10cに最も近い配線10bの間隔は、配線10a,10b,10dの相互間隔以下である。

(もっと読む)

半導体装置及びその製造方法

【課題】 占有面積を抑えた簡便な形態でプラズマ処理に伴うチャージングを抑える半導体装置及びその製造方法を提供する。

【解決手段】 層間の絶縁層17はMOSFET Q1を覆い、所定部が貫通されホール18t,18dが形成されている。ホール18tは、配線用ホールで、配線プラグ部材19tが埋め込まれ、下端部はゲート電極14に接続されている。配線パターン21は、配線プラグ部材19tの上端部と接続されている。ホール18dは、ダミー用ホールで、埋め込まれたダミープラグ部材19dは、その下端部が半導体基板10の基板コンタクト領域12に接続されている。配線パターン21形成のために配線層M1(破線)をドライエッチングしている最中において、ダミープラグ部材19dは、プラズマチャージを放電させる経路となる。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】外部イオンや水分のゲート絶縁膜への浸透を防止する半導体集積回路装置を提供する。

【解決手段】半導体集積回路装置は、半導体基板、半導体基板上に一方向に延びて形成されたゲート配線220とゲート配線に整列して半導体基板内に形成されたソース/ドレーン領域を含むトランジスタ、ゲート配線上にゲート配線と同一方向に延びて形成され、半導体基板に拡散されるイオンを遮断する拡散防止メタルパターン432aを含む。

(もっと読む)

半導体装置及び該半導体装置を動作させる方法

本発明は、ドレイン延長部(8)を備えるラテラルDMOSTに特に関する。既知のトランジスタにおいて、更なる金属ストリップ(20)は、ゲート電極コンタクトストリップと、ソース領域コンタクト(15)に電気的に接続されているドレインコンタクト(16)との間に位置される。本特許出願において提案される装置において、更なる金属ストリップ(20)とソースコンタクト(15,12)との間の接続部は、コンデンサ(30)を有し、更なる金属ストリップ(20)は更なる金属ストリップ(20)に電圧を供給するための更なるコンタクト領域(35)を備えている。このようにして、改善された線形性が実現可能であり、当該装置の実用性が、特に、高電力及び高周波数において改善される。好ましくは、コンデンサ(30)は、単一の半導体基体(1)内にトランジスタと一体化されている。本発明は、更に、本発明による装置(10)を動作させる方法を有する。  (もっと読む)

(もっと読む)

半導体装置

【課題】第1の負性抵抗領域が無い、高サージ耐量の半導体装置を提供すること。

【解決手段】p半導体基板1の表面にnウェル領域2を形成し、nウェル領域2の表面層にpウェル領域3を形成し、pウェル領域3の表面層からnウェル領域2の表面層に渡ってnオフセット領域9を形成し、このnオフセット領域9の表面層にnドレイン領域8を形成する。pウェル領域3のnドレイン領域8側は横方向拡散によりnドレイン領域8側に向かって不純物濃度が低くなるため、nドレイン領域8側に向かって不純物濃度か高くなる第2のnオフセット領域15が形成され、その結果、nオフセット領域9は不純物濃度が一定で低い第1のnオフセット領域9aと、nドレイン領域8側に向かって不純物濃度が高くなる第2のnオフセット領域15で構成される。この第2のオフセット領域の長さMをnドレイン領域8の縦方向の拡散深さNより大きくする。

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体基板に垂直なフィン状のチャネル部を有する電界効果トランジスタの信頼性を高めるのに最適な構造を有する半導体装置およびその製造方法を提供する。

【解決手段】 絶縁層12上に形成された突起状の半導体層と、半導体層の少なくとも側面上にゲート絶縁膜20を介して形成されたゲート電極21と、ゲート電極21を挟むように半導体層内に形成されたソース及びドレイン領域16、17と、絶縁層12上に形成され半導体層の周りに配設された防御壁19と、半導体層および防御壁19上に形成された絶縁膜22と、を具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】高周波電力増幅用電界効果型半導体装置において、耐圧を確保しながらの小型化と高効率化の両立が困難になる。

【解決手段】高周波電力増幅用出力段LDMOSに、歪Siチャネルを用いることで更なる効率向上を実現する。更に、チャネル領域を有する歪Si層の膜厚、欠陥の不活性化、或いはフィールドプレート構造の最適化などによってリーク電流を低減しつつ最大限に効率を高める。

(もっと読む)

ゲート及びチャネル内に歪を誘起させてCMOSトランジスタの性能を向上させる方法

【課題】 ゲート内の応力を調節することによってトランジスタ・チャネル内に歪を誘起させること。

【解決手段】 相補型金属酸化物半導体トランジスタを製造する方法は、異なる型のトランジスタ、例えばN型金属酸化物半導体(NMOS)トランジスタ及びP型金属酸化物半導体(PMOS)トランジスタ(第1及び第2型トランジスタ)を基板(12)上に形成する。この方法は、これらのNMOSトランジスタ及びPMOSトランジスタ上に任意の酸化物層を形成し、次いでNMOSトランジスタ及びPMOSトランジスタを硬い材料(50)、例えば窒化ケイ素層で覆う。この後、この方法は、この硬い材料層(50)の一部をパターン形成し、硬い材料層がNMOSトランジスタ上にのみ残るようにする。次に、この方法は、NMOSトランジスタを加熱し(178、204)、次いで硬い材料層(50)の残存部分を除去する。PMOSトランジスタ(PFET)のゲート(20)又はチャネル領域内に応力を生じさせることなく、NMOSトランジスタ(NFET)のゲート(22)内に圧縮応力、チャネル領域内に引張応力(70)を生じさせることによって、この方法は、PFETの性能を低下させることなく、NFETの性能を改善する。

(もっと読む)

半導体装置

【課題】 簡易な工程でかつ安価に製造でき、しかも高温高湿下でのドレイン耐圧の低下を防止でき、微細化も図れる半導体装置を提供する。

【解決手段】 ソース電極70およびドレイン電極80の上部における保護膜90に、第1の開口部としてイオンスルー領域102を設ける。保護膜90上に封止樹脂を塗布して半導体装置をパッケージする。このとき、イオンスルー領域102内にも封止樹脂を充填して、封止樹脂とソース電極70およびドレイン電極80とを直に接触させる。これにより、高温高湿雰囲気下において、封止樹脂内における保護膜90との界面に蓄積した可動イオンは、イオンスルー領域102を通ってソース電極70およびドレイン電極80へと排出され、N- 型延長ドレイン領域30に影響を与えなくなるため、ドレイン耐圧を向上できる。

(もっと読む)

半導体集積回路装置の製造方法

【課題】 MOSトランジスターのきめ細かなマルチVth化により、複雑な信号処理が可能であるアナログ半導体集積回路装置の製造方法を提供する。

【問題解決手段】 MOSトランジスターのソ−スとゲート電極にオーバラップするように選択的に窒化膜を配する製造方法により、かつそのチャネル幅方向の窒化膜のゲート電極へのオーバラップ量をパターン設計値で可変することによりきめ細かなマルチVth化を実現する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】ダミーパターンの面積を大きくしなくても、半導体素子や配線へのプラズマチャージ量を少なくする。

【解決手段】 半導体基板1にトランジスタ11を形成すると共に、半導体基板1上にMNOS素子10を形成する。MNOS素子10に電荷を蓄積した後、層間絶縁膜20を形成する。層間絶縁膜20に、ゲート電極5b上に位置する第1の接続孔20b、及びMNOS素子10上に位置する第2の接続孔20aを形成する。層間絶縁膜20上に、第1の接続孔20bを介してゲート電極5bに接続する配線22bを形成すると共に、第2の接続孔20aを介してMNOS素子10に接続するダミーパターン22aを形成する。

(もっと読む)

21 - 35 / 35

[ Back to top ]