Fターム[5F140CE05]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 製造工程一般 (2,583) | 平坦化 (1,497)

Fターム[5F140CE05]の下位に属するFターム

エッチバック (137)

CMP (1,242)

SD領域/SD電極とG電極上面の平坦化 (34)

Fターム[5F140CE05]に分類される特許

21 - 40 / 84

歪み半導体デバイス用のゲルマニウム含有量が漸次変化した高ゲルマニウム化合物膜

ゲルマニウム含有量が漸次変化した高ゲルマニウム化合物領域を供する装置及び方法に係る実施例が全体として記載されている。他の実施例も記載及びクレームされている。  (もっと読む)

(もっと読む)

半導体装置

【課題】 従来の構造よりさらに安定した電気的特性を実現しうる横型MOSトランジスタを提供する。

【解決手段】 P型の半導体基板10内において方向d1に延伸するP型のボディ領域15、ボディ領域15と離間して形成されたN型のドレイン領域11、ボディ領域15内に形成された高濃度P型のボディコンタクト領域21及びN型のソース領域16、ドレイン領域11内に形成された高濃度N型のドレインコンタクト領域12、並びにソース領域16とドレインコンタクト領域12の間に形成されたP型の拡散領域13を備え、拡散領域13は、ドレイン領域11内においてボディ領域15と離間した状態で方向d1に延伸して形成される主領域13aと、主領域13a内のボディ領域15と対向する外周端の一または離散した複数の一部領域からボディ領域15に向かう方向にボディ領域15または半導体基板10と連絡する位置まで突出する突出領域13bとを有する。

(もっと読む)

トランジスタにおいて進歩したシリサイド形成と組み合わされる凹型のドレイン及びソース区域

【解決手段】

洗練されたトランジスタ要素を形成するための製造プロセスの間、それぞれの金属シリサイド領域を形成するのに先立つ共通のエッチングシーケンスにおいて、ゲート高さが減少させられてよく、そして凹型のドレイン及びソース構造もまた得られてよい。対応する側壁スペーサ構造はエッチングシーケンスの間に維持され得るので、ゲート電極におけるシリサイド化プロセスの可制御性及び均一性を高めることができ、それにより、低減された程度のスレッショルドばらつきを得ることができる。更に、凹型のドレイン及びソース構造が、全体的な直列抵抗の低減及び応力転移効率の増大をもたらすことができる。

(もっと読む)

半導体装置

【課題】 LDD形成工程に於けるプラズマプロセスが原因となり生じる素子の

損傷を極力低減した半導体装置の作製方法を提供すること。

【解決手段】 基板全面を覆うように導電性膜を形成した状態で、ハードマスク

を利用した半導体装置の作製方法でLDD構造の素子を形成することにより、L

DD形成工程におけるプラズマプロセスによる素子への損傷を極力低減する。導

電性膜が全面に形成されていることにより、異方性エッチング等のプラズマによ

る処理(プラズマプロセス)においてゲート電極に蓄積される電荷密度を低減で

き、プラズマプロセスによる損傷を低減できる。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化しても動作特性の劣化が生じないSTI構造の半導体装置及びその製造方法を得る。

【解決手段】NMOSトランジスタのゲート電極部をNMOS仕事関数制御メタル層7及びゲート主電極5により構成する。NMOS仕事関数制御メタル層7をスパッタ法により形成され、ディボット部2dが設けられるエッジ近傍領域である領域bにおける膜厚は、他の領域である領域aにおける膜厚より薄く形成される。したがって、NMOS仕事関数制御メタル層7に関し、領域bにおける実効仕事関数が領域aにおける実効仕事関数に比べ、ミッドギャップよりに設定される。

(もっと読む)

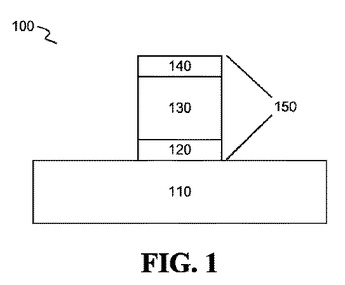

誘電体エッチストップ層の選択的形成

【解決手段】 パターニングされた金属フィーチャの上方に誘電体エッチストップ層を選択的に形成する方法を開示する。実施形態には、当該方法に従って形成されたエッチストップ層をゲート電極の上方に設けているトランジスタが含まれる。本発明の特定の実施形態によると、ゲート電極の表面上に金属を選択的に形成して、当該金属をケイ化物またはゲルマニウム化物に変換する。他の実施形態によると、ゲート電極の表面上に選択的に形成された金属によって、ゲート電極の上方にシリコンまたはゲルマニウムのメサを触媒成長させる。ケイ化物、ゲルマニウム化物、シリコンメサ、またはゲルマニウムメサの少なくとも一部を酸化、窒化、または炭化して、ゲート電極の上方にのみ誘電体エッチストップ層を形成する。 (もっと読む)

半導体装置及びその製造方法

【課題】 厚いCESL膜を用いてもCESL膜やその上の層間絶縁膜に生じるボイドを回避し、高い駆動電流と高い信頼性を実現する。

【解決手段】 半導体基板10上にゲート絶縁膜12を介してゲート電極13を形成し、ゲート電極13を挟んで基板の表面部にソース/ドレイン領域18を形成してなるMOSFETを有する半導体装置であって、ゲート部のゲート長方向の側部に形成された側壁絶縁膜17と、ソース/ドレイン領域18上に形成された合金層19と、側壁絶縁膜17の側部に設けられ、ゲート長方向の断面で見た基板表面と成すテーパ角度が側壁絶縁膜17よりも小さいテーパ調整用絶縁膜21と、ゲート部、側壁絶縁膜17及びテーパ調整用絶縁膜21を覆うように形成された、チャネルに歪みを与えるための応力付与用絶縁膜22と、応力付与用絶縁膜22上に形成された層間絶縁膜25とを備えた。

(もっと読む)

半導体装置及びその製造方法

【課題】電力用半導体装置において十分な基板強度を確保しつつ低オン抵抗且つ高耐圧でスイッチング速度を向上できるようにする。

【解決手段】P型の半導体基板1に形成されたN型のリサーフ領域2と、半導体基板1の上部にリサーフ領域2と隣接したP型のベース領域3と、ベース領域3にリサーフ領域2と離隔したN型のエミッタ/ソース領域8と、ベース領域3にエミッタ/ソース領域8と隣接したP型のベース接続領域10と、エミッタ/ソース領域8の上からベース領域3の上及びリサーフ領域2の上に形成されたゲート絶縁膜6並びにゲート電極7と、リサーフ領域2にベース領域3と離隔したP型のコレクタ領域4とを有している。半導体基板1は、その抵抗値が半導体基板1に添加された不純物濃度で決まる抵抗値の2倍以上となるように結晶欠陥が導入されている。

(もっと読む)

半導体装置

【課題】MIS型半導体装置やMS型半導体装置において、簡便な手法により半導体層の界面準位を所望のエネルギー準位に設定することが可能な半導体装置を提供する。

【解決手段】導電体と、ソース領域とドレイン領域とを有する半導体と、前記ソース領域と前記ドレイン領域との間において、前記導電体と前記半導体とにそれぞれ接して前記導電体と前記半導体との間に設けられた単分子層と、を備え、前記半導体と前記単分子層との界面において、前記単分子層を構成する分子の電子準位が前記半導体のバンドギャップ内に状態密度の極大を形成してなることを特徴とする半導体装置を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】低い閾値電圧のnチャネル型MISトランジスタを含む半導体装置を実現する。

【解決手段】半導体装置は、半導体基板と、半導体基板の主面に形成されたn型半導体領域とp型半導体領域と、半導体基板上に形成され、n型半導体領域とp型半導体領域を露出するように形成された第1と第2のトレンチを有する第1の絶縁層と、第1と第2のトレンチの側壁と底部に沿って形成されたゲート絶縁膜と、第1のトレンチの側壁と底部に沿って形成されゲート絶縁膜を介して内張りされた第1の金属層と、第2のトレンチの側壁と底部に沿って形成されゲート絶縁膜を介して1モノレイヤー以上で1.5nm以下の厚さに内張りされた第2の金属層と、第2の金属層上に内張りされたアルカリ土類金属元素、III族金属元素の単体、窒化物、炭化物、酸化物の内の少なくとも1つの金属元素を含む第3の金属層と、第1と第2のソース/ドレイン領域を具備することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】 低コストで製造が可能な低オン抵抗且つ高耐圧な半導体装置及びその製造方法を提供する。

【解決手段】 P型の半導体基板1上に形成された、N型のウェル領域2と、ウェル領域2内に形成されたP型のボディ領域3と、ボディ領域3内に形成されたN型のソース領域6と、ウェル領域2内において、ボディ領域3とは離間して形成されたN型のドレイン領域8と、ボディ領域3の一部上層を含む領域に形成されたゲート絶縁膜12と、ゲート絶縁膜12上層に形成されたゲート電極9と、ウェル領域2内において、ボディ領域3の底面に接触すると共に、半導体基板1面と平行方向にドレイン領域8の下方領域に延在するP型の埋め込み拡散領域4と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極間の分離領域を含むゲート電極の端部形状の加工が容易となる構造を有する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10の表面よりも高い上面を有する素子分離絶縁膜11により半導体基板に第1及び第2チャネル形成領域を有する第1及び第2半導体領域(12,13)がそれぞれ区分され、第1及び第2チャネル形成領域上にゲート絶縁膜14と第1及び第2ゲート電極(G1,G2)が形成され、その両側部における第1及び第2半導体領域の表層部にソースドレイン領域が形成され、第1及び第2ゲート電極は、第1及び第2半導体領域内において素子分離絶縁膜と略同じ高さを有し、その端部が素子分離絶縁膜の側面に接するように形成された第1導電層15pと、上記端部から素子分離絶縁膜上にはみ出すように第1導電層上に形成された第2導電層16sとを有する構成とする。

(もっと読む)

半導体素子およびその製造方法

【課題】所定の耐圧で、所定のON抵抗を得ることができる実用可能なリサーフ型LDMOSを提供する。

【解決手段】第1導電型不純物の半導体層と、半導体層に形成の局所絶縁層7と、局所絶縁層を挟んで、第2導電型不純物のドレイン層8、ソース層11と、局所絶縁層上からソース層に至る半導体層上のゲート電極13と、を備えた半導体素子において、ドレイン層下、局所絶縁層下、およびゲート電極下の半導体層に、第2導電型不純物をドレイン層より低濃度の低濃度拡散層と、ゲート電極と半導体層の間に、ゲート電極のソース層側端部から局所絶縁層に向かって、局所絶縁層に達することなく延在した第1のゲート絶縁膜と、ゲート電極と半導体層の間に、局所絶縁層の他の側の端部からソース層に向かって延在して第1のゲート絶縁膜に接続された、膜厚が第1のゲート絶縁膜の膜厚より厚く、局所絶縁層の膜厚の半分よりも薄い第2のゲート絶縁膜と、を有する。

(もっと読む)

半導体装置の構造および製造方法

【課題】STI領域の絶縁膜掘り下げにより形成される幅30nm以下の拡散層が配されているFinFETにおいて、寄生抵抗を低減した構造及びその製造方法を提供する。

【解決手段】STI領域105に挟まれ、素子分離領域上方に突き出た幅30nm以下の半導体層にソース及びドレイン領域となる拡散層104が形成されており、ソース及びドレイン領域間のチャネル領域を跨ぐゲート電極を有する凸型Fin構造の電界効果トランジスタであって、前記ソース及びドレイン領域となる拡散層側壁にサイドウォール110b、該サイドウォールに挟まれた拡散層上面に選択エピタキシャル成長シリコン層111、及び該選択エピタキシャル成長シリコン層に接続されるコンタクトプラグ115を有することを特徴とする半導体装置。

(もっと読む)

半導体装置の製造方法

【課題】 イオン注入時における素子形成領域と素子分離領域とのレジスト寸法差を所望の値以下とすることができ、デバイス特性の改善に寄与する。

【解決手段】 半導体基板101の素子形成領域102を囲むように素子分離溝を形成する工程と、この溝内に絶縁膜104を埋め込んだ後に平坦化することで素子分離領域103を形成する工程と、素子形成領域102にゲート絶縁膜111、ゲート電極112、ソース/ドレイン領域114,115を形成することでトランジスタを作製する工程と、素子形成領域102と素子分離領域103に跨るように、イオン注入のマスクとなるレジスト121のパターンを形成する工程とを含む半導体装置の製造方法であって、絶縁膜104の厚さを、所望耐圧を満たす膜厚以上に設定し、且つ絶縁膜104上のレジスト寸法と素子形成領域102上のレジスト寸法との差が極小値となる膜厚近傍に設定する。

(もっと読む)

半導体装置及びその製造方法

【課題】STI領域で囲まれた部分のシリコン基板をエッチングすることによりシリコン柱を形成して、シリコン柱をゲート絶縁膜およびゲート電極で覆いチャネル部とし、チャネル部の上下にソース・ドレインとなる拡散層を有した縦型MOSトランジスタにおいて、STI絶縁膜側壁に残ったゲート電極材による寄生MOS動作を解消する。

【解決手段】STI絶縁膜2の側壁に形成されるゲート電極材8に、該ゲート電極材の電位を制御する電極14を形成する。

(もっと読む)

半導体デバイスの製造方法。

【課題】高誘電体膜とシリコン基板とを分離する、極薄かつ緻密な界面層を形成する半導体デバイスの製造方法を提供する。

【解決手段】本発明の半導体デバイスの製造方法は、シリコン基板表面にシリコン酸化膜を形成する工程(酸化膜形成ステップ)と、シリコン酸化膜を所望膜厚だけ残してエッチングする工程(エッチングステップ)と、エッチング後のシリコン酸化膜上に高誘電体膜を形成する工程(高誘電体膜形成ステップ)とを有する。

(もっと読む)

半導体装置とその製造方法

【課題】絶縁膜を研磨せずに、該絶縁膜からゲート電極の上面を露出させることが可能な半導体装置とその製造方法を提供すること。

【解決手段】シリコン基板1の上にゲート絶縁膜5を形成する工程と、ゲート絶縁膜5の上にゲート電極7aを形成する工程と、ゲート電極7aを覆うように液状の絶縁性材料20を塗布する工程と、絶縁性材料20に鋳型100を押し当てることにより、ゲート電極7aの上方の絶縁性材料20を押し流す工程と、絶縁性材料20を硬化して絶縁膜21にする工程と、硬化の後、ゲート電極7a上に高融点金属膜を形成する工程と、高融点金属膜をアニールすることにより、ゲート電極7aの全体をシリサイド化する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置及びその製造方法

【課題】 ゲート電極の側壁絶縁膜のエッチングを効果的に防止することが可能な半導体装置を提供する。

【解決手段】 半導体基板11と、半導体基板上に形成されたゲート絶縁膜13と、ゲート絶縁膜上に形成されたゲート電極22と、ゲート電極の側面に形成された第1の絶縁膜17と、第1の絶縁膜の表面を覆い、第1の絶縁膜とは異なった材料で形成された第2の絶縁膜28と、半導体基板、ゲート電極及び第2の絶縁膜を覆い、第2の絶縁膜とは異なった材料で形成された第3の絶縁膜23とを備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】レイアウトに依存することなく深さが制御されかつ結晶欠陥の発生が抑えられたエピタキシャル成長層が設けられ、これにより特性の向上が図られた半導体装置を提供する。

【解決手段】半導体基板3上に設けられたゲート電極9と、ゲート電極9両脇に不純物を導入して設けられたソース/ドレイン領域15とを備えた半導体装置1aにおいて、ソース/ドレイン領域15は、ゲート電極9脇における半導体基板3を掘り下げた位置に当該半導体基板3とは格子定数が異なる半導体材料をエピタキシャル成長させてなるエピタキシャル成長層11と、半導体基板3の表面層に設けた基板拡散層13とで構成されている。

(もっと読む)

21 - 40 / 84

[ Back to top ]