Fターム[5F140DB06]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | シミュレーション (228) | 実測値による補正を行うもの (41)

Fターム[5F140DB06]に分類される特許

1 - 20 / 41

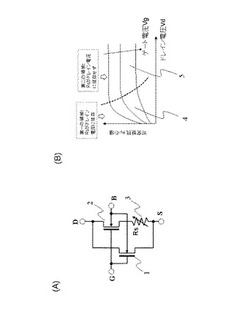

高耐圧MOSFETの回路シミュレーション用モデルの作成方法と装置並びにプログラム

【課題】高耐圧MOSFETのモデルにおいて、ドレイン電流の精度を広いバイアス範囲で得ることができ、シミュレーションの精度を向上させる。

【解決手段】ドレインが共通接続され、ゲートが共通接続され、バックゲートが共通接続され、ソース領域のソース拡散層の幅とウェルコンタクト拡散層の幅にそれぞれ対応した第1及び第2のチャネル幅を有する第1及び第2のMOSFET1、2と、第2のMOSFET2のソースに一端が接続された第1の可変抵抗素子3を備え、第2のMOSFET2のソースと第1の可変抵抗素子3の他端との接続点をソース端子Sとし、第1及び第2のMOSFETの共通接続したドレイン、共通接続したゲート、共通接続したバックゲートをそれぞれドレイン端子D、ゲート端子G、バックゲート端子Bとするモデルを作成し、モデリング対象の高耐圧MOSFETの電気特性データに基づき、第1の可変抵抗素子3の抵抗値を調整する。

(もっと読む)

半導体装置設計支援方法、半導体装置設計支援プログラム、及び半導体装置設計支援装置

【課題】バイアス条件によらず、モデルに対する解析精度を向上させる。

【解決手段】本発明による半導体回路の設計支援方法は、第1モデル22を用いて、プロセスパラメータが変動したときのデバイス特性の変動量102を算出するステップと、第2モデル23を用いて算出されたデバイス特性と実測値21との誤差に対して、変動量102で規格化するステップと、演算装置11が、規格化された誤差を用いて第2モデル23に対する解析を行うステップとを具備する。

(もっと読む)

回路シミュレーション装置、回路シミュレーション方法

【課題】MOSトランジスタの電気的特性を高精度に再現する。

【解決手段】図形情報生成手段と、パラメータ補正量計算手段と、回路シミュレーション手段とを備える回路シミュレーション装置によって以下の方法で、回路シミュレーションを行う。その方法は、チャネル領域とSTI領域との境界における、チャネル長方向の中点を特定する。そして、ゲート幅方向を縦方向とし、その中点を原点としてそのMOSトランジスタとそのMOSトランジスタの隣の拡散層との距離を縦方向隣接拡散層距離とするとき、その縦方向隣接拡散層距離を、そのチャネル長方向の位置Xに応じて変化する縦方向の距離の関数として特定する。その縦方向隣接拡散層距離の関数と重み付け関数とを掛け合わせた乗算式を生成し、その乗算式に基づいて、パラメータ補正量を算出する。

(もっと読む)

MOSトランジスタのシミュレーションパラメータの抽出方法

【課題】ゲートとドレインとの重なり部分の容量であるゲートオーバーラップ容量を精度よく抽出する。

【解決手段】本発明の一態様に係るシミュレーションパラメータの抽出方法は、コンタクトプラグ数のみが異なる複数のレイアウトパターンのそれぞれについて、所定のバイアス電圧下におけるゲート−ドレイン間の容量を測定して真のゲートオーバーラップ容量を含む測定値を求め、コンタクトプラグとゲートとの間の寄生容量を求めるためのモデルパラメータを変化させてシミュレーションを行って得られるコンタクトプラグとゲートとの間のコンタクト寄生容量を測定値から減算することによりゲートオーバーラップ容量演算値を求め、当該ゲートオーバーラップ容量演算値がコンタクトプラグの数によらず略一定となるモデルパラメータにおける当該ゲートオーバーラップ容量演算値を真のゲートオーバーラップ容量として抽出する。

(もっと読む)

半導体装置の解析方法、設計方法、設計支援プログラム、及び設計支援装置

【課題】トランジスタの高精度な解析及び設計を実現する。

【解決手段】チャネル領域54をチャネル方向(X方向)に離散化した複数の節点56の各々に、予め設定された濃度分布則に従ってチャネル方向(X方向)及び深さ方向(Z方向)の次元を有する不純物濃度N(x,z)を設定するステップと、不純物濃度N(x,z)の深さ方向(Z方向)の次元を削減する次元縮退によって、各節点56における表面ポテンシャルφS0を算出するステップと、各節点56間の相互作用を考慮して表面ポテンシャルφS0を修正するステップと、修正された表面ポテンシャルφSを用いてトランジスタ50の電気的特性を算出するステップと、算出された電気的特性と、予め用意された電気的特性の測定値22とが、所定の範囲内で一致する場合、不純物濃度N(x,z)をトランジスタ50のモデルパラメータ24として記憶装置13に記録するステップとを具備する。

(もっと読む)

モデルパラメータ決定装置、モデルパラメータ決定方法及びプログラム

【課題】半導体集積回路を製造するプロセスを変更した場合において、デバイスモデルによって変更後のプロセスにより製造された半導体素子を表すためにデバイスモデルに含まれるモデルパラメータを容易に決定できるようにする。

【解決手段】モデルパラメータ決定装置は、第1の製法により製造された半導体素子を特徴付ける第1の物理パラメータ群と、半導体素子の特性を表すためのデバイスモデルに含まれるモデルパラメータ群であって第1の製法により製造された半導体素子を表すための第1のモデルパラメータ群と、第2の製法により製造された半導体素子を特徴付ける第2の物理パラメータ群とを入力し、第2の製法により製造された半導体素子の特性を当該デバイスモデルによって表すためのモデルパラメータ群を、第1の物理パラメータ群及び第1のモデルパラメータ群並びに第2の物理パラメータ群に基づいて決定する。

(もっと読む)

ばらつきを考慮した半導体集積回路の設計方法

【課題】少数の離散的な電荷によって生じるトランジスタ特性のばらつきを考慮した半導体集積回路の設計方法を提供する。

【解決手段】単一の電荷が付加されることにより生じるトランジスタ特性の変位xの確率密度関数P1(x)を決定する工程と、P1(x)と、付加される電荷の個数nの出現確率と、を元に回路設計上想定すべき設計余裕Mを決定する工程と、を備える。単一の電荷が特性に影響を与えるほど微細なトランジスタを有する半導体集積回路においても、正確にばらつきが計算できる。

(もっと読む)

直列電界効果型トランジスタのパラメータフィッティング方法

【課題】 直列接続電界効果型トランジスタの回路モデルパラメータのフィッティング方法に関し、多段直列接続電界効果型トランジスタの回路モデルパラメータの効率的な抽出手順を提供し、モデル化を実施可能にする。

【解決手段】 多段直列接続電界効果型トランジスタの評価テスト用デバイスを用意し、複数のゲート電極に印加する電圧を制御して電気特性を評価し、パラメータ変数の基準値を孤立電界効果型トランジスタのモデル変数で設定し、さらに、パラメータ変数の微小変動分を加える形で回路モデルを作成し、次いで、評価した電気特性の多数のバイアス点とパラメータ変数の微小変動分の関係を、評価関数で評価し、評価関数を最小化することで微小変動分の変数の最適解を求め、最適解を多数の多段直列接続電界効果型トランジスタの評価テスト用デバイスについて求めてレイアウト変数の関数としてモデル化する。

(もっと読む)

シミュレーション方法、情報処理装置およびプログラム

【課題】既存の劣化モデル式に比べて、評価対象のトランジスタの適用範囲を広くしたシミュレーション方法を提供する。

【解決手段】情報処理装置が実行するシミュレーション方法であって、ゲート電圧、ドレイン電圧およびバックバイアス電圧の3種の電圧についてトランジスタの基準劣化率における寿命の電圧依存性のデータを記述したテーブル、または、3種の電圧についてトランジスタの基準時間における劣化率の電圧依存性のデータを記述したテーブルによりストレス時間と劣化率との関係式を求め、劣化後のドレイン電流について基準劣化率における実測データ、特定のトランジスタモデルの初期状態のドレイン電流および関係式に基づいた、ドレイン電流の変化を示す情報の3種の電圧の依存性を記述したテーブルを用いて、ドレイン電流の変化量を劣化率に対応して算出するものである。

(もっと読む)

モデルパラメータ抽出プログラム

【課題】既存回路シミュレータに設定すべきモデルパラメータの値の決定を客観的にできるようにする。

【解決手段】本方法は、入力変数としてデバイス寸法と端子電圧とを含み、係数としてモデルパラメータを含む、電気特性を計算するモデル式におけるモデルパラメータが最適化パラメータとして設定され、各点誤差の平均値である最適化誤差が最適化指標として設定される最適化アルゴリズムに従って、最適化誤差を最小化するモデルパラメータを探索する処理の過程で、モデルパラメータ値セットと、デバイス寸法の代表値セット毎の各点誤差と、最適化誤差と特定する工程と、上記代表値のセット毎に各点誤差が最小となるモデルパラメータ値セットをモデルパラメータの最適値セットとして特定する工程と、各モデルパラメータについて、当該モデルパラメータの最適値を近似するためのマップ関数の係数を、近似アルゴリズムに従って算出する工程とを含む。

(もっと読む)

モデルパラメータ抽出装置およびモデルパラメータ抽出方法

【課題】回路シミュレーションの精度の向上。

【解決手段】測定点の電気特性を示す測定データを入力する入力部10と、入力された測定データが存在している測定点について、入力された測定データに基づいて、測定点の電気特性を近似する第1近似関数式を作成する第1近似関数式作成部201と、入力された測定データが不足している測定点について、第1近似関数式作成部201によって作成された第1近似関数式を修正して、測定点の電気特性を近似する第2近似関数式を作成する第2近似関数式作成部202と、第1および第2近似関数式作成部201,202によって作成された第1および第2近似関数式に基づいて、測定点の電気特性の近似値を算出する近似値算出部30と、算出された近似値を含むモデルパラメータセットを生成するモデルパラメータセット生成部80と、生成されたモデルパラメータセットを出力する出力部90と、を備える。

(もっと読む)

パラメータ抽出方法及び装置

【課題】電力変換回路に用いられる電界効果型トランジスタの等価回路モデルにおけるパラメータを比較的簡単な方法において高精度に抽出することにより、高精度な回路シミュレーションが行える環境を提供する。

【解決手段】電力変換回路に用いられる電界効果型トランジスタの等価回路モデルにおいて、ゲート−ソース間容量Cgs、ゲート−ドレイン間容量Cgd、及びチャネル電流源Ichを、電界効果型トランジスタの誘導性負荷におけるスイッチング波形から抽出する。

(もっと読む)

半導体装置の解析及び設計装置、及び半導体装置の解析及び設計方法

【課題】より精密な半導体装置の解析及び設計を可能とする。

【解決手段】半導体装置の解析及び設計装置は、トランジスタの構成情報と電気特性の測定値とを関連付けて格納する記憶部2と、第1トランジスタのチャネル領域を複数の領域に分割し、各領域の不純物濃度をパラメータとするパラメータ設定部11と、パラメータに基づいてチャネル領域の両端領域での不純物濃度を減少させた実効不純物濃度を算出し、実効不純物濃度を用いたポアソン方程式で計算された表面ポテンシャルから第1トランジスタの電気特性の第1計算値を求める素子特性計算部12と、記憶部2から読み出した測定値と第1計算値とが一致する場合、当該パラメータを第1トランジスタのパラメータとして、記憶部2に構成情報と関連付けて格納する判定部13とを具備する。パラメータ設定部11と素子特性計算部12とは、第1計算値と測定値とが一致するまで動作を実行する。

(もっと読む)

MOSトランジスタの模擬回路

【課題】MOSトランジスタの直流特性を精度良くシミュレーションできるMOSトランジスタの模擬回路を提供すること。

【解決手段】電圧制御型電圧源EGD1(10)は、シミュレーション結果としてのドレイン―ソース間電圧VDSとドレイン電流IDとが、それぞれ実測のドレイン―ソース間電圧VDSとドレイン電流IDに一致するように、電圧制御型電圧源EGD1(10)の出力電圧V1を設定する。この電圧制御型電圧源EGD1(10)による電圧変換は、式で実現してもよく、或いはテーブルを参照することで実現しても良い。

(もっと読む)

設計支援装置、プログラム、半導体装置の設計方法、及び半導体装置の製造方法

【課題】アンテナ比の上限値をゲート絶縁膜の膜厚に基づいて変える場合に、アンテナ比の上限値を具体的に設定することができるようにする。

【解決手段】この設計支援装置は、半導体装置の設計を支援する装置であり、ゲート膜情報取得部260、及び上限アンテナ比設定部280を備える。ゲート膜情報取得部260は、設計された半導体装置が有するゲート絶縁膜の膜厚を取得する。上限アンテナ比設定部280は、ゲート電極のアンテナ比の上限を設定するが、ゲート膜情報取得部260が取得した膜厚によってアンテナ比の上限を異ならせる。このため、設計者はアンテナ比の上限値をゲート絶縁膜の膜厚に基づいて変える場合に、アンテナ比の上限値を具体的に設定することができる。

(もっと読む)

回路シミュレーション方法、回路シミュレーション装置、及びプログラム

【課題】MOSトランジスタのチャネル領域に印加される応力を適切に考慮し、精度が高い回路シミュレーションを行う。

【解決手段】対象MOSトランジスタのレイアウト寸法を示す図形情報19を生成するステップ、パラメータ変調量20を計算するステップ、回路シミュレータに与えられたトランジスタモデルパラメータ17をパラメータ変調量20に応じて修正し回路シミュレーションを行うステップ、とを具備。パラメータ変調量20の計算は、MOSトランジスタのチャネル領域に作用する応力を表す応力モデル式を含んでいる。応力モデル式は、応力の大きさが、MOSトランジスタのチャネル領域が形成されている活性領域から隣接する活性領域までの距離Sdの増加に対して単調に減少、隣接距離Sdが無限に大きい場合に一定値に収束、応力の隣接距離Sdに対する微分係数の大きさが単調に減少、前記微分係数が隣接距離Sdが無限に大きい場合に0に収束する。

(もっと読む)

パワー半導体素子の評価方法および評価装置

【課題】 自己発熱していない状態のパワー半導体素子の電流・電圧特性を、比較的簡易な手法により精度良く得ることのできるパワー半導体素子の評価方法および評価装置を実現する。

【解決手段】 自己発熱状態の評価対象LDMOS4の電流・電圧特性を測定し(S1)、自己発熱していない状態におけるドレイン電流値をId0、S1により測定されたドレイン電流値をId、S1における測定開始時のパワー半導体素子の絶対温度をTo、ドレイン電圧(Vd)を上昇させたときの温度上昇分をΔT、n=1.5〜2とした場合に、次式、Id0=Id×((To+ΔT)/To)nを用いて自己発熱していないときの電流値Id0を求め、評価対象LDMOS4の自己発熱していない状態における電流・電圧特性を演算する(S2)。

(もっと読む)

MOSFET集積回路におけるプロセスによって誘起される性能変動の補償方法

MOSFET集積回路における、プロセスによって誘起される閾値電圧及び駆動電流の変動を自動的に補償する方法。前記方法の第1ステップは、アレイから解析対象のトランジスタを選択することである。前記方法は、アレイの複数のトランジスタに対して所望のループ処理を行う。次に、選択されたトランジスタの設計を解析する。この解析においては、近隣のレイアウトによって誘起される閾値電圧の変動を決定する工程と、近隣のレイアウトによって誘起される駆動電流の変動を決定する工程とが含まれる。前記方法は、次に、トランジスタのゲート長を変更することにより、何れかの決定された変動に対して補償を行う。前記方法には、更に、コンタクトの間隔を変更することにより補償が不十分な点を特定する工程を含めることができる。  (もっと読む)

(もっと読む)

接合位置の検出方法

【課題】トランジスタ等のデバイス特性を精確に予測、制御し、特定部位の不良解析を行う、微細な半導体デバイスの半導体基板内のPN接合位置を検出する方法を提供する。

【解決手段】本発明の接合位置の検出方法は、半導体基板にて、P型不純物領域と、N型不純物領域との接合位置を検出する方法であり、観察対象の断面を露出させてサンプルを作成する断面露出工程と、断面を洗浄処理する断面処理工程と、断面に遷移金属を堆積させる堆積工程と、サンプルを加熱し、断面の半導体と遷移金属との合金を形成する第1熱処理工程と、過酸化水素水を含む溶液に、サンプルを浸漬する第1浸漬工程と、第1浸漬工程後にサンプルを加熱し、合金化反応を促進する第2熱処理工程と、フッ酸を含む溶液に、サンプルを浸漬し、合金をエッチングする第の浸漬工程と、P型不純物領域とN型不純物領域との合金のエッチング状態を観察し、接合界面を検出する検出工程とを有する。

(もっと読む)

半導体装置の評価方法及び半導体装置の設計方法

【課題】 半導体装置の評価方法及び半導体装置の設計方法に関し、シミュレーションにおいて同時に扱うパラメータを見掛け上少なくして、モデル式の見通しを良くするとともに、シミュレーション効率を高める。

【解決手段】 単体のMOSFETにおいて、実効的反転層移動度をμeff 、実効チャネル幅をWeff 、実効チャネル長をLeff 、単位面積当たりのゲート絶縁膜容量をCOX、実効的ゲート電圧をVgeff、Vgeff=0の時の実効的反転層移動度をμ0 とした場合のU0 =μ0 Weff COX/Leff で、実効一次移動度減衰係数をΘ1eff、二次移動度減衰係数をΘ2 、しきい値電圧をVth、及び、相補コンダクタンスをgm とした場合に、YをY≡Ids(gm )-1/2とするとともに、相関を求める一方の変数として1/Y2 を含むモデル式を用い、見掛け上のフィッティングパラメータを3個以下とする。

(もっと読む)

1 - 20 / 41

[ Back to top ]