Fターム[5F152AA13]の内容

Fターム[5F152AA13]に分類される特許

1 - 20 / 273

貼り合わせSOIウェーハの製造方法

【課題】 本発明は、SOI層の膜厚の面内均一性の良好なSOIウェーハを製造する方法を提供することを目的とする。

【解決手段】 イオン注入層が形成されたボンドウェーハのイオン注入された側の表面とベースウェーハの表面とを絶縁膜を介して貼り合わせた後、前記ボンドウェーハの一部を前記イオン注入層で剥離して、貼り合わせSOIウェーハを作製し、その後、平坦化処理を行う貼り合わせSOIウェーハの製造方法であって、

前記剥離後の貼り合わせSOIウェーハに対し、前記SOI層表面の周辺部の自然酸化膜が除去され、中央部の自然酸化膜が残存するように、水素ガスを含む雰囲気でRTA処理を行い、前記中央部に自然酸化膜が残存した貼り合わせSOIウェーハに対し、前記SOI層の面内膜厚レンジが1.5nm以下となるように前記平坦化処理を行うことを特徴とする貼り合わせSOIウェーハの製造方法。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板の主面に形成した溝部表面へのイオン注入量やイオン注入深さのバラつきを抑え、イオンが注入されたドーパンド領域を活性化して、厚み、イオンドープ量、活性化状態がほぼ均一なドーパンド層を形成できる半導体装置の製造方法を提供する。

【解決手段】半導体基板の主面に溝部を形成し、該溝部を形成した半導体基板の主面側にイオンを注入した後、イオンが注入されたドーパンド領域にレーザを照射してアニール処理を行う半導体装置の製造方法であって、前記ドーパンド領域にイオンを注入する前に、前記溝部の側面にレーザを照射して、該溝部の側面の表面段差を平滑化する。

(もっと読む)

半導体装置の作製方法

【課題】複数のトランジスタが高集積化された素子の少なくとも一のトランジスタに、作製工程数を増加させることなくバックゲートを設ける半導体装置を提供する。

【解決手段】複数のトランジスタが上下に積層されて設けられた素子において、少なくとも上部のトランジスタ102は、半導体特性を示す金属酸化物により設けられ、下部のトランジスタ100が有するゲート電極層を上部のトランジスタのチャネル形成領域と重畳するように配して、ゲート電極層と同一の層の一部を上部のトランジスタ102のバックゲートBGとして機能させる。下部のトランジスタ100は、絶縁層で覆われた状態で平坦化処理が施され、ゲート電極が露出され、上部のトランジスタ102のソース電極及びドレイン電極となる層に接続されている。

(もっと読む)

ラインビームとして成形されたレーザと基板上に堆積された膜との間の相互作用を実現するためのシステム及び方法

【課題】ラインビームとして成形されたレーザとの相互作用に対して膜を位置決めし、かつ例えばアモルファスシリコン膜を溶融させて例えば薄膜トランジスタ(TFT)を製造するために膜を結晶化するように成形ラインビームのパラメータを制御するためのシステム及び方法を提供する。

【解決手段】基板上に堆積されたアモルファスシリコンのような膜を選択的に溶融させるためのレーザ結晶化装置及び方法。装置は、膜を溶融させる際に使用される伸張レーザパルスを生成するための光学システムを含むことができる。本発明の実施形態の更に別の態様では、レーザパルスを伸張するためのシステム及び方法を提供する。別の態様では、ビーム経路に沿ったある位置でパルスレーザビーム(伸張又は非伸張)の発散を予め決められた範囲に維持するためのシステムを提供する。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体膜を含むトランジスタの作製工程において、非晶質酸化物半導体膜を形成し、該非晶質酸化物半導体膜に酸素を導入して酸素を過剰に含む非晶質酸化物半導体膜を形成する。該非晶質酸化物半導体膜上に酸化アルミニウム膜を形成した後、加熱処理を行い該非晶質酸化物半導体膜の少なくとも一部を結晶化させて、結晶性酸化物半導体膜を形成する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルからの読み出しのために基準電位より低い電位を出力する機能を有する電位切り替え回路を備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ162、トランジスタ162と異なる半導体材料を用いた読み出し用トランジスタ160及び容量素子164を含む不揮発性のメモリセルにおいて、メモリセルへの書き込みは、書き込み用トランジスタ162をオン状態とすることにより、書き込み用トランジスタ162のソース電極(またはドレイン電極)と、容量素子164の電極の一方と、読み出し用トランジスタ160のゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタ162をオフ状態とすることにより、ノードに所定量の電荷を保持させることで行う。また、読み出し用トランジスタ160として、pチャネル型トランジスタを用いて、読み出し電位を正の電位とする。

(もっと読む)

半導体装置および当該半導体装置の作製方法

【課題】電気的特性の安定した酸化物半導体膜を用いることにより、半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供すること。また、結晶性の高い酸化物半導体膜を用いることにより、移動度の向上した半導体装置を提供すること。

【解決手段】表面粗さの低減された絶縁膜上に接して、結晶性を有する酸化物半導体膜を形成することにより、電気的特性の安定した酸化物半導体膜を形成することができる。これにより、半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供することができる。さらに、移動度の向上した半導体装置を提供することができる。

(もっと読む)

基板上のフィルム領域を処理して、こうした領域内及びその端部領域をほぼ均一にするレーザ結晶化プロセス及びシステム、及びこうしたフィルム領域の構造

【課題】薄膜フィルム試料を処理するシステム、並びに薄膜フィルム構造を提供する。

【解決手段】フィルム試料170の一区画の特定部分の第1部分を融解させるべく照射ビームパルスの第1パルスの第1小ビームで照射して、この第1部分が少なくとも部分的に融解して自ずと再凝固して結晶化し、それぞれの隣接する第1部分どうしの間に第1未照射部分が残る。特定部分の第1小ビームによる照射の後に、この特定部分を、この特定部分の第2部分を融解させるべく照射ビームパルスの第2パルスの第2小ビームで再び照射して、この第2部分が少なくとも部分的に融解して自ずと再凝固して結晶化し、それぞれの隣接する第2部分どうしの間に第2未照射部分が残る。再凝固して結晶化した第1部分及び前記第2部分は、フィルム試料の領域内で互いに間に入り合う。これに加えて、第1部分が第1画素に対応し、第2部分が第2画素に対応する。

(もっと読む)

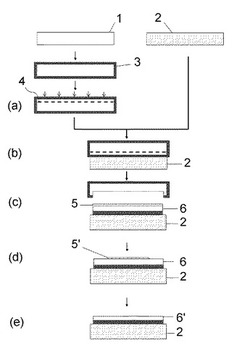

SOI基板、およびSOI基板の作製方法

【課題】単結晶シリコン膜などの半導体膜が、支持基板から剥がれることを防止するSOI基板の作製方法を提供する。また、当該方法を用いることで、SOI基板作製における歩留まりを向上させ、生産コストを削減する。

【解決手段】半導体基板に絶縁膜を形成し、加速されたイオンを半導体基板に照射することにより、半導体基板中に脆化領域を形成し、半導体基板と支持基板とを、絶縁膜を介して貼り合わせ、脆化領域において、半導体基板を分離して、支持基板上に絶縁膜を介して半導体膜を形成し、半導体膜上にマスクを形成し、半導体膜の一部及び絶縁膜の一部をエッチングすることにより、半導体膜の周端部が、絶縁膜の周端部の内側に位置するように、半導体膜及び絶縁膜を形成する、SOI基板の作製方法である。

(もっと読む)

SOI基板の作製方法

【課題】欠陥の少ない半導体層を得ること、及び信頼性の高い半導体装置を得る。

【解決手段】半導体基板中に、H2O+が水素イオン(H3+)に対して3%以下、好ましくは0.3%以下であるイオンビームを照射することにより、前記半導体基板中に脆化領域を形成し、前記半導体基板の表面及びベース基板の表面を対向させ、接触させることにより、前記半導体基板及び前記ベース基板を貼り合わせ、貼り合わせた前記半導体基板及び前記ベース基板を加熱し、前記脆化領域において分離させることにより、前記ベース基板上に半導体層を形成するSOI基板の作製に関する。

(もっと読む)

SOI基板の作製方法

【課題】照射された水素イオンの単結晶半導体基板からの脱離を抑制する。

【解決手段】半導体基板中に炭素イオンを照射し、当該炭素イオンが照射された半導体基板中に、水素イオンを照射することにより、当該半導体基板中に脆化領域を形成し、当該半導体基板の表面及びベース基板の表面を対向させ、接触させることにより、当該半導体基板及び当該ベース基板を貼り合わせ、貼り合わせた当該半導体基板及び当該ベース基板を加熱し、当該脆化領域において分離させることにより、当該ベース基板上に半導体層を形成するSOI基板の作製に関する。

(もっと読む)

SOI基板の作製方法

【課題】膜厚の均一な半導体層を有するSOI基板を得る。

【解決手段】半導体基板の第1の面を研磨して、当該第1の面を平坦化し、当該半導体基板の当該第1の面と反対側の面である第2の面にイオンを照射することにより、当該半導体基板中に脆化領域を形成し、当該半導体基板の第2の面及びベース基板の表面を対向させ、接触させることにより、当該半導体基板及び当該ベース基板を貼り合わせ、貼り合わせた当該半導体基板及び当該ベース基板を加熱し、当該脆化領域において分離させることにより、当該ベース基板上に半導体層を形成するSOI基板の作製に関する。当該SOI基板の作製においては、当該半導体層の膜厚の標準偏差をσとし、3σが1.5nm以下である。

(もっと読む)

半導体素子のための緩衝化基板

【課題】製造時間と製造価格を増加することなく多結晶シリコン粒径の微小化と均一化を

行なうための技術を提供する。

【解決手段】基板100上に形成したシリコン層104をレーザビーム106の照射によ

って結晶化して多結晶シリコン層108を得る半導体装置などに用いられ、基板100と

シリコン層104との間にバッファ層102が形成されている。バッファ層102を有す

るこのようなバッファ化基板において、該バッファ層102は、基板100の限界温度よ

りも高い融点を有し、さらに、シリコン層104の結晶化に際し、バッファ層102上に

均一なシリコン結晶粒子を形成するためシリコン層104の核生成密度を規定し、かつシ

リコン層104の結晶化過程における等方粒成長の基礎として機能する。

(もっと読む)

半導体記憶装置

【課題】メモリデータを外部回路を用いずに、コピーを行う半導体記憶装置を提供することを課題とする。

【解決手段】複数のメモリセルの第一端子が共通接続されたビット線と、ビット線に接続され、読み出し時にビット線を特定の電位にプリチャージするプリチャージ回路と、メモリセルから読み出したデータ、もしくはメモリセルへの書き込みデータを一時的に保持する容量素子を有するデータ保持回路と、データ保持回路で保持しているデータの反転データをビット線に出力する反転データ出力回路とを有し、反転データ出力回路は、データ保持回路で保持しているデータの反転データの出力を制御する手段を有する構成とする。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】絶縁層上に結晶性の良好な半導体層を形成することができる、半導体装置の製造方法を提供する。

【解決手段】絶縁層41上に厚さ4nm〜1μmの非晶質の半導体層43を形成する工程と、この半導体層43に対して、波長が350nm〜500nmの範囲内のエネルギービームを照射することにより、半導体層43を結晶化させる工程とを含んで、半導体装置を製造する。

(もっと読む)

半導体装置の製造方法

【課題】多結晶シリコン層の表面平坦性を向上できる半導体装置の製造方法を提供する。

【解決手段】本実施形態によれば、半導体装置の製造方法は、基板上に非晶質シリコン膜を形成する工程と、前記非晶質シリコン膜を結晶化して多結晶シリコン膜を形成する工程と、プラズマドーピング法を用いて、前記多結晶シリコン膜にイオンを注入する工程と、前記イオンを注入した前記多結晶シリコン膜の表面を研磨する工程と、を備える。

(もっと読む)

SOI基板の作製方法及び半導体装置の作製方法

【課題】単結晶半導体層のテーパー形状を有する端部の特性を良好にすることを課題とする。

【解決手段】加速されたイオンを単結晶半導体基板に照射することによって、単結晶半導体基板中に脆化領域を形成し、単結晶半導体基板とベース基板とを、絶縁膜を介して貼り合わせ、脆化領域において単結晶半導体基板を分離して、ベース基板上に絶縁膜を介して第1の単結晶半導体層を形成し、第1の単結晶半導体層に対してドライエッチングを行って、端部の形状がテーパー形状である第2の単結晶半導体層を形成し、第2の単結晶半導体層の端部に対して、ベース基板側の電位を接地電位としたエッチングを行う。

(もっと読む)

結晶性半導体膜の作製方法

【課題】ビームスポットの面積を飛躍的に広げ、結晶性の劣る領域の占める割合を低減することができるレーザ照射装置の提供を課題とする。また連続発振のレーザ光を用いつつ、スループットをも高めることができる、レーザ照射装置の提供を課題とする。さらに本発明は、該レーザ照射装置を用いたレーザ照射方法及び半導体装置の作製方法の提供を課題とする。

【解決手段】高調波のパルス発振の第1のレーザ光により溶融した領域に、連続発振の第2のレーザ光を照射する。具体的に第1のレーザ光は、可視光線と同程度かそれより短い波長(890nm以下程度)を有する。第1のレーザ光によって半導体膜が溶融することで、第2のレーザ光の半導体膜への吸収係数が飛躍的に高まり、第2のレーザ光が半導体膜に吸収されやすくなる。

(もっと読む)

薄膜トランジスタの製造方法、薄膜トランジスタ、および表示装置

【課題】信頼性を向上させると共に、電気的特性を改善することができる薄膜トランジスタの製造方法を提供する。

【解決手段】ガラス基板11上に成膜された非晶質シリコン膜20に、ガラス基板11の裏面側からレーザ光を照射することによって、縦成長モードで多結晶シリコン膜30を形成する。多結晶シリコン膜30は、溶融した半導体の表面に高い密度で形成された種結晶からガラス基板11側に向かって固化することにより形成される。これにより、多結晶シリコン膜30の表面付近には、微結晶シリコン領域を多く含む不完全結晶層32が形成される。そこで、不完全結晶層32をエッチングにより除去して、多結晶シリコン膜33を形成し、多結晶シリコン膜33を活性層とするTFTを製造する。

(もっと読む)

1 - 20 / 273

[ Back to top ]