Fターム[5F152CE34]の内容

再結晶化技術 (53,633) | 被結晶化層 (7,497) | 元素が導入されたもの(結晶化直前の状態) (601) | 結晶化制御用 (158)

Fターム[5F152CE34]の下位に属するFターム

触媒元素 (136)

Fターム[5F152CE34]に分類される特許

1 - 20 / 22

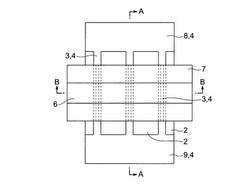

半導体装置およびその製造方法

【課題】高性能でかつばらつきの少ないナノワイヤトランジスタを備えた半導体装置およびその製造方法を提供する。

【解決手段】半導体基板上に第1絶縁膜を形成する工程と、第1絶縁膜上に設けられ、第1領域と第1領域よりも幅の広い第2および第3領域とを有しこれらの第2および第3領域の少なくとも一方が第1領域に接続するように構成された第1半導体層と、第1半導体層の上面に設けられるマスクと、を形成する工程と、マスクを用いて、前記第1半導体層の第1領域の側面にイオン注入を行う第1イオン注入を行う工程と、イオン注入を行った後に、第1熱処理を行う工程と、マスクを除去した後、第1半導体層の前記第1領域の少なくとも側面にゲート絶縁膜を形成する工程と、ゲート絶縁膜上にゲート電極を形成する工程と、ゲート電極の、第2および第3領域側の側面に絶縁体のゲート側壁を形成する工程と、少なくとも第1半導体層の第2および第3領域に第2イオン注入を行う工程と、とを備えている。

(もっと読む)

半導体膜、半導体素子、半導体装置およびそれらの作製方法

【課題】特性が安定した半導体膜を提供することを目的の一とする。または、特性が安定した半導体素子を提供することを目的の一とする。または、特性が安定した半導体装置を提供することを目的の一とする。

【解決手段】具体的には、絶縁性の表面に一方の面を接する第1の結晶構造を有する結晶を含む種結晶層(シード層)と、当該種結晶層(シード層)の他方の面に異方性の結晶が成長した酸化物半導体膜を有する構成とすれば良く、このようなヘテロ構造とすることにより、当該半導体膜の電気特性を安定化することができる。

(もっと読む)

多結晶シリコン層とその製造方法、該多結晶シリコン層を利用した薄膜トランジスタ及び該薄膜トランジスタを備えた有機発光表示装置

【課題】多結晶シリコン層、その製造方法、多結晶シリコン層を利用した薄膜トランジスタ及び薄膜トランジスタを備えた有機発光表示装置を提供する。

【解決手段】基板10上のバッファ層11上に非晶質シリコン層12を形成する工程と、非晶質シリコン層12上に触媒金属層を1011ないし1015原子/cm2の密度を有するように形成する工程と、触媒金属層の触媒金属が非晶質シリコン層12に拡散して非晶質シリコン層12とバッファ層11との界面でピラミッド形態の結晶化シードを形成し、結晶化シードによってシリコン結晶が成長して多結晶シリコン層22を形成するように、非晶質シリコン層12を熱処理する工程と、を含むシリコン層の結晶化方法である。

(もっと読む)

半導体装置の製造方法

【課題】不純物拡散領域の抵抗値のばらつきを抑制しうる半導体装置の製造方法を提供する。

【解決手段】半導体層にドーパント不純物を添加し、0.1秒〜10秒の活性化熱処理を行う。次いで、半導体層にイオン注入を行い、半導体層のドーパント不純物が添加された領域をアモルファス化する。次いで、0.1ミリ秒〜100ミリ秒の活性化熱処理を行い、アモルファス化した半導体層を再結晶化することにより、半導体層にドーパント不純物の拡散領域を形成する。

(もっと読む)

炭化珪素基板の製造方法

【課題】製造工程を簡略化すると共に、表層部にらせん転位が存在することを抑制することができるSiC基板の製造方法を提供する。

【解決手段】炭化珪素からなり、主表面および当該主表面の反対面である裏面を備え、らせん転位1を表層部2aに含む欠陥含有基板2を用意する工程と、欠陥含有基板2のうち主表面に外力を印加することにより表層部2aの結晶性を低下させる第1外力印加工程と、外力印加工程の後、欠陥含有基板2を熱処理することにより表層部2aの結晶性を回復させる第1熱処理工程と、を含む製造方法とする。

(もっと読む)

薄膜トランジスタ及びその製造方法並びに半導体装置

【課題】薄膜トランジスタのリーク特性を維持しつつ、オン電流を大幅に改善することができる薄膜トランジスタ及びその製造方法並びに半導体装置の製造方法を提供すること。

【解決手段】半導体薄膜を形成する工程と、前記半導体薄膜にシリコンを注入する工程と、チャネル形成領域とソース形成領域及びドレイン形成領域との間にそれぞれ位置するLDD形成領域上にマスクを形成する工程と、前記LDD形成領域上にマスクを形成した半導体薄膜上にシリコンを注入する工程と、前記半導体薄膜を熱処理により結晶化する工程と、を有する薄膜トランジスタの製造方法とした。

(もっと読む)

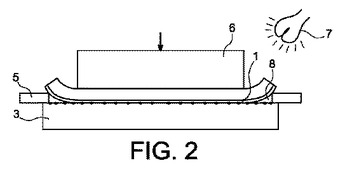

層の結晶化方法

異なる構造の薄膜(1)に対するアモルファス又は結晶性構造の結晶(3)の転移は、結晶に薄膜を適用し、それを結晶化するためにそれを焼き鈍しするための加圧(6)及び加熱(7)の組合せによって達成され得る。特徴的に、ブロック(5)は、薄膜を屈曲させ、組立体のクラックを開始し、圧力が取り除かれた際に薄膜を開放するように端部に配置され、それによって結晶(3)を取り除き又はそれを破壊するための複雑な方法を取り除く。この方法は、いくつかの膜に使用される結晶(3)が結晶化されることを可能にし、達成される良好な製造率を可能にし、費用を削減する。  (もっと読む)

(もっと読む)

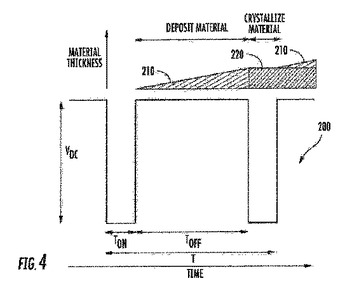

パルス堆積及び再結晶、並びに、結晶化/アモルファス材料を利用したタンデム太陽電池構造

基板上に材料を堆積及び結晶化する方法が開示され、特定の実施態様において、その方法は、堆積され、吹きつけられる種及びエネルギー輸送種を有するプラズマの生成を含んでもよい。第一の期間の間、基板にバイアス電圧は印加されず、プラズマ堆積を通じて種が基板上に堆積する。第二の期間の間、基板に電圧が印加され、堆積した種に向かって及び内部にイオンが引き付けられ、それにより堆積した層が結晶化する。このプロセスを十分な厚みが得られるまで繰り返すことができ、他の実施態様では、バイアス電圧又はバイアスパルス継続時間を変更して、生ずる結晶化の量を変えることができる。他の実施態様において、ドーパントを用いて、堆積した層をドープしてもよい。  (もっと読む)

(もっと読む)

貼り合わせウェーハの製造方法

【課題】貼り合わせ基板の活性層用ウェーハの表面に、結晶面が異なる領域を簡単に形成可能な貼り合わせウェーハの製造方法を提供する。

【解決手段】高エネルギ光を、活性層用ウェーハの素材は溶融しないが、吸光係数が高いアモルファスシリコンは溶融する条件で貼り合わせ基板の活性層用ウェーハ側の面に照射し、この窓部内のシリコンを溶融させて固化させる。このとき、アモルファスシリコンを単結晶シリコンに液相エピタキシーにより変質させれば、貼り合わせ基板の活性層用ウェーハの表面に、結晶面が異なる領域を簡単に形成できる。

(もっと読む)

半導体装置の製造方法、半導体装置、および電気光学装置

【課題】単結晶シリコン層を貼り付けた高価な基板や、触媒金属を拡散させたシリコン膜を用いなくても、トランジスター特性の優れた薄膜トランジスターを備えた半導体装置の製造方法、半導体装置、および電気光学装置を提供すること。

【解決手段】半導体装置の製造工程では、非晶質のシリコン膜1の一部の領域にゲルマニウムを導入して熱処理を行う。その結果、核形成用元素導入領域1sに結晶核が生成するとともに、かかる結晶核を起点として結晶粒が成長する。このため、シリコン結晶粒の位置制御が可能となり、チャネル領域1hに含まれる粒界の量を制御することができる。また、ゲルマニウムは、チャネル領域形成予定領域1iやその周辺の領域1k、1mなどに拡散しない。

(もっと読む)

アレイ基板

【課題】半導体層にゲルマニウムを添加した際、ゲート絶縁膜のリークによるTFT特性劣化を抑制する。

【解決手段】非晶質シリコンの固相成長の低温化を図るため、TFT33の半導体層35にゲルマニウムを添加し、かつゲート絶縁膜20bのゲートリーク電流を抑えるため、窒化物を主成分とするゲート絶縁膜20bを用いる。

(もっと読む)

半導体装置の製造方法

【課題】

本発明は、低温下で結晶性の良好な単結晶および多結晶を提供することを目的とする。また、本発明は、固相成長法を用い、信頼性の高い半導体装置を提供することを目的とする。

【解決手段】

本発明では、非晶質半導体薄膜を基板あるいは絶縁膜上に堆積するにあたり、特に、その膜を構成する主元素からなる非晶質膜の平均原子間隔分布が、単結晶の平均原子間隔分布にほぼ一致するように形成し、これに再結晶化エネルギーを付与し固相成長を行い単結晶半導体薄膜3を形成する。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】 ガラスやプラスチックなどの単結晶でない基体上に単結晶半導体薄膜を形成することで、任意の基体上に十分に動作速度の速いトランジスタを作製することを可能とする。また、それにより任意の基体上に集積回路を形成することを可能にする。

【解決手段】 基体上に基体全面に渡って結晶方位が揃った配向中間層を形成し、その上にアモルファス状態もしくは多結晶状態の半導体薄膜を形成し、その半導体薄膜を適切な条件でアニールすることによって、基体全面に渡って結晶方位が揃った半導体薄膜を形成する。

(もっと読む)

半導体記憶装置の製造方法

【課題】 固相成長に伴う欠陥領域の発生を制御することができ、回路を配置できない領域を最小限にとどめ、SOI結晶層を有効に活用することで製造コストの低減をはかる。

【解決手段】 半導体記憶装置の製造方法であって、シリコン基板上に形成された絶縁膜の複数箇所に開口部を設けた後、開口部が設けられた絶縁膜上及び該開口部内にアモルファスシリコン膜を形成し、次いで隣接する開口部間の中央付近でアモルファスシリコン膜を一方の開口部側と他方の開口部側とに分離する溝を形成し、次いで溝が形成されたアモルファスシリコン膜をアニールし、開口部をシードとして単結晶を固相成長させることによりシリコン単結晶層を形成し、次いでシリコン単結晶層上にメモリセルアレイを形成する。

(もっと読む)

多結晶半導体薄膜の製造方法、多結晶半導体薄膜、半導体装置及び表示装置

【課題】薄膜トランジスタのチャネル領域に用いた場合にそのキャリア移動度を高め、且つ、特性ばらつきを小さくする多結晶半導体薄膜の製造方法、多結晶半導体薄膜、半導体装置及び表示装置を提供する。

【解決手段】多結晶半導体薄膜の製造方法は、特定のエネルギー密度の結晶化エネルギーを特定方向に走査しながら付与することにより、所定領域の非晶質珪素膜の膜面に平行に{101}面が優先配向し、結晶化エネルギーの走査方向に{100}面が優先配向し、結晶化エネルギーの走査方向に対して直交する方向に{101}面が優先配向した結晶面を有する多結晶珪素の結晶核を形成する結晶核形成工程と、優先配向した結晶面に対応する領域以外の領域に非晶質珪素膜を形成する結晶核制御工程と、非晶質珪素膜に珪素膜の結晶化を助長する触媒物質を導入して膜面と略平行な方向に結晶成長させる結晶粒成長工程と、を備える。

(もっと読む)

半導体基板の製造方法および半導体基板

【課題】 2枚のウェーハの接合により、DSB構造を有する半導体基板を製造する場合において、接合界面を半導体基板側に残さないことによって、接合界面のボイド発生に起因する素子の歩留まり低下を解消することを可能とする半導体基板の製造方法および半導体基板を提供する。

【解決手段】 第1の半導体ウェーハ102表面に非晶質(アモルファス)半導体層120を形成する工程と、第2の半導体ウェーハ104表面に多孔質半導体層118を形成する工程と、非晶質半導体層120と多孔質半導体層118を重ね合わせた状態で、第1の半導体ウェーハ102と第2の半導体ウェーハ104とを接合する工程と、非晶質半導体層120を単結晶化する熱処理工程と、接合する工程において形成された半導体基板114を、多孔質半導体層118において分離する工程を有することを特徴とする半導体基板の製造方法および半導体基板。

(もっと読む)

半導体装置の接合形成方法およびそれにより作製された半導体装置

【課題】半導体装置の所望のソース/ドレイン接合深さの近傍にある、エンドオブレンジ(EOR)領域の存在の、負の影響を低減する。

【解決手段】装置とその装置の製造方法が記載され、それにより、装置がエンドオブレンジ欠陥から離れた浅い接合深さを有する。方法は、シリコンのような結晶半導体中に、第1深さまで、アモルファス領域を形成する工程と、これに続いて、例えば炭素のような置換型元素を、第1深さより浅い深さまで注入する工程とを含む。続いて領域は例えばリンやボロンのような適当なドーパントでドープされ、熱処理工程によりアモルファス領域が再結晶化される。

(もっと読む)

厚い歪みSOI基板における歪み設計

絶縁物上半導体(SOI)ウェハ(101)とともに用いることが好ましい半導体製造プロセス。ウェハの活性層(106)は2軸歪みであり、また第1の領域(110−1)と第2の領域(110−2)とを有する。第2の領域(110−2)をアモルファス化して、その歪み成分を変える。ウェハをアニールして、アモルファス半導体を再結晶化する。第1および第2のタイプのトランジスタ(150−1、150−2)を、第1の領域および第2の領域内にそれぞれ作製する。活性層の第3の領域(110−3)、あるいは第4の領域(110−4)を処理して、それらの歪み特性を変えても良い。犠牲の歪み構造(130)を、第3の領域を覆うように形成しても良い。歪み構造は圧縮であっても良い。ウェハのアニールを、歪み構造が所定の位置にある状態で行なう場合、その歪み特性が第3の活性層領域内に反映されても良い(110−3)。第4の活性層領域(110−4)のアモルファス化を、トランジスタ歪みの幅方向に平行に進み一軸応力を幅方向に生成するストライプ状に行なっても良い。  (もっと読む)

(もっと読む)

結晶質半導体膜およびその製造方法

【課題】 電気的特性が良好で、かつ、電気的特性のばらつきを抑制した結晶質半導体膜および前記結晶質半導体膜を容易に製造するための製造方法を提供する。

【解決手段】 本発明の結晶質半導体膜の製造方法は、多結晶半導体膜(120)を用意する工程と、多結晶半導体膜(120)の少なくとも一部の領域に所定の元素(130)を注入することにより、多結晶半導体膜(120)の結晶化率よりも低い結晶化率を有する非晶質化領域を多結晶半導体膜(120)の少なくとも一部の領域に形成する工程であって、所定のエネルギービーム(150)に対する非晶質化領域の吸収率が所定の方向に沿って連続的に変化するように所定の元素(130)を注入する、工程と、非晶質化領域に所定のエネルギービーム(150)を照射することにより、非晶質化領域を結晶化する工程とを包含する。

(もっと読む)

混合結晶配向のチャネル及びソース/ドレイン領域をもつ電界効果トランジスタ

【課題】 混合結晶配向のチャネル及びソース/ドレイン領域をもつ電界効果トランジスタを提供すること。

【解決手段】 ハイブリッド配向基板は、n型電界効果トランジスタ(nFET)が電子移動度に最適な半導体の配向内に配置され、p型電界効果トランジスタ(pFET)が正孔移動度に最適な半導体の配向内に配置される、相補型金属酸化膜半導体(CMOS)回路の製造を可能にする。本発明は、最適な半導体の配向内に完全に形成されたFETの性能利点が、デバイスのチャネルを最適な配向をもつ半導体内に配置することを必要とするだけで実現できることを開示する。様々な新しいFET構造体が説明され、その全ては、FETのチャネルは、FETのソース及び/又はドレインとは異なる配向を有するという特徴を備えている。これらの新しいFETを組み込むことができるハイブリッド基板は、その製造方法と共に説明される。

(もっと読む)

1 - 20 / 22

[ Back to top ]