Fターム[5F152CE38]の内容

再結晶化技術 (53,633) | 被結晶化層 (7,497) | 元素が導入されたもの(結晶化直前の状態) (601) | 堆積時に同時導入 (47)

Fターム[5F152CE38]に分類される特許

1 - 20 / 47

半導体シリコン膜及び半導体デバイス、並びにそれらの製造方法

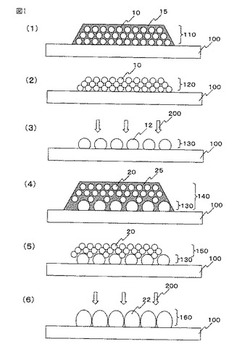

【課題】本発明の目的は、新規な半導体シリコン膜及びそのような半導体シリコン膜を有する半導体デバイス、並びにそれらの製造方法を提供することである。

【解決手段】本発明の半導体シリコン膜(160)は、複数の細長シリコン粒子(22)が短軸方向に隣接してなる半導体シリコン膜である。ここでは、細長シリコン粒子(22)は、複数のシリコン粒子の焼結体である。また、このような半導体シリコン膜(160)を製造する本発明の方法は、第1のシリコン粒子分散体を、基材(100)上に塗布し、乾燥し、光(200)を照射して、第1の半導体シリコン膜(130)を形成する工程、第2のシリコン粒子分散体を、第1の半導体シリコン膜(130)に塗布し、乾燥し、光(200)を照射する工程を含む。ここで、この方法では、第1のシリコン粒子分散体の第1のシリコン粒子の分散が5nm2以上である。

(もっと読む)

多結晶型太陽電池パネルおよびその製造方法

【課題】ドーパント含有シリコンインゴットを材料効率よく提供することで、より低コストな多結晶型シリコン太陽電池を提供する。

【解決手段】P型またはN型のドーパントを含有したシリコンターゲットを用意する工程Aと、P型またはN型のドーパントを含有したシリコンターゲットを利用して、基板表面にP型またはN型アモルファスシリコン膜をスパッタ成膜する工程Bと、P型またはN型アモルファスシリコン膜にプラズマを走査させて溶融後、再結晶化させてP型またはN型多結晶シリコン膜を形成する工程Cと、工程Cで形成されたP型多結晶シリコン膜に、N型のドーパントを含むガスによるプラズマに曝してPN接合を形成する、または工程Cで形成されたN型多結晶シリコン膜に、P型のドーパントを含むガスによるプラズマに曝してPN接合を形成する工程Dとを含む多結晶型太陽電池パネルの製造方法。

(もっと読む)

半導体膜、半導体素子、半導体装置およびそれらの作製方法

【課題】特性が安定した半導体膜を提供することを目的の一とする。または、特性が安定した半導体素子を提供することを目的の一とする。または、特性が安定した半導体装置を提供することを目的の一とする。

【解決手段】具体的には、絶縁性の表面に一方の面を接する第1の結晶構造を有する結晶を含む種結晶層(シード層)と、当該種結晶層(シード層)の他方の面に異方性の結晶が成長した酸化物半導体膜を有する構成とすれば良く、このようなヘテロ構造とすることにより、当該半導体膜の電気特性を安定化することができる。

(もっと読む)

多結晶型シリコン太陽電池パネルおよびその製造方法

【課題】pn接合が形成された多結晶シリコン膜を少工程かつ短時間で形成することで、安価な多結晶型太陽電池パネルを提供する。

【解決手段】n型またはp型にドーピングされたシリコンからなるターゲットを用いて、基板表面にアモルファスシリコン膜をスパッタ成膜する工程と;前記アモルファスシリコン膜の表層を、p型またはn型ドーパントをプラズマドーピングする工程と;前記プラズマドーピングされたアモルファスシリコン膜にプラズマを走査してアモルファスシリコン膜を溶融させ、かつ再結晶化させる工程と;を有する、多結晶型シリコン太陽電池パネルの製造方法。

(もっと読む)

多結晶型シリコン太陽電池パネルおよびその製造方法

【課題】pn接合が形成された多結晶シリコン膜を少工程かつ短時間で形成することで、安価な多結晶型太陽電池パネルを提供する。

【解決手段】n型またはp型にドーピングされたシリコンからなる粉体状のターゲットを用いて、基板表面にアモルファスシリコン膜をスパッタ成膜する工程と;前記アモルファスシリコン膜の表層を、p型またはn型ドーパントをプラズマドーピングする工程と;前記プラズマドーピングされたアモルファスシリコン膜にプラズマを走査してアモルファスシリコン膜を溶融させ、かつ再結晶化させる工程と;を有する、多結晶型シリコン太陽電池パネルの製造方法。

(もっと読む)

半導体装置の製造方法

【課題】ReRAM用のダイオードを形成するために、アモルファス半導体膜の表面に酸化膜が形成された場合であっても、アモルファス半導体膜を結晶化することが可能な半導体装置の製造方法を提供する。

【解決手段】基板101上に、下部電極層111とアモルファス半導体膜112を形成し、アモルファス半導体膜112上の自然酸化膜121を介して、還元性のある金属層113Aを含む上部電極層113を形成し、マイクロ波を用いたアニールにより、金属層113Aと酸化膜121を反応させて、酸化膜121を半導体へと還元する。また、アニールにより更に、金属層113Aと半導体112を反応させて、金属層113Aの構成元素と半導体112の構成元素とを含む反応生成物113Cを生成する。また、反応生成物113Cを結晶成長のためのシードとして、アモルファス半導体膜112を結晶成長させる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】良好な性能の半導体装置を低コストで提供する。

【解決手段】実施形態による半導体装置の製造方法は、非晶質シリコン膜を成膜する工程と、該非晶質シリコン膜の側面に種結晶を作成する工程と、マイクロ波を用いたアニーリングにより上記非晶質シリコン膜の膜厚の方向に直交する方向で上記非晶質シリコン膜の内部へシリコンを結晶成長させる工程と、を持つ。

(もっと読む)

半導体装置及びその製造方法

【課題】セレクターの形成にあたり、不純物の拡散を抑制しつつ、非晶質膜を結晶化させる方法を提供する。

【解決手段】第1の不純物が添加された第1の非晶質膜を堆積し、第1の非晶質膜の上に、第3の非晶質下層膜を堆積し、第3の非晶質下層膜の上に、微結晶を形成し、微結晶を覆うように、第3の非晶質下層膜の上に、第3の非晶質上層膜を堆積し、第3の非晶質上層膜の上に、第2の不純物が添加された第2の非晶質膜を堆積する。さらに、マイクロ波を照射することにより、第1の非晶質膜を結晶化して、第1導電型結晶層を形成し、第2の非晶質膜を結晶化して、第2導電型結晶層を形成し、第3の非晶質下層膜と第3の非晶質上層膜とを結晶化して、第3導電型結晶層を形成する。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】最大発振周波数fmaxを高くしてダイヤモンド電界効果トランジスタの特性を大きく向上させ、かつ電圧降下を小さく抑えることにより実用レベルに到達させること。

【解決手段】「ソース・ゲート電極間隔dSG、ゲート・ドレイン電極間隔dGDを狭くすること」と「ソース電極の厚さtS、ドレイン電極の厚さtDを厚くすること」とを両立させるために、ソース電極およびドレイン電極を、エッチング溶液を用いてエッチングする層とレジストを用いてリフトオフする層とに分けて形成する。これにより電極の逆メサ部を小さくすることができるため、ソース電極とゲート電極との間隔を小さくして最大発振周波数fmaxを上げ、かつソース電極およびドレイン電極の厚みを厚くして電圧降下を小さく抑えることができる。

(もっと読む)

ダイヤモンド半導体素子およびその製造方法

【課題】ダイヤモンド薄膜内に存在する結晶欠陥、不純物等を減少させ、高品質なダイヤモンド薄膜を作製可能なダイヤモンド薄膜作製方法を提供すること。

【解決手段】ダイヤモンドが安定な高圧力下でアニールを行う。これにより、結晶中に含まれる格子欠陥等が回復、除去され、ダイヤモンド結晶薄膜を高品質化する事ができる。「(ダイヤモンドが)安定な、安定に」とは、ダイヤモンドがグラファイト化せずにダイヤモンドの状態を保つ状態を指す。ダイヤモンドが安定にアニール出来る領域内でアニールを行う温度(アニール温度、とも呼ぶ)Tおよびアニールを行う圧力(アニール圧力、とも呼ぶ)Pが決定される。この領域は、図21に示される、P>0.71+0.0027TまたはP=0.71+0.0027Tを満たし、なおかつP≧1.5GPaの領域である。このような領域は、図21中の斜線部分である。

(もっと読む)

薄膜トランジスタ

【課題】イオン注入を行わずに低コストで製造できる構造形態を備えた薄膜トランジスタを提供する。

【解決手段】基板10上(又は第1下地膜11乃至第2下地膜12上)に設けられたポリシリコン半導体膜13と、ポリシリコン半導体膜13上に離間して設けられたソース電極15s及びドレイン電極15dと、ポリシリコン半導体膜13上にゲート絶縁膜14を介して設けられたゲート電極15gとを少なくとも有する。ポリシリコン半導体膜13は、面内方向にソース電極接続領域13s、チャネル領域13c及びドレイン電極接続領域13dを有し、チャネル領域13cにはドーパントが含まれておらず、ソース電極接続領域13s及びドレイン電極接続領域13dは基板10側からソース電極側及びドレイン電極側に向かってドーパント一定濃度層21とドーパント減少傾斜層22’とを有する。

(もっと読む)

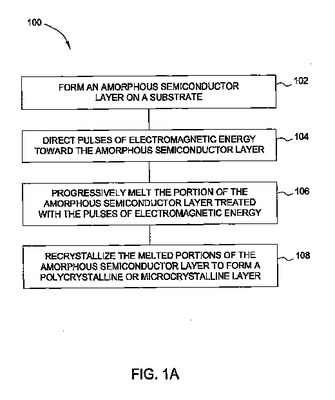

半導体用途のための結晶化処理

基板上に結晶半導体層を形成するための方法および装置が提供される。半導体層は気相堆積によって形成される。パルスレーザ溶融/再結晶化プロセスが半導体層を結晶層に変換するために実行される。レーザまたは他の電磁放射のパルスがパルス列に形成され、処置ゾーンにわたって均一に分配され、連続する隣接した処置ゾーンがパルス列にさらされて、堆積された材料を結晶材料に漸進的に変換する。  (もっと読む)

(もっと読む)

半導体装置の製造方法および製造装置

【課題】製造工数を増やすことなく、大粒径の多結晶シリコン膜を有する半導体装置を製造可能な製造装置、および、製造方法を提供する。

【解決手段】製造装置100は、反応室1と、ヒータ2と、圧力計3と、複数のガス導入管4a〜4gと、MFC5a〜5gと、ニッケル導入部6と、バルブ7a,7bと、ICP−MS8と、ガス排出管9と、APC10と、ポンプ11a,11bと、を備えている。製造装置100にニッケル導入部6を設けるため、製造工数を抑えて製造装置100内で大粒径の多結晶シリコン膜34の形成を行うことができ、製造コストを抑えることができる。

(もっと読む)

表示装置の製造方法および表示装置

【課題】微結晶化による非晶質シリコンの残留割合を下げ、かつ生産効率を向上することができる表示装置を提供すること。

【解決手段】表示装置の製造方法は、非晶質シリコンからなる第1の半導体層を形成する第1の半導体積層工程と、前記第1の半導体層の上面と接するとともに不純物が添加された第2の半導体層を形成する第2の半導体積層工程と、前記第2の半導体積層工程の後に行われ、前記第1の半導体層を加熱することにより前記第1の半導体層の少なくとも一部を微結晶化させる微結晶化工程と、を含む。

(もっと読む)

部分SOIウェーハの製造方法

【課題】活性層からバルク層に達した孔部で堆積中のアモルファスもしくは多結晶シリコンを単結晶化させる際に埋め込み酸化膜の領域での欠陥発生を抑制させる部分SOIウェーハの製造方法を提供する。

【解決手段】活性層を被う保護膜の一部に形成された窓部を通して、活性層と埋め込み酸化膜との各一部をエッチングして孔部を形成後、孔部にアモルファスシリコンを堆積させる。孔部内のアモルファスシリコンを、単結晶化させる場合に高エネルギ光の照射を行うことでエピタキシャル成長速度を速め、埋め込み酸化膜の領域を通過する際に発生する欠陥密度を抑制できる。

(もっと読む)

薄膜形成方法および薄膜形成装置

【課題】膜成長性を適切に制御することができ、均質性および機能性を向上させた薄膜を形成することができる薄膜形成方法を提供する。

【解決手段】基板2に滴下された薄膜形成材料を含む溶液の溶媒が揮発してなる結晶性薄膜5の形成方法であって、第1の溶液1を上記基板2の特定領域に滴下する第1の滴下工程と、第1の溶液1中に上記薄膜の成長核3が形成されるまで、第1の溶液1の溶媒を揮発させる第1の揮発工程と、第2の溶液4を上記特定領域に滴下して第1の溶液1と混合する第2の滴下工程と、第1の溶液1と第2の溶液4とが混合した溶液の溶媒を揮発させ、結晶性薄膜5を形成させる第2の揮発工程とを含んでおり、第1の滴下工程における第1の溶液1が含む上記薄膜形成材料の濃度は、第2の滴下工程における第2の溶液4が含む上記薄膜形成材料の濃度よりも低いことが望ましい。

(もっと読む)

貼り合わせウェーハの製造方法

【課題】貼り合わせ基板の活性層用ウェーハの表面に、結晶面が異なる領域を簡単に形成可能な貼り合わせウェーハの製造方法を提供する。

【解決手段】高エネルギ光を、活性層用ウェーハの素材は溶融しないが、吸光係数が高いアモルファスシリコンは溶融する条件で貼り合わせ基板の活性層用ウェーハ側の面に照射し、この窓部内のシリコンを溶融させて固化させる。このとき、アモルファスシリコンを単結晶シリコンに液相エピタキシーにより変質させれば、貼り合わせ基板の活性層用ウェーハの表面に、結晶面が異なる領域を簡単に形成できる。

(もっと読む)

エピタキシャルシリコンウェーハの製造方法

【課題】エピタキシャル成長時の加熱に伴うスリップが発生せず、ウェーハ表面のボイド欠陥に起因したエピタキシャル膜の表面粗さの低下も解消可能なエピタキシャルシリコンウェーハの製造方法を提供する。

【解決手段】単結晶シリコン製のシリコンウェーハの表面にアモルファスシリコン膜または多結晶シリコン膜を堆積後、この膜を高エネルギ光の照射で溶融、固化し、単結晶シリコンに変質させる。これにより、エピタキシャル膜の液層エピタキシャル成長を可能とし、エピ成長時の加熱に伴うスリップの発生を無くせる。しかも、仮にウェーハ表面にボイド欠陥が存在しても、溶融により、表面の平坦度が高いエピタキシャル膜が得られる。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタアレイ基板、及びそれらの製造方法、並びに表示装置

【課題】歩留まり向上が可能で、かつ品質向上につながる薄膜トランジスタ、薄膜トランジスタアレイ基板、及びそれらの製造方法、並びに表示装置を提供すること。

【解決手段】本発明に係る薄膜トランジスタの製造方法は、基板1上にゲート電極2を形成する工程と、ゲート電極2上にゲート絶縁膜3を形成する工程と、ゲート絶縁膜3上に、ゲート電極2の少なくとも一部と対向配置する半導体層10のパターン形成する工程と、半導体層10上にソース電極5、及びドレイン電極6を形成する工程と、ソース電極5、及びドレイン電極6をマスクとして、チャネル領域10Cに相当する半導体層10を所望の膜厚までエッチングする工程と、露出した半導体層10にレーザ光を照射する工程とを備える。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】相変化メモリやReRAMなどの記憶素子と半導体デバイスの積層により構成される半導体記憶装置を製造する際に、半導体デバイスと記憶素子の両方を高性能化し、半導体記憶装置の大容量化、高性能化、高信頼化を促進する。

【解決手段】選択素子を形成するポリシリコンをアモルファス状態で低温で成膜した後、レーザーアニールによる短時間熱処理で結晶化と不純物活性化を行う。レーザーアニールを行う際、結晶化を行うシリコンの下にある記録材料は、金属膜、または金属膜と絶縁膜により完全に覆われた状態であるため、アニール時の温度上昇を抑制でき、記録材料への熱負荷を低減できる。

(もっと読む)

1 - 20 / 47

[ Back to top ]