Fターム[5F152LL12]の内容

再結晶化技術 (53,633) | 半導体膜成長技術(半導体層) (1,668) | 成長技術 (1,654) | 液相 (55)

Fターム[5F152LL12]の下位に属するFターム

Fターム[5F152LL12]に分類される特許

1 - 20 / 23

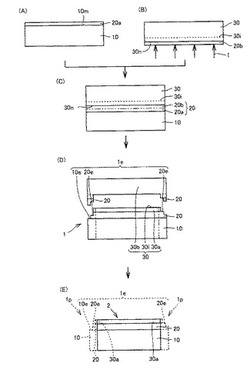

III族窒化物複合基板の製造方法

【課題】支持基板とIII族窒化物層との接合が良好なIII族窒化物複合基板の製造方法を提供する。

【解決手段】本III族窒化物複合基板の製造方法は、目標とする基板径より大きい径の主面10mを有する支持基板10と、目標とする基板径より大きい径の主面30nを有しその主面30nから所定の深さの位置にイオン注入領域30iが形成されたIII族窒化物基板30とを、中間層20を介在させて貼り合わせ、III族窒化物基板30をイオン注入領域30iにおいてIII族窒化物層30aと残りのIII族窒化物基板30bとに分離することにより、支持基板10上に中間層20を介在させてIII族窒化物層30aが接合された第1のIII族窒化物複合基板1を形成し、第1のIII族窒化物複合基板1の外周部を除去することにより目標とする基板径に等しい径の主面を有する第2のIII族窒化物複合基板2を得る。

(もっと読む)

III族窒化物複合基板

【課題】支持基板と酸化物膜との接合強度および酸化物膜とIII族窒化物層との接合強度が高いIII族窒化物複合基板を提供する。

【解決手段】本III族窒化物複合基板1は、支持基板10と酸化物膜20とIII族窒化物層30aとを含み、支持基板10は多結晶で形成され、III族窒化物層30aは少なくともc軸方向に配向しているIII族窒化物結晶で形成され、酸化物膜20は不純物が添加され、不純物の濃度は、酸化物膜20において支持基板10側の第1主面20sからIII族窒化物層30a側の第2主面20tにかけて膜厚方向で変化し、第1主面20sにおける不純物の濃度は第2主面20tにおける不純物の濃度よりも高い。

(もっと読む)

半導体素子の製造方法

【課題】少なくとも表面がSiC層で構成されるとともにオフ角を有する基板を用いた半導体素子の製造方法において、イオンを活性化する際に発生するステップバンチングを除去可能な製造方法を提供する。

【解決手段】半導体素子の製造方法は、イオン注入工程と、カーボン層形成工程と、イオン活性化工程と、除去工程と、を含む。イオン注入工程では、基板にイオンを注入する。カーボン層形成工程では、イオン注入工程でイオンが注入された基板の表面にカーボン層を形成する。イオン活性化工程では、カーボン層が形成された基板を加熱してイオンを活性化させる。除去工程では、イオン活性化工程が行われた基板をSi蒸気圧下で加熱することで、カーボン層と、イオン活性化工程で基板表面に発生するステップバンチングと、を除去する。

(もっと読む)

半導体ウエハの製造方法、複合基体および複合基板

【課題】半導体デバイスを効率よく製造するために、基体の種類の如何を問わずに効率よく半導体ウエハを製造することができる半導体ウエハの製造方法、ならびにかかる製造方法に好適に用いられる複合基体および複合基板を提供する。

【解決手段】本半導体ウエハの製造方法は、基体10上に、表面のRMS粗さが10nm以下の基体表面平坦化層12を形成して複合基体1を得る工程と、複合基体1の基体表面平坦化層12側に半導体結晶層20aを貼り合わせて複合基板3A,3B,3Cを得る工程と、複合基板3A,3B,3Cの半導体結晶層20a上に少なくとも1層の半導体層30を成長させる工程と、基体表面平坦化層12をウェットエッチングで除去することにより、基体10から半導体結晶層20aを分離して、半導体結晶層20aおよび半導体層30を含む半導体ウエハ5を得る工程と、を含む。

(もっと読む)

半導体装置

【課題】トランジスタ領域におけるゲート間距離などのレイアウトに依存することなく、半導体層のチャネル領域に有効に応力を作用させることができる半導体装置を実現する。

【解決手段】MOSトランジスタを備える半導体装置の構成として、素子分離層4で素子分離されたトランジスタ領域を有する半導体層3と、トランジスタ領域で半導体層3の第1の面上にゲート絶縁膜5を介して形成されたゲート電極6と、トランジスタ領域で半導体層3の第1の面と反対側の第2の面上に形成された応力膜31とを備え、応力膜31は、シリサイド膜を用いて形成されている。

【選択図】図13  (もっと読む)

(もっと読む)

窒化物半導体形成用基板及び窒化物半導体

【課題】窒化物半導体形成に好適な、シリコンウェーハをベースとした安価な形成用基板を提供することである。また、厚膜の窒化物半導体エピタキシャル層を成長させた場合でも、各材料間の格子定数差および熱膨張係数差から生じる、反り・クラックの発生を低減し、機械的強度や、熱的強度に優れた窒化物半導体形成用基板を提供すること。

【解決手段】ボロンとゲルマニウムとが特定濃度でドープされており、好ましくはボロンとゲルマニウムの濃度比において、ゲルマニウムの濃度をボロンの濃度の5〜8倍と制御したシリコンウェーハ。

(もっと読む)

有機結晶構造物、有機トランジスタ、及び有機結晶構造物の製造方法

【課題】結晶の結晶片又はその集合体における被形成体に対する付着力が高い、有機結晶構造物を提供すること。

【解決手段】基板12に直接接触して設けられた有機化合物の単結晶の結晶14と、結晶14が設けられた基板12の面18と同一面20に直接接触し、かつ、前記結晶14における周囲の少なくとも一部に直接接触して設けられた、有機化合物の非晶質の薄膜16と、を有する、有機結晶構造物10である。

(もっと読む)

炭化珪素基板の製造方法

【課題】炭化珪素基板中を貫通して流体が漏出することを防止することができる炭化珪素基板の製造方法を提供する。

【解決手段】炭化珪素から作られた第1および第2の被支持部11、12の各々と、炭化珪素から作られた支持部30とが互いに対向し、かつ第1および第2の被支持部11、12の間に隙間GPが設けられるように、第1および第2の被支持部11、12、および支持部30が配置される。支持部30の炭化珪素を昇華および再結晶させることで、第1および第2の単結晶基板11、12の各々に支持部30が接合される。この際、隙間GPにつながるように支持部30に貫通孔THが形成されることで、隙間GPおよび貫通孔THを通って流体が通過し得る経路PTが形成される。この経路PTを塞ぐことで、炭化珪素基板中を貫通して流体が漏出することを防ぐことが可能となる。

(もっと読む)

積層体の製造方法、III族窒化物単結晶自立基板の製造方法、および、積層体

【課題】III族窒化物単結晶が積層された積層体を冷却したとしても、該積層体の反り(結晶軸の歪み)が低減できる製造方法を提供する。

【解決手段】ベース基板/第1のIII族窒化物単結晶層/第1の非単結晶層からなる積層基板を形成する工程、積層基板からベース基板を除去する工程、第1のIII族窒化物単結晶層上にIII族窒化物単結晶をエピタキシャル成長させて第2のIII族窒化物単結晶層を形成する工程、第2のIII族窒化物単結晶層上に、第2の非単結晶層を形成する工程、を含む積層体の製造方法。

(もっと読む)

多層膜付き単結晶基板、多層膜付き単結晶基板の製造方法および素子製造方法

【課題】多層膜の成膜により生じた反りを矯正すること。

【解決手段】単結晶基板20と、単結晶基板20の片面に形成された2つ以上の層を有しかつ圧縮応力を有する多層膜30とを含み、単結晶基板20をその厚み方向において2等分して得られる2つの領域20U、20Dのうち、少なくとも単結晶基板20の多層膜30が形成された面側と反対側の面側の領域20D内に、熱変性層22が設けられている多層膜付き単結晶基板、その製造方法および当該製造方法を用いた素子製造方法

(もっと読む)

炭化珪素基板の製造方法

【課題】製造工程を簡略化すると共に、表層部にらせん転位が存在することを抑制することができるSiC基板の製造方法を提供する。

【解決手段】炭化珪素からなり、主表面および当該主表面の反対面である裏面を備え、らせん転位1を表層部2aに含む欠陥含有基板2を用意する工程と、欠陥含有基板2のうち主表面に外力を印加することにより表層部2aの結晶性を低下させる第1外力印加工程と、外力印加工程の後、欠陥含有基板2を熱処理することにより表層部2aの結晶性を回復させる第1熱処理工程と、を含む製造方法とする。

(もっと読む)

III族窒化物結晶基板、エピ層付III族窒化物結晶基板、ならびに半導体デバイスおよびその製造方法

【課題】発光のブルーシフトが抑制された発光デバイスの製造に好適なIII族窒化物結晶基板、エピ層付III族窒化物結晶基板、ならびに半導体デバイスおよびその製造方法を提供する。

【解決手段】本III族窒化物結晶基板1は、III族窒化物結晶基板1の任意の特定結晶格子面のX線回折条件を満たしながら結晶基板の主表面1sからのX線侵入深さを変化させるX線回折測定から得られる特定結晶格子面の面間隔において、0.3μmのX線侵入深さにおける面間隔d1と5μmのX線侵入深さにおける面間隔d2とから得られる|d1−d2|/d2の値で表される結晶基板の表面層の均一歪みが1.7×10-3以下であり、主表面の面方位が、結晶基板のc軸を含む面から[0001]方向に−10°以上10°以下の傾斜角を有する。

(もっと読む)

半導体基板、半導体デバイス、半導体基板の製造方法および半導体デバイスの製造方法

【課題】窒化物層上にエピタキシャル層を形成したときにクラックが発生することを抑制でき、かつエピタキシャル層が半導体基板から剥がれることを抑制できる半導体基板および半導体基板の製造方法を提供する。

【解決手段】半導体基板10aは、窒化物層12の主面12a上にエピタキシャル層を形成するための半導体基板であって、異種基板11と、異種基板11上に形成された窒化物層12とを備え、窒化物層12は応力緩和領域を有する。

(もっと読む)

GaN単結晶体およびその製造方法、ならびに半導体デバイスおよびその製造方法

【課題】GaN単結晶体を成長させる際および成長させたGaN単結晶体を基板状などに加工する際、ならびに基板状のGaN単結晶体上に少なくとも1層の半導体層を形成して半導体デバイスを製造する際に、クラックの発生が抑制されるGaN単結晶体およびその製造方法ならびに半導体デバイスおよびその製造方法を提供する。

【解決手段】本GaN単結晶体10は、ウルツ型結晶構造を有し、30℃において、弾性定数C11が348GPa以上365GPa以下かつ弾性定数C13が90GPa以上98GPa以下、または、弾性定数C11が352GPa以上362GPa以下である。

(もっと読む)

炭化シリコン膜の製造方法

【課題】高温で長時間の処理が必要なエピタキシャル成長を用いることなく、熱応力の発生を抑え、信頼性に優れた、所望の膜厚の炭化シリコン膜を容易に得ることができ、かつ低コストや大口径化が可能な炭化シリコン膜の製造方法を提供する。

【解決手段】本発明の炭化シリコン膜13の製造方法は、基板11上にアモルファスシリコンとポリシリコンとの少なくとも一方を含む第1シリコン膜14aを形成する工程と、第1シリコン膜14aを炭化処理し第1炭化シリコン膜13aを形成する工程と、第1炭化シリコン膜13aを形成した後に、第2シリコン膜14bを形成する工程と、第2炭化シリコン膜13bを形成する工程と、を少なくとも1回有することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】 格子定数が異なる複数種類の半導体素子を同一の基板上に混載することが可能な半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、シリコン基板21の一部に絶縁膜22を形成し、シリコン基板21と絶縁膜22上にアモルファスSiGe層23を形成し、シリコン基板を熱処理し、アモルファスSiGe層23を絶縁膜22上に横方向に固相若しくは液相成長させて結晶化し、シリコン基板22と絶縁膜22上に格子定数が後に形成される材料層の格子定数に整合されたSiGe層23bを形成する。

(もっと読む)

半導体基板の製造方法、半導体デバイスの製造方法、半導体基板および半導体デバイス

【課題】低抵抗な窒化物層を基板へ貼り合わせた半導体基板の製造方法、半導体デバイスの製造方法、半導体基板および半導体デバイスを提供する。

【解決手段】半導体基板10の製造方法は、以下の工程を備えている。主面と、主面と反対側の裏面とを有する窒化物基板を準備する。窒化物基板の裏面に、気相のイオンを注入する。窒化物基板の裏面と、異種基板11とを貼り合わせることにより、貼り合わせ基板を形成する。貼り合せ基板から窒化物基板の一部を剥離する。700℃を超える温度で熱処理する。

(もっと読む)

半導体装置とその製造方法

【課題】格子定数が異なる複数種類の半導体素子を同一の基板上に混載することが可能な半導体装置とその製造方法。

【解決手段】少なくとも第1、第2のSi1-xGex(0≦x≦1)層14a,14b,14cが絶縁膜13上に形成されている。第1、第2のSi1-xGex(0≦x≦1)層上に対応して少なくとも第1、第2の材料層15,16,17が形成されている。第1、第2のSi1-xGex(0≦x≦1)層層14a,14b,14cの格子定数はその上の第1、第2の材料層15,16,17の格子定数に整合されている。

(もっと読む)

膜移し変えプロセス

【課題】エピタキシャル成長の表面にできた欠陥を貼りあわせ基板に持ち込まない製造方法を提供する。

【解決手段】表面近傍の域に欠陥を有する第一基板4から、第二材料でできたホスト基板20上に、第一材料の層を移し変えるプロセスであって:a)第一の薄化基板24を形成するために、第一基板を薄化する段階;b)注入面6を形成するために前記第一基板にイオンまたは原子注入し、移し変えるべき層を画定する段階;c)注入面に沿って基板を破断することにより、ホスト基板20上に前記層を移し変える段階;を含むプロセスによって欠陥をなくした貼りあわせ基板を作ることができる。

(もっと読む)

高表面品質GaNウェーハおよびその製造方法

【課題】優れた表面品質をGa側にて有するAlxGayInzN半導体ウェーハおよびそのようなウェーハの製造方法を実現する。

【解決手段】ウェーハのGa側における10×10μm2面積内で1nm未満の根二乗平均表面粗さを特徴とする、AlxGayInzN(式中、0<y≦1およびx+y+z=1)を含む高品質ウェーハ。このようなウェーハは、例えばシリカまたはアルミナなどの研磨粒子と酸または塩基とを含む化学的機械研磨(CMP)スラリーを用いて、そのGa側にてCMPに付される。このような高品質AlxGayInzNウェーハの製造方法はラッピング工程、機械研磨工程、およびその表面品質を更に高めるための熱アニールまたは化学エッチングによるウェーハの内部応力を低下させる工程を含んでよい。このCMP方法はAlxGayInzNウェーハのGa側における結晶欠陥を強調するために有用に適用される。

(もっと読む)

1 - 20 / 23

[ Back to top ]