Fターム[5F152LM08]の内容

再結晶化技術 (53,633) | 一般エピタキシャル成長技術 (652) | 成長技術 (97)

Fターム[5F152LM08]に分類される特許

81 - 97 / 97

シリコンエピタキシャルウェーハの製造方法及びシリコンエピタキシャルウェーハ

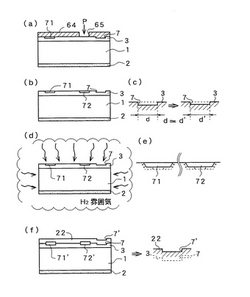

【課題】 埋込イオン注入層を介して複数のエピタキシャル層が積層形成されたエピタキシャルウェーハを極めて能率的に製造でき、形成されるイオン注入層の横方向拡散も少ないシリコンエピタキシャルウェーハの製造方法を提供する。

【解決手段】 イオン注入後の結晶回復のための熱処理を水素雰囲気中にて行うことで、注入前酸化処理を行わなくともイオン注入層71,72への面荒れ発生が極めて効果的に抑制される。その結果、埋込イオン注入層71’,72’を有するエピタキシャルウェーハの製造方法において、注入前酸化処理の省略、ひいてはフォトレジスト膜のみをマスク64として用いたイオン注入が実現される。注入前酸化を含めたエピタキシャル層3への積極的な酸化膜形成処理が排除される結果、埋込イオン注入層71’,72’に加わる熱履歴の回数が減って横方向拡散が効果的に抑制される。また、酸化膜の形成/除去が不要となる結果、エピタキシャルウェーハ製造の工程数を劇的に減ずることができる。

(もっと読む)

単結晶SiC基板の製造方法

【課題】エピタキシャル成長させるSiC層の結晶性を良好にして表面平坦性を向上させることができる単結晶SiC基板の製造方法を提供する。

【解決手段】所定厚さの表面Si層と埋め込み絶縁層とを有するSOI基板を準備し、上記SOI基板を炭化水素系ガス雰囲気中で加熱して上記表面Si層を単結晶SiC膜に変成させ、上記単結晶SiC膜をシード層としてエピタキシャル成長させることにより単結晶SiC層を形成する方法であって、上記エピタキシャル成長を、相対的に低温の成長温度に設定した第1段階と、相対的に高温の成長温度に設定した第2段階を含む少なくとも2段階の処理で段階的にエピタキシャル成長させることにより、エピタキシャル成長過程での昇華による部分的なシード層の消滅が防止され、結晶性と表面の平坦性の良好な単結晶SiC層を形成することができる。

(もっと読む)

半導体ウェハ

【課題】GaAs基板からの能動層への転位の伝播を抑止する半導体結晶基板の構造を提供すること。

【解決手段】GaAs基板1と能動層40との間に、平面内にInAs核をドット状(島状)に形成し、その上にInAs核が埋まる程度にIII−V族化合物半導体のバッファ層20を成長した構造を設ける。

(もっと読む)

成長制御方法およびデバイス

【課題】複雑で高コストとなる処理工程を経ることなく、微小な構造の位置制御性およびサイズ均一性を高める。

【解決手段】第1の物質からなる基板の上に第2の物質を堆積させ、ステップが規則的に配列する二次元表面相11を形成する(S2)。ついで、二次元表面相11の上に第3の物質を配置することにより、二次元表面相11上のステップに第3の物質を含む液滴を配列させる(S3)。ついで、液滴島21を結晶化させることにより、微小構造22を形成する(S4)。

(もっと読む)

歪みシリコンウェーハの製造方法

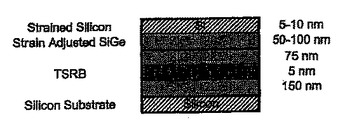

【課題】SiGe層を有する歪みシリコンウェーハにおいて、SiGe層上に形成される歪みSi層における貫通転位密度の一層の低減化を図ることができる歪みシリコンウェーハの製造方法を提供する。

【解決手段】単結晶シリコン基板上にGe濃度を上げながら組成傾斜SiGe層(Si1−xGex層のGe濃度比xが0<x≦0.5)を厚さ0.1〜3μmにエピタキシャル形成し、その上に厚さ0.1〜1μmのGe組成比が一定である歪み緩和Si1−xGex層を形成し、更に、厚さ5〜30nmの第1歪みSi層を形成し、その上に第2歪みSi層として、第1歪みSi層の成膜温度より低い温度で厚さ10nm以下の歪みSi層をエピタキシャル成長させる。

(もっと読む)

シリコン化合物によるシリコン含有層の堆積

本発明の実施形態は、一般的には、シリコン化合物の合成物及びシリコン含有膜を堆積させるためにシリコン化合物を用いる方法を提供する。本方法は、シリコン化合物を基板表面に導入するステップとシリコン化合物の一部、シリコンモチーフをシリコン含有膜として堆積させるステップとを用いる。リガンドはシリコン化合物の他の部分であり、インサイチュエッチング剤として遊離する。インサイチュエッチング剤は、選択的シリコンエピタキシーの成長を支持する。シリコン化合物は、SiRX6、Si2RX6、Si2RX8(ここで、Xは独立して水素又はハロゲンであり、Rはカーボン、シリコン又はゲルマニウムである。)を含んでいる。シリコン化合物は、また、3つのシリコン原子と、4つのカーボン、シリコン又はゲルマニウム原子と、水素又はハロゲンと少なくとも1つのハロゲン原子とを含む化合物、また、4つのシリコン原子と、5つのカーボンと、シリコン又はゲルマニウム原子と、水素又はハロゲンと少なくとも1つのハロゲン原子とを含む化合物を含んでいる。 (もっと読む)

ヘテロ集積型歪みシリコンn型MOSFET及びp型MOSFET及びその製造方法

【課題】 n型及びp型MOSFETデバイスに使用するための半導体構造体と、その製造方法とを提供する。

【解決手段】 半導体構造体は、n型MOSFETが製造されるウェハ領域の層構造が、p型MOSFETが製造されるウェハ領域の層構造とは異なるものとなるように製造される。この構造体は、まず、Heなどの軽原子のイオン注入によりSi含有基板の表面に損傷領域を形成することによって、製造される。次いで、損傷領域を含むSi含有基板の上に、歪みSiGe合金が形成される。次いで、アニール・ステップを使用し、欠陥に起因する歪み緩和によって歪みSiGe合金を実質的に緩和させる。次に、緩和したSiGe合金の上に、歪みSiなどの歪み半導体キャップが形成される。

(もっと読む)

半導体素子のための支持構造体を作製する方法

半導体素子を作製する方法を記述する。この方法において、所望の欠陥密度レベル(好ましくないドーピングレベルに終わる)を有し、充分な厚さを有する出発基板を選択する。その後、出発基板上に、所望のドーピングレベルを有する半導体層を形成する。生じた半導体層は、最終製品用途に関する所望の欠陥密度及びドーピングレベルを有する。動的素子と、導電体と、他の所要の構造体とを半導体層上に形成した後、出発基板を取り除き、所望厚の半導体層を残す。VECSEL用途において、動的素子はゲインキャビティーであることができ、この半導体層は、ウォールプラグ効率(WPE)を最大化するのに、必要な欠陥密度及びドーピングレベルを有する。態様のひとつでは、半導体層のドーピングは均一でない。例えば、層の大部分を低レベルでドープし、そして残りの部分をさらに高いレベルでドープする。より多くドープ化した材料の場合、これによって、特定の厚さにおいて、改良されたWPEがもたらされる。  (もっと読む)

(もっと読む)

多層構造の製造方法

本発明は、半導体材料製の多層構造用の製造方法に関し、この構造は、第1半導体材料製の基板(20)と、第2半導体材料製の表面薄層を備え、これらの2つの半導体材料は実質的に異なる格子定数を有する。この方法は、支持基板(100)上に表面薄層を備える層(110)を製造するステップと、支持基板及び堆積層によって形成される集合体(10)中に脆化ゾーンを形成するステップと、集合体(10)に対象基板(20)をボンディングするステップと、この脆化ゾーンのレベルで分離するステップと、得られる構造の表面を処理するステップとを含むことを特徴とする。  (もっと読む)

(もっと読む)

ウェーハの製造方法

【課題】異なる格子の基板上に成長した良質なエピタキシャル層を備えたウェーハを得る方法の提供。

【解決手段】オンアクシスシリコン基板を研磨ステップ104で研磨して、ウェーハの表面粗さを増大させる。例えばSiGe層である傾斜バッファ層及び緩和層をウェーハ上に形成した後、CMP最終研磨108を実施する。

(もっと読む)

エピタキシャル層を形成する方法および装置

本発明は、シリコン基材上にIV族元素をベースとするエピタキシャル層を化学蒸着により堆積させる方法であって、キャリヤーガスとして窒素または希ガスの一種を使用する、方法を提供する。本発明はさらに、ガス入口(14)およびガス出口(16)を有するチャンバー(12)と、チャンバー(12)の中にシリコン基材を取り付ける手段(18)とを備えてなる化学蒸着装置(10)を提供するが、該装置は、入口に接続され、なおかつキャリヤーガスとして窒素または希ガスを供給するように配置されたガス供給源を包含する。  (もっと読む)

(もっと読む)

半導体基板および該半導体基板の製造方法

【課題】支持体ウェハ2とこの支持体ウェハ2の1つの面に設けられた単結晶半導体材料から成る層8を有する半導体基板の製造にあたり、きわめて薄い半導体層をもち同時にHF欠陥密度も著しく僅かな層構造を提供する。

【解決手段】凹部3を含む層を、単結晶半導体材料から成るドナーウェハ1の表面に形成し、この凹部3を含むドナーウェハ1の層を支持体ウェハ2と接合し、支持体ウェハ2とドナーウェハ1との界面4のところで凹部3を封止するために熱処理を加えて、ドナーウェハ1内に中空室6の設けられた層を形成し、この中空室6の設けられた層に沿ってドナーウェハ1を分割して、支持体2上に半導体材料から成る層8を残す。

(もっと読む)

高速CMOS共存Ge−オン−インシュレータ光検出器の構造および製作方法

【課題】SiCMOS技術と共存可能な高速高効率光検出器を作る問題に対処すること。

【解決手段】本構造は、薄いSOI基板の上のGe吸収層から成り、分離領域、交互になるn型およびp型コンタクト、および低抵抗表面電極を利用する。本デバイスは、下の基板で生成されたキャリアを分離するために埋込み絶縁物を利用して高帯域幅を、Ge吸収層を利用して広いスペクトルにわたった高量子効率を、薄い吸収層および狭い電極間隔を利用して低電圧動作を、さらに平面構造およびIV族吸収材料の使用によってCMOSデバイスとの共存性を、達成する。本光検出器を製作する方法は、薄いSOIまたはエピタキシャル酸化物へのGeの直接成長および高品質吸収層を達成するための後の熱アニールを使用する。この方法は、相互拡散に利用可能なSiの量を制限し、それによって、下のSiによるGe層の実質的な希釈を起こすことなく、Ge層をアニールすることができるようになる。

(もっと読む)

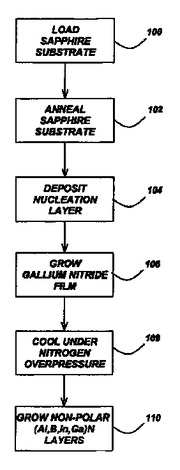

非極性(Al、B、In、Ga)N量子井戸

非極性a面GaN/(A1、B、In、Ga)N多重量子井戸(MQW)を製造する方法。a面MQWは、有機金属化学気相成長法(MOCVD)によって適切なGaN/サファイアテンプレート層上に成長し、井戸幅は20Å〜70Åの範囲である。a面MQWからの室温光ルミネセンス(PL)放射エネルギーは、自己無頓着ポアソン−シュレディンガー(SCPS)計算を使用してモデリングされた正方井戸傾向を伴った。最適PL放射強度は、a面MQWについて52Åの量子井戸幅で得られる。  (もっと読む)

(もっと読む)

半導体基板を作製する方法

【課題】絶縁体上歪み半導体(SSOI)基板を作製する方法が提供される。

【解決手段】この方法で、歪み半導体は、あらかじめ形成された絶縁体上半導体基板の絶縁体層の上に直接配置された50nm未満の厚さを有する薄い半導体層である。本発明のSSOI基板を形成する際に、ウエハボンディングは使用されない。

(もっと読む)

一次元半導体基板、並びに、該一次元半導体基板を用いた素子、素子アレー、及びモジュール

半導体回路基板としての一次元半導体基板とその製造方法、および該一次元半導体基板を用いた素子、素子アレー、モジュール、ディスプレイ、太陽電池及び太陽電池モジュールとその製造方法を提供する。

【解決手段】 本発明の一次元半導体基板1あるいは2は、幅又は厚さ、あるいは径に対して10倍以上の長さを持つ線状の基材3に所望の薄膜4を1層以上形成している。薄膜4に半導体を適用ことで一次元半導体薄膜が形成される。本発明の一次元半導体基板1あるいは2は、光ファイバの製造技術である線引技術を応用して製造される。

(もっと読む)

半導体装置、および薄層歪緩和バッファ成長方法

本発明は、半導体基板を含み、その上部に少なくとも薄層歪緩和バッファを有し、本質的に3層のスタックから成っている半導体装置に関するものであり、その薄層歪緩和バッファは半導体装置のアクティブ部分でなく、さらに、薄層歪緩和バッファを形成する前記3層が本質的に一定のGe濃度を有することを特徴としている。前記3層は以下の通りである:Si1−xGexの第1エピタキシャル層、xはGe濃度である;前記第1エピタキシャル層上の、Si1−xGex:Cの第2エピタキシャル層、Cの量は少なくとも0.3%である;前記第2層上のSi1−xGexの第3エピタキシャル層。

(もっと読む)

(もっと読む)

81 - 97 / 97

[ Back to top ]