Fターム[5F152LM08]の内容

再結晶化技術 (53,633) | 一般エピタキシャル成長技術 (652) | 成長技術 (97)

Fターム[5F152LM08]に分類される特許

61 - 80 / 97

半導体光電陰極

【課題】p型不純物の異常拡散の発生を防止すること。

【解決手段】半導体光電陰極は、p型の不純物がドープされ、且つ互いにヘテロ接合する第1および第2のIII−V族化合物半導体層を備える。第2のIII−V族化合物半導体層が光吸収層として機能し、第2のIII−V族化合物半導体層のエネルギーギャップは、第1のIII−V族化合物半導体層のそれより小さく、各半導体層におけるp型のドーパントとしては、Be又はCが用いられる。このとき、第2のIII−V族化合物半導体層は、第1のIII−V族化合物半導体層上に積層されていても良い。また、第1のIII−V族化合物半導体層と第2のIII−V族化合物半導体層は(In,Ga,Al)と(As,P,N)のうち少なくともそれぞれ一つ以上含んでいても良い。

(もっと読む)

AlN系III族窒化物単結晶厚膜の作製方法

【課題】結晶品質に優れ、かつクラックのないAlN系III族窒化物単結晶厚膜を作製する方法を提供する。

【解決手段】エピタキシャル基板上に、HVPE法によってAlN系III族窒化物厚膜を得る場合に、通常の成長条件で厚膜層の形成を行う第1の工程と、その時点で形成されている厚膜層を第1の工程における厚膜層の形成温度T1以上の高温状態T2で保持することを主目的とする第2の工程とを適宜のタイミングで切り替えつつ繰り返し行うようにする。これにより、それぞれの第1の工程において厚膜層に内在する歪を第2の工程で逐次に緩和させつつ厚膜層を形成することができる。厚膜層の形成後に面内方向に作用する引張応力を、あらかじめ緩和させた状態の厚膜層を形成することができるので、厚膜層におけるクラックの発生を抑制することができる。

(もっと読む)

半導体基板の製造方法及び半導体基板

【課題】III族窒化物半導体の結晶層の結晶性を向上できる半導体基板の製造方法及び半導体基板を提供する。

【解決手段】本発明の第1側面に係る半導体基板の製造方法は、下地基板の上にクロム層を7nm以上45nm未満の平均層厚で成膜するクロム層成膜工程と、前記クロム層を1000℃以上の温度で窒化してクロム窒化物膜にする窒化工程とを備えたことを特徴とする。

(もっと読む)

半導体基板の製造方法

【課題】III族窒化物半導体の結晶層の結晶性を向上できる半導体基板の製造方法を提供する。

【解決手段】本発明の第1側面に係る半導体基板の製造方法は、下地基板の上にクロム層を50℃以上の温度で成膜するクロム層成膜工程と、前記クロム層を窒化してクロム窒化物膜にする窒化工程とを備えたことを特徴とする。

(もっと読む)

半導体基板の製造方法

【課題】半導体基板の製造コストを低減できる半導体基板の製造方法を提供する。

【解決手段】本発明の第1側面に係る半導体基板の製造方法は、Crで形成された下地基板を準備する準備工程と、前記下地基板の(110)面を窒化してクロム窒化物層の(111)面を形成させる窒化工程とを備えたことを特徴とする。

(もっと読む)

AlN結晶基板の製造方法、AlN結晶の成長方法およびAlN結晶基板

【課題】大型で高品質なAlN結晶基板を製造することができるAlN結晶基板の製造方法、大型で高品質なAlN結晶を成長させることができるAlN結晶の成長方法およびその成長方法により成長したAlN結晶からなるAlN結晶基板を提供する。

【解決手段】異種基板1上に異種基板1の口径rに対して0.4r以上の厚さにAlN結晶2を昇華法により成長させる工程と、異種基板1から200μm以上離れたAlN結晶2の領域からAlN結晶基板3を形成する工程と、を含む、AlN結晶基板3の製造方法である。また、その製造方法により製造されたAlN結晶基板3上にAlN結晶2を昇華法により成長させるAlN結晶2の成長方法とその成長方法より成長したAlN結晶2からなるAlN結晶基板3である。

(もっと読む)

III−N層の選択的マスキング方法、自立III−N層もしくはデバイスの製造方法、および当該方法により得られる製品

【課題】自立III-N層及びIII-N材料系の選択的に形成された後続層を備えるデバイスを効率的に提供または準備する。

【解決手段】 III-N層上にマスクを形成する方法において、複数のファセットからなる表面を持つIII-N層が提供される。マスク材料は一または複数のファセット上に選択的に成長させるが、全てのファセット上に成長させるものではない。詳細には、マスク材料の成長は、III-N層のエピタキシャル成長期間、(i)第一のファセット型または第一のファセット群上の少なくとも一の別のIII-N層の選択的成長と、(ii)第二のファセット型または第二のファセット群上のマスク材料の選択的成長とが同時に進行するような条件の下で行われる。

【効果】厚い自立III-N層の製造が可能となる。さらに、独自の構造および層を有する半導体デバイスおよび部品が製造可能となる。

(もっと読む)

単結晶基板及びその製造方法

【課題】良質の単結晶基板及びその製造方法を提供する。

【解決手段】基板上に形成され、前記基板の一部が露出されるウィンドウを有する絶縁層と、前記ウィンドウに露出された前記基板の部分に形成される選択的結晶成長層と、前記絶縁層上で前記結晶成長層上に形成され、前記結晶成長層を結晶化シード層として用いて結晶化された単結晶層とを備える単結晶ウェーハである。これにより、ストッパによって結晶層の研磨深さを制御でき、従って良質の単結晶基板を製造できる。

(もっと読む)

半導体基材及びその製造方法

【課題】IV族半導体多結晶の低温成長において、結晶性に優れ、かつ結晶粒径や配向性を制御した高品質のIV族半導体多結晶の成長を可能にする半導体基材の製造方法及び得られた半導体基材を提供する。

【解決手段】550℃以下の温度でハロゲン化ゲルマニウムとシラン類を原料とする熱CVD法を用いて、非晶質、多結晶あるいは金属などの基材上にSiGeあるいはGeの結晶核を形成し、該結晶核上に気相堆積法でSi多結晶膜を形成する半導体基材の製造方法により、上記課題を解決する。また、本発明の半導体基材は、非晶質、多結晶あるいは金属などの基材と、該基材上にハロゲン化ゲルマニウムとシラン類を原料とする熱CVD法で形成されたSiGeあるいはGeの結晶核と、該結晶核上に気相堆積法で形成されたSi多結晶膜とを有する。

(もっと読む)

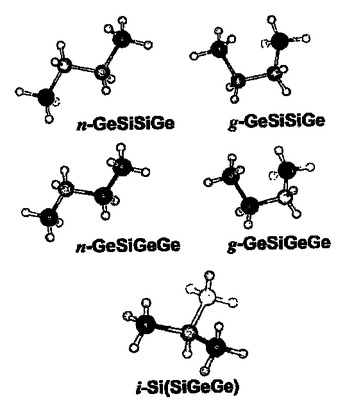

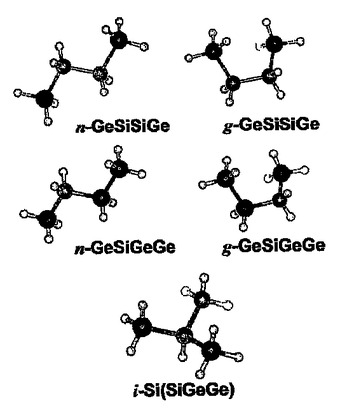

新規な水素化シリコンゲルマニウム、その製造法および使用法

本発明は、水素化シリコンゲルマニウム化合物、それらの合成法、それらの成膜法、およびそれらの化合物を用いて作製された半導体構造を提供する。これらの化合物は、式:SiHn1(GeHn2)yによって定義される。式中、yは2,3または4であり;n1は、0,1,2または3であって原子価を満たし;n2は、化合物中の各Ge原子に関して独立に0,1,2または3であって原子価を満たす。  (もっと読む)

(もっと読む)

新規な水素化シリコンゲルマニウム、その製造法および使用法

本発明は、新規水素化シリコンゲルマニウム化合物、それらの合成法、それらの成膜法、およびそれらの新規化合物を用いて作製された半導体構造を提供する。これらの化合物は、式:(SiHn1)x(GeHn2)yによって定義される。式中、xは2,3または4であり;yは1,2または3であり;x+yは3,4または5であり;n1は、化合物中の各Si原子に関して独立に0,1,2または3であって原子価を満たし;n2は、化合物中の各Ge原子に関して独立に0,1,2または3であって原子価を満たし;但し、yが1のとき、n2は0ではなく;さらに、xが3、かつ、yが1のとき、n2は2または3であり;さらに、xが2、かつ、yが1のとき、n2は3である。  (もっと読む)

(もっと読む)

単結晶SiC基板の製造方法

【課題】エピタキシャル成長させるSiC層の結晶性を良好にして表面平坦性を向上させることができる単結晶SiC基板の製造方法を提供する。

【解決手段】所定厚さの表面Si層3と埋め込み絶縁層4とを有するSOI基板1を準備し、上記SOI基板1を炭化水素系ガス雰囲気中で加熱して上記表面Si層3を単結晶SiC膜に変成させ、上記単結晶SiC膜をシード層5としてエピタキシャル成長させることにより単結晶SiC層6を形成する方法であって、上記エピタキシャル成長の際、少なくともエピタキシャル成長温度に達するまでの1100℃以上の温度域において、毎秒25℃以上の昇温速度で急速加熱を行ってエピタキシャル成長させることにより、エピタキシャル成長過程での昇華による部分的なシード層5の消滅が防止され、結晶性と表面の平坦性の良好な単結晶SiC層6を形成することができる。

(もっと読む)

窒化物半導体ウェーハ及び窒化物半導体素子

【課題】多結晶AlN基板を用いつつ結晶性にすぐれた窒化物半導体ウェーハ及び窒化物半導体素子を提供する。

【解決手段】配向性を有する多結晶窒化アルミニウムからなり、主面上に複数のステップ10Sが形成された基板10と、前記基板の前記主面上に設けられた単結晶の窒化物半導体層25とを備えた窒化物半導体ウェーハ1及び前記窒化物半導体層25の上に設けられた電極を備えた窒化物半導体素子。

(もっと読む)

半導体形成用基板、窒化物系半導体基板およびその製造方法

【課題】従来のオリエンテーションフラットやインデックスフラットよりも容易に作製することができ且つ視認ができる表裏の判別手段を備えた半導体形成用基板、窒化物系半導体基板およびその製造方法を提供すること。

【解決手段】基板の周辺部に、前記基板の表面から裏面へ貫通する貫通孔5を設け、その貫通孔の数の相違をもって又は中心からの距離の相違をもって、表裏の判別を可能とする。上記貫通孔の形成は、窒化物半導体の気相成長において、元となる種結晶表面の任意の位置に、GaN以外の材料(例えばカーボン片)を付け、または凹凸をつけることで、その上部に正常に成長しない領域を形成した状態でエピタキシャル層を成長させることにより、成長と同時に貫通孔が形成される。

(もっと読む)

部分SOI基板、部分SOI基板の製造方法、及び、SOI基板

【課題】 絶縁膜に囲まれた領域でも不純物をゲッタリングし、SOI領域の結晶欠陥を少なくし、また、パワーデバイスの搭載を容易にする。

【解決手段】 部分的に形成されたSOI領域を有する部分SOI基板において、基板1と基板1の上に部分的に形成された絶縁膜2との上に形成されたエピタキシャル層3と、絶縁膜2の上にエピタキシャル層3の一部を含んで形成され、エピタキシャル層3と同導電型でエピタキシャル層3よりも不純物濃度が高い低抵抗領域4と、低抵抗領域4内部に形成されたゲッタリング領域5と、を有するSOI領域を形成する。また、エピタキシャル層3を貫通して絶縁膜2に達する素子分離層6によってSOI領域と分離されたバルク領域を形成する。

(もっと読む)

半導体基材及びその製造方法

【課題】IV族半導体多結晶の低温成長において、結晶性に優れ、かつ結晶粒径や配向性を制御した高品質のIV族半導体多結晶の成長を可能にする半導体基材の製造方法及び得られた半導体基材を提供する。

【解決手段】IV族半導体の基材上への多結晶の低温成長において、ハロゲン化ゲルマニウムとシラン類との熱CVD法を用いて、550℃以下の温度と15torr以上の圧力で予め基材上にIV族元素より成る結晶核を生成した後、これを核として利用し、従来のIV族半導体の低温結晶成長技術により結晶成長を行うことにより、上記課題を解決する。

(もっと読む)

半導体装置およびその製造方法

【課題】特性を十分に向上することができる半導体装置およびその製造方法を提供する。

【解決手段】MOSFET30は、SiC膜11を備えている。SiC膜11はその表面にファセット形成層11aを有しており、ファセット形成層11aのファセットの一周期の長さP1は100nm以上であり、ファセット形成層11aをチャネル16としている。また、MOSFET30の製造方法は、SiC膜11を形成する工程と、SiC膜11の表面にSiを供給した状態で、SiC膜11を熱処理する熱処理工程と、熱処理工程によってSiC膜11の表面に得られたファセットをチャネル16とする工程とを備えている。

(もっと読む)

SOI基板及び該基板の製造方法

【課題】SOI層の厚さのバラツキの無いSOI基板及び該SOI基板の製造方法を提供する。

【解決手段】シリコン基板上にエピタキシャル剥離層を介してALE成長でSOI層を形成し、ボデイウエーハを貼り付けた後、前記エピタキシャル剥離層を溶解除去することによって、全てがALE成長で作成したSOI層を形成し、

SOI層の厚さのバラツキの無いSOI基板とした。

(もっと読む)

シリコンウエハ上に炭化ケイ素の層を形成する方法

本発明はシリコンウエハ(1)上に炭化ケイ素(3,4)の層を形成する方法に関する。本発明は、本質的なチェック模様を用いてウエハ上に浸炭防止マスク(2)を積層し、残存ストレスがそれぞれ膨張と圧縮の形態をとるような条件で浸炭工程を実行し、前記マスクを取り除き、残存ストレスがそれぞれ圧縮と膨張の形態をとるような条件で浸炭工程を実行する工程を含むことを特徴とする。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】安定した性能を示す半導体装置を提供すること。

【解決手段】酸化膜およびゲート配線により区画された半導体基板上の所定の位置に設け

られたソースおよび/またはドレインせり上げ構造を備えた半導体装置であって、

前記ソースおよび/またはドレインせり上げ構造の上端部の形状の、前記半導体基板法

線方向に沿った前記半導体基板上に対する正射投影像が、対応する前記酸化膜および前記

ゲート配線により区画された前記半導体基板上の所定の形状と略一致し、かつ、前記ソー

スおよび/またはドレインせり上げ構造のうち、前記半導体基板と平行な平面で切断して

得られる断面の、前記半導体基板法線方向に沿った前記半導体基板上に対する正射投影像

の少なくとも一つが、対応する前記酸化膜および前記ゲート配線により区画された前記半

導体基板上の所定形状よりも大きいことを特徴とする半導体装置。

(もっと読む)

61 - 80 / 97

[ Back to top ]