Fターム[5F152LM08]の内容

再結晶化技術 (53,633) | 一般エピタキシャル成長技術 (652) | 成長技術 (97)

Fターム[5F152LM08]に分類される特許

21 - 40 / 97

炭化シリコン膜の製造方法

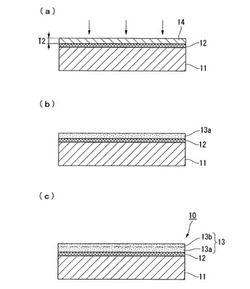

【課題】緻密で均一な膜厚であり、しかも所望の膜厚の炭化シリコン膜を得ることができ、かつ低コストや大口径化が可能な炭化シリコン膜の製造方法を提供する。

【解決手段】本発明の炭化シリコン膜13の製造方法は、基板11上にアモルファスシリコンとポリシリコンとの少なくとも一方を含むシリコン膜14を形成する工程と、シリコン膜14を炭化処理し、炭化された膜を含んだ炭化シリコン膜13を形成する工程と、を有することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】 格子定数が異なる複数種類の半導体素子を同一の基板上に混載することが可能な半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、シリコン基板21の一部に絶縁膜22を形成し、シリコン基板21と絶縁膜22上にアモルファスSiGe層23を形成し、シリコン基板を熱処理し、アモルファスSiGe層23を絶縁膜22上に横方向に固相若しくは液相成長させて結晶化し、シリコン基板22と絶縁膜22上に格子定数が後に形成される材料層の格子定数に整合されたSiGe層23bを形成する。

(もっと読む)

窒化物単結晶の製造方法、テンプレート基板、および窒化物単結晶基板

【課題】窒化物単結晶膜におけるクラックの発生を抑制する窒化物単結晶膜の製造方法、クラックの発生が抑制された窒化物単結晶基板、およびクラックの発生が抑制された窒化物単結晶膜を備えるテンプレート基板を提供する。

【解決手段】窒化物単結晶膜の製造方法は、(11−20)面からのオフ角が5°以下である下地基板1を準備する工程と、上記下地基板1の主表面上に窒化物単結晶膜3を形成する工程とを備える。前記下地基板1はSiCまたはサファイアからなることが好ましく、また、前記窒化物単結晶膜3を形成する工程における成膜温度範囲は1700℃以上2400℃以下であることが好ましい。これにより、前記テンプレート基板4の窒化物単結晶膜3はクラックの密度が低く、また、前記テンプレート基板4から下地基板1を取り除いた窒化物単結晶基板についても同様に、クラックの密度が低くなる。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】電子デバイスのスイッチング速度等の性能を向上させる。半導体基板の結晶性を向上させる。

【解決手段】ベース基板と、絶縁層と、Si結晶層とをこの順に有する半導体基板であって、Si結晶層上に化合物半導体の結晶成長を阻害する阻害層が設けられ、阻害層はSi結晶層にまで貫通する開口を有し、開口の内部にシード結晶を備え、化合物半導体はシード結晶に格子整合または擬格子整合している半導体基板を提供する。サブストレートと、サブストレート上に設けられた絶縁層と、絶縁層上に設けられたSi結晶層と、Si結晶層上に設けられ化合物半導体の結晶成長を阻害する阻害層であって、Si結晶層にまで貫通する開口を有する阻害層と、開口の内部に設けられたシード結晶と、シード結晶に格子整合または擬格子整合する化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

非極性または半極性(Ga、Al、In、B)N基板上に成長させられる素子

非極性または半極性の(Ga、Al、In、B)N基板上の(Ga、Al、In、B)N薄膜の成長形態を改良する方法であって、(Ga、Al、In、B)N薄膜は、非極性または半極性の(Ga、Al、In、B)N基板あるいはテンプレート上に直接成長させられ、成長の際に使用されるキャリアガスの一部は、不活性ガスから構成される。非極性または半極性の窒化物LEDおよびダイオードレーザは、本発明によって成長させられる平滑(Ga、Al、In、B)N薄膜上に成長させられてもよい。  (もっと読む)

(もっと読む)

シリコンエピタキシャルウェーハおよびシリコンエピタキシャルウェーハの製造方法

【課題】シリコン薄膜にミスフィット転位が発生しにくい超低抵抗率のシリコンエピタキシャルウェーハとこれを低コストで製造する方法を提供する。

【解決手段】少なくとも、シリコン単結晶基板と、該シリコン単結晶基板の主表面上に気相成長によって形成されたシリコン薄膜からなるシリコンエピタキシャルウェーハであって、前記シリコン単結晶基板は、抵抗率が2mΩ・cm以下で、かつ燐及びゲルマニウムが、前記燐の濃度〔P〕と前記ゲルマニウムの濃度〔Ge〕の比〔Ge〕/〔P〕が、0.55≦〔Ge〕/〔P〕<1.5となるようにドープされたものであることを特徴とするシリコンエピタキシャルウェーハ。

(もっと読む)

結晶性半導体膜の作製方法及び薄膜トランジスタの作製方法

【課題】結晶粒径が大きく、均一な結晶性半導体膜を作製する方法を提供する。

【解決手段】絶縁膜上に接して結晶性半導体膜を形成する第1の工程と、前記第1の工程よりも核生成頻度が低い条件により結晶性半導体膜を成長させる第2の工程と、により結晶性半導体膜を作製する。第2の工程は、第1の工程よりも半導体材料ガスの流量比が小さい条件で行う。これにより、結晶粒径が大きく、均一性の高い結晶性半導体膜を得ることができ、結晶性半導体膜の下地膜に対するプラズマダメージを従来よりも低減することができる。

(もっと読む)

シリコン膜の形成方法、pn接合の形成方法、及びこれを用いて形成されたpn接合

【課題】マイクロヒーターを利用して、多結晶シリコンからなるシリコン膜を形成する方法、pn接合を形成する方法、及びこれを用いて形成されたpn接合を提供する。

【解決手段】シリコン膜は、基板10及び基板と離間した金属パターン30を含むマイクロヒーターを利用して形成されうる。マイクロヒーターの金属パターンに電圧を印加して金属パターンを加熱し、シリコンを含むソース気体にマイクロヒーターを露出させて金属パターン上にシリコン膜100を形成することができる。シリコン膜は、多結晶シリコンからなりうる。pn接合は、基板10、基板上の導電層20、及び基板と離間した金属パターン30を含むマイクロヒーターを利用して形成されうる。マイクロヒーターの金属パターンに電圧を印加して金属パターンを加熱することで、金属パターンと導電層との間にpn接合を形成することができる。pn接合は、多結晶シリコンを含みうる。

(もっと読む)

エピタキシャル成長用内部改質基板及びそれを用いて作製される結晶成膜体、デバイス、バルク基板及びそれらの製造方法

【課題】窒化物半導体層のエピタキシャル成長に用いるサファイア基板において、効率良く基板の反り形状及び/又は反り量を精密に制御することができ、且つ、成膜中に生じる基板の反りを抑制、それを用いて作製される窒化物半導体層成膜体、窒化物半導体デバイス、窒化物半導体バルク基板及びそれらの製造方法を提供する。

【解決手段】サファイア基板の内部に、前記サファイア基板の研磨面側を通してパルスレーザを集光し、走査し、前記パルスレーザによる多光子吸収を利用して改質領域パターンを形成し、サファイア基板の反り形状及び/又は反り量を制御する。本発明により得られたサファイア基板を用いて窒化物半導体層を形成すると、成膜中の基板の反りを抑制し、基板の反り挙動を小さくすることができるため、膜の品質及び均一性が向上し、窒化物半導体デバイスの品質及び歩留まりを向上させることができる。

(もっと読む)

ホウ素ドープ半導体ナノワイヤ及びその製造方法

【課題】成長軸方向に径の均一なホウ素ドープ半導体ナノワイヤ及びその製造方法を提供する。

【解決手段】成長軸方向に径の均一なホウ素ドープ半導体ナノワイヤは、次の工程を含む製造方法により製造できる。

工程(1):半導体原料ガスを用いて、基板上にIV族半導体ナノワイヤを成長させる;

工程(2):ジボランガスのみを導入することにより、前記半導体ナノワイヤの表面にホウ素膜を堆積させる;

工程(3):表面にホウ素膜を堆積させた前記ホウ素膜付き半導体ナノワイヤを、半導体ナノワイヤ(本体)の融点以下の温度で熱アニールする。

(もっと読む)

基板上に微細構造を作製する方法

【課題】 本発明は微細構造の作製方法に関する。

【解決手段】 先駆体流体が存在する中で基板全体にわたって集束粒子ビームを走査することによって、パターニングされたシード層が形成される。ここで前記シード層を原子層堆積法又は化学気相成長法によって成長させることによって、高品質の層を成長させることができる。当該方法の利点は、非常に薄い層しか堆積しなくて良いため、前記シード層を形成するのに要する時間が相対的に短くなることである。

(もっと読む)

薄膜トランジスタの作製方法

【課題】電気特性が良好な薄膜トランジスタを、生産性高く作製する方法を提供する。

【解決手段】基板上にゲート電極を形成し、ゲート電極上にゲート絶縁層を形成し、ゲート絶縁層上に、シリコンまたはゲルマニウムを含む堆積性気体と、水素と、ヘリウム、アルゴン、ネオン、クリプトン、キセノン等の希ガスとを用い、プラズマを発生させて、厚さ3〜10nm、好ましくは3〜5nmの第1の半導体層を形成する。次に、シリコンまたはゲルマニウムを含む堆積性気体と、水素と、窒素を含む気体とを用い、プラズマを発生させて、非晶質半導体と、第1の半導体層を種結晶として部分的に結晶成長させて、形成される微結晶半導体で形成される複数の錐形状の凸部を有する第2の半導体層を形成する。次に、一導電型を付与する不純物元素が添加された半導体層を形成し、導電層を形成して、薄膜トランジスタを作製する。

(もっと読む)

窒化ガリウム系化合物半導体層の形成方法、移設方法、及び窒化ガリウム系化合物半導体層が接合されたシリコン基板

【課題】比較的結晶欠陥の少ない窒化ガリウム系化合物半導体層を比較的低コストで得ることができる技術を提供する。

【解決手段】サファイア基板10上に、SiO2層13を形成し、層13を部分的に除去してサファイア基板の露出部を形成し、露出部を持つサファイア基板上に、非晶質窒化ガリウム系化合物半導体を堆積し、層13上の非晶質窒化ガリウム系化合物半導体を蒸発させ、サファイア基板の露出部上に非晶質窒化ガリウム系化合物半導体の核を形成し、核のサイズ増大、合体、結晶成長、層13上への横方向結晶成長、平坦表面形成などを経て、サファイア基板上に窒化ガリウム系化合物半導体層20を形成し、サファイア基板10の露出部上の窒化ガリウム系化合物半導体層を除去して分離溝25を形成する。サファイア基板上の窒化ガリウム系化合物半導体層20は他の基板に移設される。

(もっと読む)

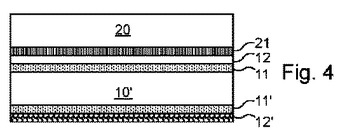

マイクロエレクトロニクス分野において単結晶膜を形成する方法

所定の材料の薄膜を形成する方法は次の工程を含む:表面上に上記所定の材料のアモルファスおよび/または多結晶膜12を有する第1の基板10が準備される;この第1の基板に疎水性直接結合(分子付着)によって、第2の基板20が結合され、上記第2の基板は、その表面上に所定の結晶配向の単結晶参照膜21を有する;少なくとも、アモルファスおよび/または多結晶膜に熱処理が適用され、上記熱処理は、このアモルファスおよび/または多結晶膜12の少なくとも一部に参照膜21の結晶配向に沿って固相再結晶を受けさせるように設計され、この参照膜は再結晶種として機能を果たす;少なくとも部分的に再結晶された膜は、参照膜の少なくとも一部から分離される。  (もっと読む)

(もっと読む)

膜製造方法

【課題】基板上に薄膜成長核を形成する場合に、大気圧環境下で、高温プロセスを排除し、かつスループットを低下させることなく、さらには薄膜成長核の無駄を発生させることなく容易に薄膜成長核を形成することにより膜製造設備のコストの低減及び膜製造コストの低減を図ることができる膜製造方法を提供する。

【解決手段】金属若しくは半導体を構成する元素、又はその元素からなるイオンを組成中に含む物質の溶液又は懸濁液を、基板上に塗布し、乾燥させた後、大気圧水素プラズマにて曝露処理することにより、基板上に薄膜を形成するための薄膜成長核を形成する。

(もっと読む)

ウェーハおよびウェーハの製造方法

【課題】異なる格子の基板上に成長した良質なエピタキシャル層を備えたウェーハおよびウェーハ製造方法の提供。

【解決手段】単結晶の第1の材料の基板はオンアクシスシリコン基板であり、オンアクシスシリコン基板上に第2の材料を成長させるウェーハの製造方法に関し、第2の材料が、第1の材料上にエピタキシャル成長し、第1の材料の格子とは異なる格子を持っている。オンアクシスシリコン基板を研磨ステップ104で研磨して、ウェーハ表面粗さを増大させる。SiGe層である傾斜バッファ層及び緩和層をウェーハ上に形成した後、CMP最終研磨108を実施する。上述のタイプの方法により解決され、基板の最終表面仕上げの前に第2の材料の成長を実施する。

(もっと読む)

薄膜半導体層の形成方法

【課題】 半導体層の表面に、その半導体層よりも非常にキャリア濃度の大きい半導体層を形成する高キャリア濃度の薄膜半導体層の形成方法を提供する。

【解決手段】 半導体層1表面の自然酸化膜または250℃以下の低温で生成した酸化膜4を還元して形成される活性化した金属元素と結合させることにより、半導体層1よりも高キャリア濃度で、かつ、バンドギャップが前記半導体層より大きい薄膜化合物半導体層2を形成する。この上に、SiN:Hからなる保護層3を設けることが薄膜を保護するために好ましい。

(もっと読む)

グレーデッドエピタキシャル成長を用いた半導体品の製造プロセス

【課題】緩和III−V族またはII−VI族マテリアルオンインシュレータの製造方法の提供。

【解決手段】緩和Si1−yGey層104を有する半導体構造の形成プロセスは、第1の基板上へのグレーデッドSi1−xGexバッファ層102の堆積であって、前記Ge濃度xはゼロから値yまで増加するものである堆積、緩和Si1−yGey層104の堆積、前記緩和Si1−yGey層104中にイオンを導入して第1のヘテロ構造を規定、前記第1のヘテロ構造を第2の基板108に接合して第2のヘテロ構造を規定、および前記導入されたイオンの領域での前記第2のヘテロ構造の分割であって、前記緩和Si1−yGey層104の表層部分は前記第2の基板上108に残るものである分割を含む。

(もっと読む)

窒素化合物半導体基板の製造方法および窒素化合物半導体基板

【課題】結晶性のよい窒素化合物半導体層が得られ、しかも低コストで生産性のよい窒素化合物半導体基板の製造方法を提供する。

【解決手段】所定厚さの表面Si層3と埋め込み絶縁層4とを有するSi基板1を準備する工程と、上記Si基板1を炭素系ガス雰囲気中で加熱して上記表面Si層3を単結晶SiC層6に変成させる際に、上記埋め込み絶縁層4との界面8近傍のSi層を残存Si層5として残す工程と、表面の単結晶SiCに対してさらに窒素化合物半導体層15をエピタキシャル成長させる工程とを行なう。

(もっと読む)

シリコン上にバッファ層構造を形成する方法および当該方法により形成された構造

【解決手段】 微小電子デバイスを形成する方法および対応する構造を記載する。当該方法は、基板にGaSb核生成層を形成する段階と、GaSb核生成層にGa(Al)AsSbバッファ層を形成する段階と、Ga(Al)AsSbバッファ層にIn0.52Al0.48As下側バリア層を形成する段階と、In0.52Al0.48As下側バリア層にInxAl1−xAsグレーデッド層を形成する段階とを備えるとしてよい。当該方法によれば、欠陥の少ない、勾配をつけたInGaAsベースの量子井戸構造を有するデバイスを製造することができる。 (もっと読む)

21 - 40 / 97

[ Back to top ]