Fターム[5F152LM09]の内容

再結晶化技術 (53,633) | 一般エピタキシャル成長技術 (652) | 成長技術以外 (353)

Fターム[5F152LM09]に分類される特許

1 - 20 / 353

炭化珪素半導体装置の製造方法

III族窒化物半導体デバイスの製造方法

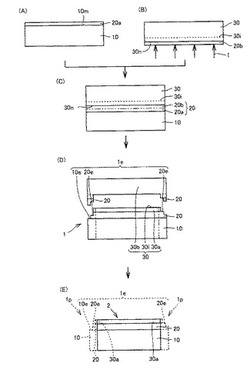

III族窒化物複合基板の製造方法

【課題】支持基板とIII族窒化物層との接合が良好なIII族窒化物複合基板の製造方法を提供する。

【解決手段】本III族窒化物複合基板の製造方法は、目標とする基板径より大きい径の主面10mを有する支持基板10と、目標とする基板径より大きい径の主面30nを有しその主面30nから所定の深さの位置にイオン注入領域30iが形成されたIII族窒化物基板30とを、中間層20を介在させて貼り合わせ、III族窒化物基板30をイオン注入領域30iにおいてIII族窒化物層30aと残りのIII族窒化物基板30bとに分離することにより、支持基板10上に中間層20を介在させてIII族窒化物層30aが接合された第1のIII族窒化物複合基板1を形成し、第1のIII族窒化物複合基板1の外周部を除去することにより目標とする基板径に等しい径の主面を有する第2のIII族窒化物複合基板2を得る。

(もっと読む)

β−Ga2O3系基板の製造方法、及び結晶積層構造体の製造方法

【課題】還元雰囲気や不活性ガス雰囲気下におけるドナー濃度の変化が抑えられたβ−Ga2O3系基板の製造方法、及び還元雰囲気や不活性ガス雰囲気下において品質のばらつきの小さい高品質な結晶膜をエピタキシャル成長させることのできる結晶積層構造体の製造方法を提供する。

【解決手段】IV族元素を含むβ−Ga2O3系結晶からβ−Ga2O3系基板を切り出す工程を含み、還元雰囲気及び不活性ガス雰囲気の少なくともいずれか一方を含む雰囲気下でのアニール処理が、前記β−Ga2O3系基板を切り出す前の前記β−Ga2O3系結晶、又は切り出された前記β−Ga2O3系基板に施される、β−Ga2O3系基板の製造方法を提供する。

(もっと読む)

エピタキシャルウエーハ及びその製造方法

【課題】 本発明は、シリコンウエーハ中の酸素等不純物の悪影響がエピタキシャル層の撮像素子形成部分まで及ばないエピタキシャルウエーハ及びその製造方法を提供することを目的とする。

【解決手段】 撮像素子製造用のエピタキシャルウエーハを製造する方法であって、前記エピタキシャル層の成長前に、前記撮像素子の製造後において前記エピタキシャル層中の酸素濃度が4×1017atoms/cm3以上となる領域の厚さXを計算し、前記エピタキシャル層の成長において、前記エピタキシャル層を、前記厚さXに加えて、更に前記撮像素子の製造後におけるエピタキシャル層中の酸素濃度が4×1017atoms/cm3未満となる領域の厚さが6μm以上となる厚さで成長することを特徴とするエピタキシャルウエーハの製造方法。

(もっと読む)

貼り合わせSOIウェーハの製造方法

【課題】 本発明は、SOI層の膜厚の面内均一性の良好なSOIウェーハを製造する方法を提供することを目的とする。

【解決手段】 イオン注入層が形成されたボンドウェーハのイオン注入された側の表面とベースウェーハの表面とを絶縁膜を介して貼り合わせた後、前記ボンドウェーハの一部を前記イオン注入層で剥離して、貼り合わせSOIウェーハを作製し、その後、平坦化処理を行う貼り合わせSOIウェーハの製造方法であって、

前記剥離後の貼り合わせSOIウェーハに対し、前記SOI層表面の周辺部の自然酸化膜が除去され、中央部の自然酸化膜が残存するように、水素ガスを含む雰囲気でRTA処理を行い、前記中央部に自然酸化膜が残存した貼り合わせSOIウェーハに対し、前記SOI層の面内膜厚レンジが1.5nm以下となるように前記平坦化処理を行うことを特徴とする貼り合わせSOIウェーハの製造方法。

(もっと読む)

III族窒化物複合基板

【課題】支持基板と酸化物膜との接合強度および酸化物膜とIII族窒化物層との接合強度が高いIII族窒化物複合基板を提供する。

【解決手段】本III族窒化物複合基板1は、支持基板10と酸化物膜20とIII族窒化物層30aとを含み、支持基板10は多結晶で形成され、III族窒化物層30aは少なくともc軸方向に配向しているIII族窒化物結晶で形成され、酸化物膜20は不純物が添加され、不純物の濃度は、酸化物膜20において支持基板10側の第1主面20sからIII族窒化物層30a側の第2主面20tにかけて膜厚方向で変化し、第1主面20sにおける不純物の濃度は第2主面20tにおける不純物の濃度よりも高い。

(もっと読む)

複合基板の製造方法

【課題】結晶成長用基板に形成した半導体結晶層を転写先基板に転写する場合の犠牲層のエッチング速度を高める。

【解決手段】半導体結晶層形成基板の上に犠牲層および半導体結晶層を順に形成するステップと、犠牲層の一部が露出するように半導体結晶層をエッチングし、半導体結晶層を複数の分割体に分割するステップと、転写先基板に接することとなる半導体結晶層形成基板側の第1表面と、第1表面に接することとなる転写先基板側の第2表面と、が向かい合うように、半導体結晶層形成基板と転写先基板とを貼り合わせるステップと、半導体結晶層形成基板および転写先基板をエッチング液に浸漬して犠牲層をエッチングし、半導体結晶層を転写先基板側に残した状態で、転写先基板と半導体結晶層形成基板とを分離するステップと、を有し、前記半導体結晶層が、GexSi1−x(0<x≦1)からなる、複合基板の製造方法を提供する。

(もっと読む)

スイッチング素子

【課題】逆ピエゾ効果が効果的に抑制され、オフ時の高電界状態であっても、ゲート電極近傍でクラックの発生が抑止されたスイッチング素子を提供する。

【解決手段】スイッチング素子1は、電子走行層13と、電子走行層13の上面に形成され、バンドギャップが電子走行層13より大きく電子走行層13とヘテロ接合する電子供給層14と、ソース電極15とドレイン電極16と、ソース電極15とドレイン電極16の間に配置されたゲート電極17とを備え、ゲート電極の下方に、電子供給層14に替えて、逆ピエゾ抑制層20を配置してなる。逆ピエゾ抑制層20は、ヘテロ接合よりも格子不整合が緩和された状態で電子走行層13と接合するように、その組成等が調整されており、ゲート電極17との接触領域A2のドレイン電極16側境界B4を跨ぐように配置される。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】多様な構造を実現することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1の上方に形成された化合物半導体層2と、が設けられている。化合物半導体層2には、第1の不純物の活性化により発生した第1導電型のキャリアを含む第1の領域2aと、第1の不純物と同一種類の第2の不純物の活性化により発生したキャリアを、第1の領域2aよりも低濃度で含有する第2の領域2bと、が設けられている。

(もっと読む)

半導体基板の製造方法及び半導体装置

【課題】基板に形成された窒化ガリウム系半導体で形成された半導体層におけるドーパント濃度がばらつくと、半導体層を用いた半導体装置の特性がばらつくので、半導体層におけるドーパント濃度のばらつきが抑えられた層を有する半導体基板を得る。

【解決手段】基板に、窒化ガリウム系半導体で形成された半導体層を形成する半導体層形成段階と、半導体層に、中性子線を照射して、半導体層に含まれるガリウム原子の一部をゲルマニウム原子に変換する照射段階と、を備える半導体基板の製造方法を提供する。

(もっと読む)

半導体装置の作製方法

【課題】複数のトランジスタが高集積化された素子の少なくとも一のトランジスタに、作製工程数を増加させることなくバックゲートを設ける半導体装置を提供する。

【解決手段】複数のトランジスタが上下に積層されて設けられた素子において、少なくとも上部のトランジスタ102は、半導体特性を示す金属酸化物により設けられ、下部のトランジスタ100が有するゲート電極層を上部のトランジスタのチャネル形成領域と重畳するように配して、ゲート電極層と同一の層の一部を上部のトランジスタ102のバックゲートBGとして機能させる。下部のトランジスタ100は、絶縁層で覆われた状態で平坦化処理が施され、ゲート電極が露出され、上部のトランジスタ102のソース電極及びドレイン電極となる層に接続されている。

(もっと読む)

薄膜製造方法、それを用いた半導体デバイスの製造方法およびそれらに用いられる半導体薄膜部品

【課題】高品質な半導体薄膜を製造する薄膜製造方法を提供する。

【解決手段】薄膜製造方法は、a−Si膜等の半導体薄膜を第1の基板上に堆積する工程S1と、第1の基板をエッチングして第1の基板と半導体薄膜との間に中空部を形成する工程S2と、半導体薄膜に第2の基板を接触させる工程S3と、半導体薄膜に第2の基板を押し付け、または半導体薄膜が溶融する強度を有するレーザ光を半導体薄膜に照射する工程S4と、第1の基板を半導体薄膜から引き離す工程S5とを備える。

(もっと読む)

単結晶の半導体層を支持基板上に転写する方法

【課題】単結晶の半導体層を支持基板上に転写し、転写された層がもはや脆化注入によって生成される可能性のある結晶欠陥を含まない方法を提供する。

【解決手段】単結晶の半導体層3を支持基板上に転写する方法に関し、(a)ドナー基板31に注入種を注入するステップと、(b)ドナー基板31を支持基板に接合するステップと、(c)層3を支持基板上に転写するためにドナー基板31を破壊するステップと、前記単結晶の層3の第2の部分35の結晶格子の秩序を乱すことなしに、転写されるべき単結晶の層3の部分34が非晶質にされるステップであり、部分34、35が、それぞれ、単結晶の層3の表面部分および埋め込み部分であるステップと、非晶質の部分34が500℃未満の温度で再結晶化されるステップであり、第2の部分35の結晶格子が再結晶化のための種結晶として働くステップとを含む。

(もっと読む)

GaN薄膜貼り合わせ基板およびその製造方法、ならびにGaN系高電子移動度トランジスタおよびその製造方法

【課題】バッファリーク電流およびゲートリーク電流が抑制された高性能のHEMTを提供する。

【解決手段】本GaN薄膜貼り合わせ基板の製造方法は、GaNバルク結晶10の主表面から0.1μm以上100μm以下の深さの面10iへの平均注入量が1×1014cm-2以上3×1017cm-2以下の水素イオン注入工程と、水素イオン注入されたGaNバルク結晶10の上記主表面へのGaNと化学組成が異なる異組成基板20の貼り合わせ工程と、GaNバルク結晶10の熱処理によりGaNバルク結晶10を水素イオンが注入された深さの面10iにおいて分離することによる異組成基板20上に貼り合わされたGaN薄膜10aの形成工程と、を含む。GaN系HEMTの製造方法は、上記GaN薄膜貼り合わせ基板1のGaN薄膜10a上への少なくとも1層のGaN系半導体層30の成長工程を含む。

(もっと読む)

半導体素子の製造方法

【課題】SiC半導体基板の不純物元素を捕捉・固定するためのゲッタリング層の形成を含む半導体素子の製造方法を提供する。

【解決手段】SiC基板10上にSiCエピタキシャル層16を形成し、該エピタキシャル層16にイオン注入および熱処理を行なって半導体素子を製造する方法において、上記SiC基板10よりも欠陥密度の高いゲッタリング層13を形成する工程を含むことを特徴とする半導体素子の製造方法。

(もっと読む)

半導体基板及びその製造方法

【課題】絶縁層埋め込み型半導体の炭化珪素基板において、電子デバイス作製に不可避である、低抵抗p型不純物層を形成するための工業的な方法を提案すること。

【解決手段】絶縁層埋め込み型半導体炭化珪素基板に、例えば、アルミニウムイオンを注入しp型不純物層を形成させ、次いで熱処理することからなる、p型不純物層を有する絶縁層埋め込み型半導体炭化珪素基板の製造方法。

(もっと読む)

シリコン−オン−インシュレーター構造及びバルク基板に対するSiGeの堆積

【課題】欠陥を最小限としながら、SiGe−オン−インシュレーター構造を製造するため及びシリコン上に歪み緩和SiGe層を製造するための方法を提供する。

【解決手段】アモルファスSiGe層600が、トリシラン及びGeH4からCVDによって、ドーパントの1以下のモノレイヤー上に堆積される。これらのアモルファスSiGe層600は、融解または固相エピタキシー(SPE)プロセスによってシリコン上に再結晶される。融解プロセスは、好ましくは、全体のゲルマニウム含量を希釈するようなゲルマニウムの拡散も引き起こし、そして絶縁体の上層のシリコン500を実質的に消費する。SPEプロセスは、下地のシリコン500中へのゲルマニウムの拡散を用いてまたは用いずに実際され得、従って、SOI及び従来の半導体基板に適用可能である。

(もっと読む)

半導体の製造方法及び半導体装置

【課題】複雑な工程を経ることなく、通常の半導体製造装置を使用して、低コストで、半導体装置の、低電圧動作、高集積性を実現する。

【解決手段】次の工程(1)〜(5)で半導体装置を製造する。(1)シリコン結晶製の半導体支持基板の表面を洗浄し、酸化被膜を除去して、結晶面を露出させる工程、(2)該結晶面上に高誘電率非晶質薄膜を低温で堆積する工程、(3)該高誘電率非晶質薄膜の結晶化開始温度よりも低いプレアニール温度で該高誘電率非晶質薄膜をプレアニールする工程、(4)該半導体支持基板を選択的に急速加熱することにより該高誘電率非晶質薄膜内部に基板界面から該薄膜表面方向に向けて温度が低くなる急峻な温度勾配を形成することにより該高誘電率非晶質薄膜を結晶化して、エピタキシャル薄膜を形成する工程、(5)該エピタキシャル薄膜の上面に半導体結晶の配向膜を形成する工程を有する。

(もっと読む)

炭化珪素単結晶ウェハ

【課題】デバイス作製に供用可能なウェハ面積部分を増大し、かつ大口径化に伴って増大する加工負荷を回避できる炭化珪素単結晶ウェハを提供する。

【解決手段】ウェハの特定の方位端に総面積の小さい加工欠損部、あるいは非対称な形状を有するノッチ状の加工欠損部を有する炭化珪素単結晶ウェハ。

(もっと読む)

1 - 20 / 353

[ Back to top ]