Fターム[5F152LN02]の内容

再結晶化技術 (53,633) | 格子整合、格子不整合技術 (1,553) | 目的 (706) | 歪みによる悪影響防止 (524)

Fターム[5F152LN02]の下位に属するFターム

転位、クラック等の低減又は抑制 (334)

凹凸の低減 (54)

反りの低減 (63)

Fターム[5F152LN02]に分類される特許

61 - 73 / 73

CMOSプロセス中に歪み半導基板層を保護する方法

Si/SiGeヘテロ構造をベースとしたウェハで不都合な表面材料の多量の消費を回避する酸化方法を、様々な中間CMOS熱酸化ステップに代えて行う。まず、酸化物堆積法を利用して、表面シリコンをほとんどまたは全く消費することなく、任意の厚さの酸化物を形成する。このような酸化物、例えばスクリーン酸化物およびパッド酸化物は、表面層との反応および表面層の消費によってではなく、表面層への堆積によって形成される。別の態様では、酸化物の堆積は、短時間の熱酸化ステップ、例えば急速熱酸化によって行われる。この場合、熱酸化が短時間であるために、表面Siはほとんど消費されず、Si/酸化物境界面は高い品質を有する。次に、堆積によって、この酸化物の厚みを所望の最終厚さにまで増大させる。さらに、この薄い熱酸化物層は、バリヤ層として働くことができ、これにより、後続の酸化物堆積と関連する汚染を防ぐことができる。  (もっと読む)

(もっと読む)

格子調整半導体基板の作製

格子調整半導体基板を形成する方法が、転位が優先的に形成されるストライプ領域(16)を、シリコン基板(10)の表面上に形成する工程と、ストライプ上に第1SiGe層(18)を成長させ、ストライプ領域の間の第1SiGe層を横切って第1転位(20)を優先的に延ばし、ストライプ(16)に直交する方向の、第1SiGe層中の歪を緩和する工程と、第1SiGe層の上に第2SiGe層を成長させ、第2SiGe層中に第2転位(22)を優先的に形成し、第1転位(20)に直交する方向に第2SiGe層中の歪を緩和する工程とを含む。そのように形成された転位は、2つの互いに直交した方向に材料を緩和し、一方、2組の転位は相互作用しないように間隔をおいて配置されている。これにより、貫通転位の密度と、表面粗さが大幅に低減され、能動デバイス中で電子を散乱し電子の移動速度を低減する原子格子の崩壊を減らすことにより、仮想基板の特性を向上させる。  (もっと読む)

(もっと読む)

半導体エピタキシャル基板

【目的】エピタキシャル成長面の凹凸が小さく、良好な特性を有し、生産性に優れた半導体エピタキシャル基板を提供する。

【構成】基板の結晶学的面方位が、1つの{100}面の結晶学的面方位から傾いており、その傾きの大きさが0.05°以上0.6°以下である単結晶砒化ガリウム基板上にエピタキシャル成長により結晶が形成されており、エピタキシャル結晶の少なくとも一部がInx Ga(1-x) As結晶(ただし0<x<1)であり、かつエピタキシャル成長が熱分解気相成長方法によって行われることを特徴とする半導体エピタキシャル基板。

(もっと読む)

ホウ素またはヘリウムと、水素とともにシリコンを注入することによって、Ge含有量が高い緩和Si1−XGeX(0<x<1)層を形成する方法

【課題】 水素注入ドーズおよび/またはアニーリング温度および時間を低減させることによって、費用を削減し、かつ、膜の性質を向上させることができる緩和Si1−XGeX(0<x<1)層の形成方法を提供する。

【解決手段】 本発明による、半導体デバイスにおいて、ゲルマニウム含有量が高い緩和Si1−XGeX(0<x<1)層を形成する方法は、シリコン基板を準備することと(12)、歪Si1−XGeX(0<x<1)層を堆積することと(14)、歪SiGe層内にイオンを注入することであって、イオンは、シリコンイオンと、ホウ素およびヘリウムからなるイオンの群から選択されるイオンとを含み、H+イオンを注入することをさらに包含する、ことと(16、18)、アニーリングすること(20)により歪SiGe層を緩和し、それにより、第1の緩和SiGe層を形成することと、半導体デバイスを完成することとを包含する。

(もっと読む)

多層構造の製造方法

本発明は、半導体材料製の多層構造用の製造方法に関し、この構造は、第1半導体材料製の基板(20)と、第2半導体材料製の表面薄層を備え、これらの2つの半導体材料は実質的に異なる格子定数を有する。この方法は、支持基板(100)上に表面薄層を備える層(110)を製造するステップと、支持基板及び堆積層によって形成される集合体(10)中に脆化ゾーンを形成するステップと、集合体(10)に対象基板(20)をボンディングするステップと、この脆化ゾーンのレベルで分離するステップと、得られる構造の表面を処理するステップとを含むことを特徴とする。  (もっと読む)

(もっと読む)

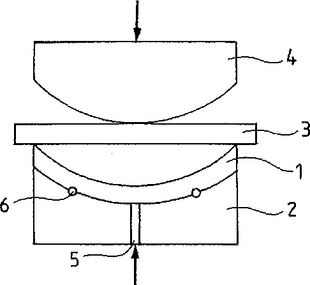

応力下の構造体の組立により複合構造体を作製する方法

本発明は、複合マイクロエレクトロニック構造体の作製方法に関し、2つの基本マイクロエレクトロニック構造体1、3が、その2つの結合面で組み立てられる。本発明は、組立前に、接線応力状態における差が組み立てられる2つの面間で引き起こされ、この差が、組立条件に対する所与の条件下で、組立構造体内で所定の応力状態を得るように選択されることを特徴とする。  (もっと読む)

(もっと読む)

キャップ層および埋込みゲートを有する窒化物ベースのトランジスタを作製する方法

ショットキーコンタクトなどのゲートコンタクトを形成する前にゲート埋込み部のアニーリングを行うことにより、ゲートリークが低減され、かつ/またはトランジスタなどの半導体デバイス内に高品質のゲートコンタクトを提供することができる。アニーリング中に封入層を使用することで、トランジスタのゲート埋込み部内の半導体への損傷がさらに低減される。アニーリングを、例えばデバイスのオーミックコンタクトのアニーリングによって提供することができる。したがって、埋込み部を形成する際のエッチングにより損傷をきたした埋込みゲートを提供することによって生じ得るゲート領域劣化が低減された、高品質のゲートコンタクトおよびオーミックコンタクトを提供することができる。  (もっと読む)

(もっと読む)

エピタキシャル層を形成する方法および装置

本発明は、シリコン基材上にIV族元素をベースとするエピタキシャル層を化学蒸着により堆積させる方法であって、キャリヤーガスとして窒素または希ガスの一種を使用する、方法を提供する。本発明はさらに、ガス入口(14)およびガス出口(16)を有するチャンバー(12)と、チャンバー(12)の中にシリコン基材を取り付ける手段(18)とを備えてなる化学蒸着装置(10)を提供するが、該装置は、入口に接続され、なおかつキャリヤーガスとして窒素または希ガスを供給するように配置されたガス供給源を包含する。  (もっと読む)

(もっと読む)

GaN系窒化膜を形成する方法

本発明は、サファイヤ基板上にSiaCbNc

(c,b>0,a≧0)の組成からなる第1層を形成する第1段階と、SiaCbNc

(c,b>0,a≧0)の組成からなる第1層の上にGaN成分を含む窒化膜を形成する第2段階と、を含むことを特徴とするGaN系窒化膜の形成方法に関する。  (もっと読む)

(もっと読む)

半導体基板を作製する方法

【課題】絶縁体上歪み半導体(SSOI)基板を作製する方法が提供される。

【解決手段】この方法で、歪み半導体は、あらかじめ形成された絶縁体上半導体基板の絶縁体層の上に直接配置された50nm未満の厚さを有する薄い半導体層である。本発明のSSOI基板を形成する際に、ウエハボンディングは使用されない。

(もっと読む)

空洞を有するシリコン基板上の高移動度MISFET半導体装置及びその製造方法

MISFETの高性能化を実現する高移動度歪みシリコン構造に、低欠陥かつ低コストで移動度を向上した半導体装置を提供する。MISFETの高性能化を実現する高移動度歪みシリコン構造として、空洞を有するシリコン基板上に、格子緩和シリコン・ゲルマニウム膜/濃度傾斜シリコン・ゲルマニウム膜を形成し、さらにその上に歪みシリコン膜を形成する。これにより、空洞近傍の格子の束縛が緩み、自由度が増すことにより、シリコン・ゲルマニウム膜の薄膜化が実現できるため、低欠陥かつ低コストで移動度を向上した半導体装置を提供できる。 (もっと読む)

縦型構造複合半導体装置

複数の縦型構造光学電子装置を結晶基板上に形成し、レーザリフトオフ処理で基板を取り除く工程を含んだ縦型構造光学電子装置の製造方法が開示されている。続いてこの方法は基板の代わりに金属支持構造体を形成する。1例ではこの形成には電気メッキ処理及び/又は無電メッキ処理が利用される。1例では縦型構造体はGaN型であり、結晶基板はサファイヤ製であり、金属支持構造体は銅を含む。本発明の利点には、高性能で生産効率が高い大量生産用の縦型構造LEDの製造が含まれる。 (もっと読む)

歪みシリコン・オン・インシュレータ(SSOI)およびこれを形成する方法

【課題】 コストが低く歩留まりの高い、引っ張り歪みSOI層を形成するための方法および引っ張り歪みSOI層の構造を提供する。

【解決手段】 歪みSiベースの層を製造するための方法、この層に製造されるデバイス、ならびに、かかる層およびデバイスを含む電子システムを開示する。この方法は、基板上にSiGe層をエピタキシャル成長させるステップと、このSiGe層において様々なGe濃度を生成するステップを含む。SiGe層内のGe濃度は、Ge濃度が突然かつ著しく増大する固有のGeオーバーシュート・ゾーンを含む。SiGe層上に、Siベースの層をエピタキシャル堆積させ、これによって引っ張り歪みが与えられる。また、典型的にSiまたはSiGeである歪みSiベースの層を、異なるバルク基板または絶縁体に転写可能であることも開示される。

(もっと読む)

61 - 73 / 73

[ Back to top ]