Fターム[5F152NN04]の内容

再結晶化技術 (53,633) | 基板材料(積層体を基板として扱う場合も含む) (4,266) | 半導体 (1,904) | 4族 (1,311) | Ge、SiGe (150)

Fターム[5F152NN04]に分類される特許

141 - 150 / 150

シャロウトレンチ分離プロセスおよび構造

集積回路(IC)を製造する方法は、シャロウトレンチ分離(STI)技術を利用する。シャロウトレンチ分離技術は歪みシリコン(SMOS)プロセス中において使用される。トレンチ(34)を形成した後、歪み材料(36)を形成する。このプロセスは、埋込酸化膜(BOX)層(14)上の化合物半導体層16上で利用される。  (もっと読む)

(もっと読む)

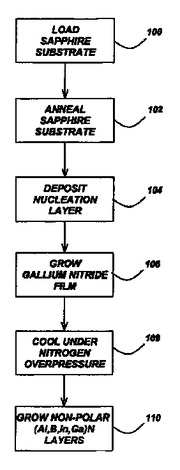

非極性(Al、B、In、Ga)N量子井戸

非極性a面GaN/(A1、B、In、Ga)N多重量子井戸(MQW)を製造する方法。a面MQWは、有機金属化学気相成長法(MOCVD)によって適切なGaN/サファイアテンプレート層上に成長し、井戸幅は20Å〜70Åの範囲である。a面MQWからの室温光ルミネセンス(PL)放射エネルギーは、自己無頓着ポアソン−シュレディンガー(SCPS)計算を使用してモデリングされた正方井戸傾向を伴った。最適PL放射強度は、a面MQWについて52Åの量子井戸幅で得られる。  (もっと読む)

(もっと読む)

Si:C−OIおよびSGOI上のシリコン・デバイスならびに製造方法

【課題】より費用効果が高くより簡略な、大きな引張り応力および圧縮応力をそれぞれnFETおよびpFETのチャネル中で生成する方法を提供すること。半導体構造および製造方法を提供すること。

【解決手段】この製造方法は、基板中に浅いトレンチ分離(STI)(25)を形成するステップと、基板上に第1の材料(30)および第2の材料(40)を設けるステップとを含む。第1の材料(30)および第2の材料(40)は、熱アニール・プロセスによって基板中に混合され、それぞれnFET領域の第1のアイランド(50)、およびpFET領域の第2のアイランド(55)を形成する。第1のアイランド(50)および第2のアイランド(55)の上に、材料層を形成する。STIは、緩和して、第1のアイランド(50)および第2のアイランド(55)の緩和を促進する。第1の材料(30)は、堆積または成長させたGe材料とすることができ、第2の材料(40)は、堆積または成長させたSi:CまたはCとすることができる。第1のアイランド(50)および第2のアイランド(55)の少なくとも一方の上に、歪みSi層を形成する。

(もっと読む)

半導体基板を作製する方法

【課題】絶縁体上歪み半導体(SSOI)基板を作製する方法が提供される。

【解決手段】この方法で、歪み半導体は、あらかじめ形成された絶縁体上半導体基板の絶縁体層の上に直接配置された50nm未満の厚さを有する薄い半導体層である。本発明のSSOI基板を形成する際に、ウエハボンディングは使用されない。

(もっと読む)

テンプレート層構成

ひずみ半導体層を形成するためのプロセス。かかるプロセスは、ウェハを加熱しながら、当該ウェハの上にわたって塩素ベアリングガス(例えば、塩化水素、塩素、四塩化炭層、及び、トリクロロエタン)を流すことを含む。ある実施例では、ひずみ半導体層(例えば、ひずみシリコン)を形成するためのテンプレート層として使用される半導体層に圧縮プロセスをする間、塩素ベアリングガスが流される。他の実施例では、圧縮操作の後、前記ウェハのポストベーク中、塩素ベアリングガスが流される。

(もっと読む)

(もっと読む)

埋込多孔質シリコン層の酸化によるシリコン・ゲルマニウムオンインシュレータ構造の形成

【課題】Ge含有層の下に生成される多孔質シリコンの層(または領域)を酸化することによりSiGeオンインシュレータを形成する簡単で直接的な方法を提供すること。

【解決手段】この方法は、正孔を多く含む領域が中に形成されたSi含有基板、およびこのSi含有基板の上のGe含有層を備える構造を提供するステップと、この正孔を多く含む領域を多孔質領域に転換するステップと、実質的に緩和したSiGeオンインシュレータ材料を提供するために、この多孔質領域を含む構造をアニールするステップとを含む。

(もっと読む)

半導体チップの製造方法

本発明によれば、成長基板ウエハ(1)が設けられ、前記成長基板ウエハ(1)の主平面(100)に対して平行に存在する分離ゾ−ン(4)が当該成長基板ウエハ(1)内に形成され、前記成長基板ウエハ(1)に補助支持体ウエハ(2)が接合され、前記分離ゾーン(4)の層から成長基板ウエハ(1)の補助支持体ウエハ(2)とは反対側部分(11)が当該分離ゾーン(4)に沿って分離され、前記補助支持体ウエハ(2)上に残った成長基板ウエハの残留部分(12)上に、後続の半導体層列(5)のエピタキシャル成長のための成長面(121)が形成され、前記成長面(121)上に半導体層列(5)がエピタキシャル成長され、前記半導体層列(5)上にチップ基板ウエハ(7)が被着され、前記補助支持体ウエハ(2)が分離され、前記半導体層列(5)とチップ基板ウエハ(7)の接続部が、相互に分離された半導体チップ(20)に個別化される。  (もっと読む)

(もっと読む)

実質的に緩和されたSiGeオン・インシュレータ基板材料およびそれを製作する方法(合金融点付近でのアニーリングによる高品質SGOI)

【課題】 低欠陥で実質的に緩和されたSiGeオン・インシュレータ基板材料を形成する方法を提供することにある。

【解決手段】 この方法は、Ge拡散に対する抵抗力のあるバリア層の上に存在する第1の単結晶Si層の表面上にGe含有層をまず形成するステップを含む。次に、加熱ステップは、最終的なSiGe合金の融点に近く、Geを保持しながら積層欠陥の形成を遅らせる温度で実行される。加熱ステップは、第1の単結晶Si層およびGe含有層全体にわたってGeの相互拡散を可能にし、それによりバリア層の上に実質的に緩和された単結晶SiGe層を形成する。その上、加熱ステップは最終的なSiGe合金の融点に近い温度で実行されるので、緩和の結果として単結晶SiGe層内に存続する欠陥はそこから効率よく消滅される。一実施形態では、加熱ステップは、2時間未満の期間の間、約1230〜約1320℃の温度で実行される酸化プロセスを含む。この実施形態は、最小表面ピッチングおよび低減されたクロスハッチングを有するSGOI基板を提供する。

(もっと読む)

エピタキシャル基板の製造方法

本発明は、エピタキシャル基板、例えば、GaN,SiGe,AlNまたはInNのエピタキシャル基板の製造方法、およびエピタキシャル基板上またはその中に作製された電子デバイスに関する。本発明の目的は、基板の影響を更に軽減することが可能であると同時に経済的に実行可能な、エピタキシャル基板の製造方法を提供することである。この目的は、以下のように達成することが出来る。すなわち、結晶性基板を用意し、原子種を基板に注入して脆性層を作成し、第1の温度で、基板の表面にエピタキシャル補強層を設け、第2の温度範囲で補強層を基板の副層とともに基板の残部から分離させて、これによって、この分離した材料によって、その上にホモエピタキシャル層またはヘテロエピタキシャル層の形成する擬似基板が作成される。 (もっと読む)

選択されたパラメータを有するSiGeオン・インシュレータ(SGOI)基板を製作する方法(酸化、薄型化、およびエピタキシャル再成長の組み合わせを使用するSiGe格子工学)

【課題】 SiGe厚さとGe比とひずみ緩和との相互依存を切り離すために格子工学が使用される、SiGeオン・インシュレータ(SGOI)基板を製作する方法を提供することにある。

【解決手段】 この方法は、選択された平面内格子定数と、選択された厚さパラメータと、選択されたGe含有量パラメータとを有するSiGe合金層を有するSiGeオン・インシュレータ(SGOI)基板材料を提供するステップであって、選択された平面内格子定数が一定値を有し、他のパラメータ、すなわち、厚さまたはGe含有量の一方または両方が調整可能な値を有するステップと、選択された平面内格子定数を維持しながら、他のパラメータの一方または両方を最終選択値に調整するステップとを含む。この調整は、どのパラメータが固定され、どのパラメータが調整可能であるかに応じて、薄型化プロセスまたは熱希釈プロセスのいずれかを使用して達成される。

(もっと読む)

141 - 150 / 150

[ Back to top ]