Fターム[5F152NN04]の内容

再結晶化技術 (53,633) | 基板材料(積層体を基板として扱う場合も含む) (4,266) | 半導体 (1,904) | 4族 (1,311) | Ge、SiGe (150)

Fターム[5F152NN04]に分類される特許

101 - 120 / 150

半導体膜の成膜方法

【課題】Ge系・SiGe系基板に高品質で平坦な半導体膜を形成する方法を提供する。

【解決手段】半導体膜の製造方法は、Ge系基板あるいはSiGe基板を塩酸溶液あるいは弗酸添加塩酸溶液で洗浄し、洗浄後の基板をCVD成膜装置内で水素アニールし、CVD層装置内に成膜ガスを導入し、半導体膜を形成する。

(もっと読む)

III族窒化物結晶の形成方法、積層体、およびエピタキシャル基板

【課題】従来よりも結晶品質の優れたIII族窒化物結晶およびその形成方法を提供する。

【解決手段】所定の基材に第1のIII族窒化物結晶を成長下地層2としてエピタキシャル形成してなる下地基板に対して、1250℃以上の所定の温度で熱処理を行う。これにより、成長下地層2の表面には、島状結晶2Iによる三次元的な微細な凹凸形状が形成される。係る下地基板の上に、結晶層4として、第2のIII族窒化物をエピタキシャル形成する。結晶層4と下地基板3との界面には多数の微細な空隙5を介在することになるが、該空隙5の存在により、下地基板3からの転位の伝搬が抑制されるので、結晶層4の転位密度は低下する。結果的に、良好な結晶品質の結晶層4を得ることが出来る。

(もっと読む)

結晶化度が改善された歪シリコン層を有する歪シリコンオンインシュレータ(SSOI)構造

本発明は、一般に歪シリコンオンインシュレータ(SSOI)構造とその製造方法に関するものである。この方法は、歪シリコン層の歪を維持しつつその結晶化度を改善するための高温熱アニールを含む。  (もっと読む)

(もっと読む)

直接チャネル応力

【課題】移動度の向上したMOSトランジスタを提供する。

【解決手段】半導体装置に伸張性のチャネル領域を形成する工程を包含する。一形態において、製造の中間段階において半導体装置のアモルファス部分を覆う応力層を歪ませる工程を包含する。上記半導体装置はマスクされており、応力層の一部における歪みは緩和される。製造途中の半導体装置のアモルファス部分を再結晶化することによって、応力層からの歪みを基板に伝達する。歪みの少なくとも一部は、装置の製造工程の間、基板に残存する。その結果、完成した装置の性能を向上させることができる。他の形態において、伸張性の応力層は、上記装置の第1部分を覆うよう形成され、圧縮性の応力層は、上記装置の第2部分を覆うよう形成される。伸張性の応力層は、PMOS装置において圧縮性のチャネルを形成し、圧縮性の応力層は、NMOS装置において伸張性のチャネルを形成する。

(もっと読む)

代替活性エリア材料の集積回路への組み込みのための解決策

結晶半導体基板上に代替材料のエリアを形成する方法、並びにこの方法により形成された構造。このような代替材料のエリアは、MOSFET又は電子デバイス若しくは光電子デバイスにおける活性エリアとしての使用に適している。  (もっと読む)

(もっと読む)

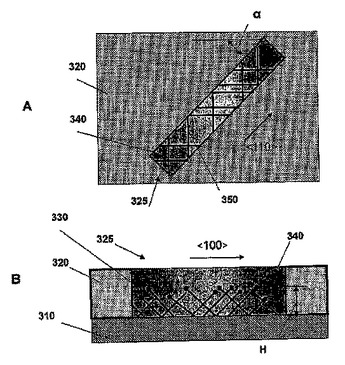

歪み超格子とその上の応力層とを含む半導体デバイス、及びその製造方法

半導体デバイスは、積層された複数の層群を有する歪み超格子層(325)、及び歪み超格子層の上方の応力層を含んでいる。歪み超格子層の各層群は、ベース半導体部分を画成する積層された複数のベース半導体モノレイヤーと、隣接し合うベース半導体部分の結晶格子内に拘束された少なくとも1つの非半導体モノレイヤーとを含んでいる。  (もっと読む)

(もっと読む)

機能性膜含有構造体、及び、機能性膜の製造方法

【課題】 成膜基板上に形成された機能性膜を、成膜基板から容易に剥離することができる剥離方法を含む機能性膜の製造方法を提供する。

【解決手段】 基板上に分離層を形成する工程(a)と、分離層上に、機能性材料を用いて形成される機能性膜を含む被剥離層を形成する工程(b)と、分離層に外力を与えて分離層の層内又は界面に割れを生じさせることにより、被剥離層を基板から剥離し、又は、被剥離層と基板との接合強度を低下させる工程(c)とを含む。

(もっと読む)

III族窒化物結晶の表面平坦性改善方法、エピタキシャル成長用基板、および半導体素子

【課題】作製条件に特段の制限を設けることなく、III族窒化物結晶における表面平坦性の向上を実現する方法を提供する。

【解決手段】単結晶の基材1とその主面上にエピタキシャル形成されたIII族窒化物結晶膜からなる上部層2とで構成されたエピタキシャル基板10を、窒素雰囲気下で1250℃以上の温度で加熱処理する。

【効果】表面におけるピットが低減することにより表面平坦性が改善し、また、III族窒化物結晶内の転位密度が熱処理前の1/2以下となる。

(もっと読む)

積層層構造およびその形成方法

【課題】基板と、少なくとも2つの化合物AおよびBを含む材料の複数の層のスタックとから成る積層層構造の製造方法を提供する。

【解決手段】化合物Aが基板3上でホモエピタキシャル成長又はヘテロエピタキシャル成長が十分にできるような結晶構造を有し、スタック5の層の少なくとも一部は、xが0≦x≦1の範囲を有する組成パラメータであり、且つ、組成パラメータ(1−xg)が対応する層の厚みの上に徐々に、特に線形に増大する勾配組成AxB(1−xg)を有する。表面粗さと転位密度に関して積層層構造1の品質を改善するため、スタック5内の勾配組成を有する層と後続層との界面で、組成パラメータが、勾配組成を有する層側の組成パラメータ(1−xg)よりも小さくなるように選択される。本発明は、また、このような積層層構造1を製造する方法にも関する。

(もっと読む)

エピタキシャル基板、半導体素子、エピタキシャル基板の製造方法、およびIII族窒化物結晶における転位偏在化方法

【課題】結晶品質の良好なIII族窒化物結晶の生成に好適なエピタキシャル基板を提供する。

【解決手段】オフ角が与えられてなるサファイア基材の上にIII族窒化物からなる上部層2を形成したうえで、1500℃以上で、好ましくは1650℃以上で加熱処理を施すことにより、上部層2の結晶品質を向上させるとともに該上部層2の表面に数原子層高さよりも大きな繰り返し段差を与えたエピタキシャル基板10を、III族窒化物結晶層3の成長用下地基板として用いる。III族窒化物結晶は段差部分からステップフロー成長するので、上部層2からの貫通転位はこれに伴い屈曲させられ、その後の結晶成長につれて偏在化する。得られるIII族窒化物結晶層3は良好な表面平坦性を有し、かつ、表面近傍の大部分は転移密度が1×107/cm2程度の低転位領域RE2となる。すなわち、エピタキシャル基板10は結晶品質のよいIII族窒化物結晶形成に好適であるといえる。

(もっと読む)

転位欠陥密度の低い格子不整合半導体構造およびこれに関連するデバイス製造方法

貫通転位が実質的にない上部分を有する制限されたエリア領域を備えている、モノリシック格子不整合半導体ヘテロ構造の製造、ならびにこのような格子不整合ヘテロ構造をベースとした半導体デバイスの製造。  (もっと読む)

(もっと読む)

混合結晶配向のチャネル及びソース/ドレイン領域をもつ電界効果トランジスタ

【課題】 混合結晶配向のチャネル及びソース/ドレイン領域をもつ電界効果トランジスタを提供すること。

【解決手段】 ハイブリッド配向基板は、n型電界効果トランジスタ(nFET)が電子移動度に最適な半導体の配向内に配置され、p型電界効果トランジスタ(pFET)が正孔移動度に最適な半導体の配向内に配置される、相補型金属酸化膜半導体(CMOS)回路の製造を可能にする。本発明は、最適な半導体の配向内に完全に形成されたFETの性能利点が、デバイスのチャネルを最適な配向をもつ半導体内に配置することを必要とするだけで実現できることを開示する。様々な新しいFET構造体が説明され、その全ては、FETのチャネルは、FETのソース及び/又はドレインとは異なる配向を有するという特徴を備えている。これらの新しいFETを組み込むことができるハイブリッド基板は、その製造方法と共に説明される。

(もっと読む)

基板上に歪層を製造する方法と層構造

【課題】

ウエーハ接着及び/又はウエーハ研磨なしに基板上に高い品質の歪層を製造する簡単な方法を提供すること。

【解決手段】

この発明は、歪をもたせる層に隣接した層に欠陥領域を形成する工程と、歪をもたせる層に少なくとも隣接した層を緩和させる工程とにより、基板上に歪層を製造する方法に関する。その歪層は別のエピタキシャル層に配置されることができる。そのように形成された層構造は種々の構成要素に好ましく適している。  (もっと読む)

(もっと読む)

基板上に歪層を製造する方法及び層構造

この発明は、基板上に歪層を有する層構造を製造する方法に関し、この方法は、歪を持たせる層に隣接する層内に、欠陥領域を形成する工程と、歪を持たせる層に隣接する少なくとも一つの層を緩和させる工程とを有する。この欠陥領域は、特に基板内に形成される。別のエピタキシャル層を配置することができる。このようにして形成した層構造は、有利には様々な種類の部品に適している。  (もっと読む)

(もっと読む)

半導体基板、半導体装置、半導体基板の製造方法および半導体装置の製造方法

【課題】 単結晶半導体層の結晶品質を向上させつつ、単結晶半導体層を絶縁体上に安価に形成する。

【解決手段】 選択エピタキシャル成長を行うことにより、非晶質半導体層3と接触するように開口部5内に埋め込まれた単結晶半導体層6を形成した後、エッチングガスまたはエッチング液をシリコン酸化膜2、4に接触させることにより、シリコン酸化膜2、4をエッチング除去して、単結晶半導体基板1と非晶質半導体層3との間に空隙7を形成し、単結晶半導体層6を種として非晶質半導体層3の熱処理を行うことにより、非晶質半導体層3が単結晶化された単結晶化半導体層8を形成してから、単結晶半導体基板1と単結晶半導体層8との間の空隙7に埋め込み絶縁層9を形成する。

(もっと読む)

格子整合されなかった基板上に応力緩和層構造を形成する方法及び電子素子及び/又は光導電素子内でのこのような層組織の使用

【課題】

本発明は、その都度異なる格子構造を有する基板上に1つ又は多数の層を有する単結晶応力緩和層構造を形成する方法に関する。特殊な構造では、この方法は、好ましくは応力緩和したSi−Ge層構造上にひずみシリコンを形成するために使用される。さらに本発明は、このような層組織を、例えばMOSFET,MODFET,共振トンネルダイオード,フォト検出器や量子カスケード・レーザのような素子で使用することに関する。  (もっと読む)

(もっと読む)

分離可能な基板の形成方法

本発明は、初期結晶性基板(1)の表面に成長マスク(20)を製造する方法に関し、本方法は、第一の材料からなる初期基板(1)の一方の側に第二の材料からなる層(2)を形成する工程、及び前記初期基板の表面領域を露出するため、第二の材料の層の厚さ内にパターンを形成することにより、前記初期基板の一方の側の領域を露出させ、前記領域を初期基板上の成長窓とする工程を含む。前記方法は、パターン形成が、第二の材料からなる層の下方に位置する初期基板(1)の表面層へのイオン注入によって行われ、この注入条件として、注入直後又は熱処理を行なった後で、前記初期基板の一方の側に、第一の材料が剥離された領域(5)ができることにより、第一の材料の剥離領域(5)を覆う第二の材料の領域が部分的に除去され、これによって初期基板(1)が部分的に露出し、初期基板上に成長窓(6)が形成されるような条件を用いることを特徴とする。本発明はまた、薄い結晶性の層を形成して受容基板上に移転する方法に関する。 (もっと読む)

構造均一性を有する半導体構造

組成変動を有する半導体層を備えている半導体構造を形成する。この半導体層の最上表面は、実質的にヘイズを有していない。  (もっと読む)

(もっと読む)

薄層を除去した後の多層構造を備えるウェハのリサイクル

半導体材料から選ばれた材料を含む有用層を除去した後にドナーウェハ(10)をリサイクル方法であって、ドナーウェハ(10)は基板(1)と多層構造(I)とを順次に備え、除去前の多層構造(I)は除去すべき有用層を備え、そのプロセスは除去が行われた側での物質除去を含み、物質除去の後に多層構造(I’)の少なくとも部分が残り、このバッファ構造(I’)の少なくとも部分は除去することができる別の有用層を1つ以上含み、有用層を再形成する補足的段階をともなわないことを特徴とする。本書はまた:本発明による少なくとも1つのリサイクル可能ドナーウェハ(10)から薄層を除去する方法、本発明によるリサイクル可能ドナーウェハ(10)に関する。  (もっと読む)

(もっと読む)

薄膜半導体素子およびその製造方法

本発明は、ゲルマニウムを含んでいる支持板(4)に配置されている薄膜半導体基体(2)を備えた半導体素子に関する。更にこの種の半導体素子を製造するための方法が記載されている。  (もっと読む)

(もっと読む)

101 - 120 / 150

[ Back to top ]