Fターム[5F152NN04]の内容

再結晶化技術 (53,633) | 基板材料(積層体を基板として扱う場合も含む) (4,266) | 半導体 (1,904) | 4族 (1,311) | Ge、SiGe (150)

Fターム[5F152NN04]に分類される特許

21 - 40 / 150

NMOSエピ層の形成方法

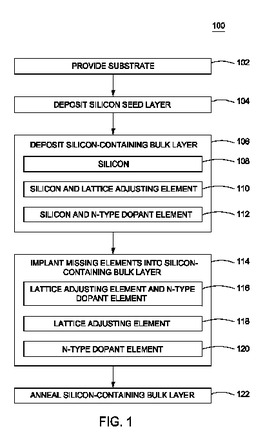

制御されたチャネル歪みおよび接合抵抗を有するNMOSトランジスタ、およびその製造方法が、本明細書で提供される。いくつかの実施形態において、NMOSトランジスタを形成するための方法は、(a)p型シリコン区域を有する基板を準備すること、(b)p型シリコン区域の上にシリコンシード層を堆積すること、(c)シリコン、シリコンおよび格子調整元素またはシリコンおよびn型ドーパントを備えるシリコン含有バルク層をシリコンシード層の上に堆積すること、(d)(c)で堆積されたシリコン含有バルク層に欠けている格子調整元素またはn型ドーパントのうちの少なくとも1つをシリコン含有バルク層の中に注入すること、(e)(d)の注入の後、シリコン含有バルク層をエネルギービームを用いてアニールすることを含むことができる。いくつかの実施形態において、基板は、その中に画定されたソース/ドレイン区域を有する、部分的に製造されたNMOSトランジスタデバイスを備えることができる。  (もっと読む)

(もっと読む)

半導体基板及び半導体基板の製造方法

【課題】半導体基板のアライメントマークを繰り返し使用する。

【解決手段】ベース基板にアライメントマークを形成する段階と、アライメントマークを形成する段階の後に、ベース基板上のアライメントマークを含む領域に、結晶成長を阻害する阻害層を形成する段階と、アライメントマークの位置を基準とする開口を形成すべき位置を示す情報に基づいて、阻害層におけるアライメントマークが設けられていない領域に、ベース基板を露出する開口を形成する段階と、開口内に半導体結晶を成長させる段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

半導体基板、電子デバイスおよび半導体基板の製造方法

【課題】シリコン基板を用いてGaN系の良質な半導体結晶層を形成する。

【解決手段】第1領域と第2領域とを表面に有する基板と、前記第1領域の上方に形成された第1半導体と、を含み、前記基板は、表面がSixGe1−x(0≦x≦1)であり、前記第1領域は、前記第2領域により囲まれ、前記第1半導体は、窒素原子を含有する3−5族化合物半導体であり、単結晶であり、且つ前記SixGe1−xと格子整合または擬格子整合し、前記第2領域は、前記第1領域とは性状が異なる半導体基板を提供する。

(もっと読む)

半導体基板、電子デバイスおよび半導体基板の製造方法

【課題】シリコン基板を用いてGaAs系の良質な半導体結晶膜を形成する。

【解決手段】第1領域と第2領域とを表面に有する基板と、前記第1領域の上方に形成された第1半導体と、を含み、前記基板は、表面がSixGe1−x(0≦x≦1)であり、前記第1領域は、前記第2領域により囲まれ、前記第1半導体は、砒素を含有する3−5族化合物半導体であり、単結晶であり、且つ前記SixGe1−xと格子整合または擬格子整合し、前記第2領域は、前記第1領域とは性状が異なる半導体基板を提供する。

(もっと読む)

半導体素子の製造方法

【課題】 半導体層のエッチング時間の短縮化が望まれている。

【解決手段】 第1の膜及び半導体膜がこの順番に形成された積層基板の前記半導体膜の上に、マスクパターンを形成する。マスクパターンをエッチングマスクとして、半導体膜をエッチングすることにより、凹部を形成するとともに、凹部の底面の一部の領域に第1の膜が露出し、他の領域には、半導体膜の残渣が残っている状態でエッチングを停止させる。凹部の底面に露出した第1の膜を厚さ方向及び横方向にエッチングすることにより、残渣の下に空洞を形成する。積層基板を浸漬させた液体に超音波を印加することにより、空洞の上に残留している残渣を積層基板から脱離させる。

(もっと読む)

結晶シリコンの少なくとも一つの極薄層を含む多層膜を製造する方法及び前記方法により得られたデバイス

【課題】 結晶シリコンの少なくとも一つの極薄層を含む多層膜を製作する、単純で負担がより少ない方法を提案すること。

【解決手段】 本発明は結晶シリコンの少なくとも一つの極薄層を有する多層膜を製作する方法に関し、前記膜は、結晶構造を有し、予め洗浄された表面を含む基板から製作される。本発明によれば、前記方法は前記洗浄された表面をSiF4、水素、及びアルゴンのガス混合物内で生成されたRFプラズマに当て、それにより前記基板に接触して微小空洞を含有する界面副層を備える結晶シリコンの極薄層を形成するステップa)と、結晶シリコンの前記極薄層上に少なくとも1層の材料を堆積させ、それにより少なくとも一つの機械的に強い層を含む多層膜を形成するステップb)と、前記多層膜で覆われた前記基板を400℃より高い温度でアニールし、それにより前記多層膜を前記基板から分離させるステップc)とを含む。

(もっと読む)

半導体デバイスおよび半導体構造の製造方法

【課題】 半導体結晶材料の作製またはこの半導体結晶材料を含む構造を提供する。

【解決手段】 第1の半導体結晶材料の表面の粗さは、低減されている。半導体デバイスは、第1の結晶材料の表面上に低欠陥の歪んだ第2の半導体結晶材料を含む。歪んだ第2の半導体結晶材料の表面の粗さは、低減されている。一実施例は、第1および第2の半導体結晶材料間の界面境界の不純物を減少させるプロセスパラメータを作成することによって、粗さが低減された表面を得ることを含む。一実施の形態では、第1の半導体結晶材料は、アスペクト比トラッピング技術を用いて欠陥をトラップするのに十分なアスペクト比を有する絶縁体の開口によって限定されることができる。

(もっと読む)

基板上に単結晶層を作製する方法

【課題】基板上に単結晶材料の層を成長させる方法を提供する。

【解決手段】第1単結晶材料から形成された露出領域を有する基板を、プロセスチャンバ中に配置する工程と、拡散制限ガスの存在下で、基板に向かって、第2材料の中性種のビームを供給し、プロセスチャンバ中の圧力を1×10−6torrから1×10−4torrの間にし、第2材料の中性種を露出領域上に吸着され、これにより第1単結晶材料の上にこれと接触して第2材料の単結晶層を成長させる工程とを含み、拡散制限ガスは、非反応性ガスからなる。

(もっと読む)

電界効果トランジスタの製造方法

【課題】高集積度化でき、電気射特性を維持しながら、低コスト化できる電界効果トランジスタの製造方法を実現する。

【解決手段】誘電性絶縁部層2’によって被覆されているバルクシリコンウエハ基板1’上に島状の各活性エリア10を互いに隣り合うようにそれぞれ設定する。バルクシリコンウエハ基板1’の表面上において、各活性エリア10を電界効果トランジスタの本体領域をフィン部3、5の形状で突出するように露出させて形成するために、誘電性絶縁部層2’を厚さ方向にエッチバックして絶縁体層2を形成する。上記本体領域に、チャネル領域部、上記チャネル領域部上のゲート誘電体8、ゲート誘電体8上のゲート電極4、および、ゲート電極4の自己整合マスクにより、チャネル領域部とは反対の伝導性型である不純物原子のドープによりソース領域部5およびドレイン領域部3を形成する。

(もっと読む)

半導体基板の製造方法

【課題】選択エッチング層のエッチング時の自然酸化による影響で化合物半導体層の損傷、結晶の転移が発生せず、信頼性の高い半導体基板の製造方法を提供する。

【解決手段】化合物半導体基板8上に、選択エッチング層3、応力緩和層9および応力緩和層9より大きいヤング率を有するIII−V族化合物半導体から成る化合物半導体層4をエピタキシャル成長法により順次積層させる積層工程と、選択エッチング層3、応力緩和層9および化合物半導体層4を所定パターンとなるようにエッチング除去するエッチング工程と、Si基板5の主面に化合物半導体層4の上面を直接接合法により接合させて、選択エッチング層3、応力緩和層9および化合物半導体層4が積層された化合物半導体基板8を貼りあわせる接合工程と、前記エッチング工程で残った選択エッチング層3をさらにエッチング除去することにより、Si基板5と化合物半導体基板8とを分離する分離工程とを含む。

(もっと読む)

半導体基板の作製方法および半導体装置

【課題】炭化シリコンを含む半導体基板の新たな作製方法を提供することを目的の一とする。または、炭化シリコンを用いた半導体装置を提供することを目的の一とする。

【解決手段】炭化シリコン基板にイオンを添加することにより、炭化シリコン基板中に脆化領域を形成し、炭化シリコン基板とベース基板とを絶縁層を介して貼り合わせ、炭化シリコン基板を加熱して、脆化領域において炭化シリコン基板を分離することにより、ベース基板上に絶縁層を介して炭化シリコン層を形成し、炭化シリコン層を1000℃〜1300℃の温度で熱処理して、炭化シリコン層の欠陥を低減することにより半導体基板を作製する。または、上述のようにして形成された半導体基板を用いて半導体装置を作製する。

(もっと読む)

半導体基板の再生処理方法及びSOI基板の作製方法

【課題】半導体膜が分離された後の分離後の半導体基板を、SOI基板作製に用いることが可能な再生半導体基板に再生する際に、分離後の半導体基板の取り代を削減し、1枚の半導体基板を再生使用できる回数を増やす半導体基板の再生処理方法を提供することを課題の一つとする。

【解決手段】半導体を酸化する酸化剤として機能する物質と、半導体の酸化物を溶解する物質と、半導体の酸化及び半導体の酸化物の溶解の減速剤として機能する物質と、を含む混合溶液を用いて、分離後の半導体基板の周辺部に残存した脆化層及び半導体層を選択的に除去することを特徴とする半導体基板の再生処理方法である。なお、イオン注入装置により水素ガスから生成される、H+イオンを注入することにより半導体基板に形成する脆化層を用いて、半導体基板から半導体膜を分離する。

(もっと読む)

減少した転位パイルアップを有する半導体ヘテロ構造および関連した方法

【課題】緩和した格子不整合の半導体へテロ構造を提供すること。

【解決手段】組成的に勾配した半導体層における転位パイルアップは、減少もしくは実質的に除かれ、これによって、増加した半導体デバイス歩合および製造性に導く。このことは、組成的に勾配したバッファ層の後に続く成長および緩和の前のスタート層としておよび/または組成的に勾配した層の成長および緩和中の少なくとも1つの中間層としてその表面にわたり実質的に均一に分布する複数のスレッディング転位を有する半導体層を導入することによって達成される。この半導体層は、半導体層の表面に近接して位置するシード層、およびそこに均一的に分布するレッディング転位を有することを含み得る。

(もっと読む)

III−V族加工基板の製造方法およびそのIII−V族加工基板

【課題】パッシベーション層を備え、改善した性能を持つデバイスを実現できるIII−V族加工基板およびその製造方法を提供する。

【解決手段】III−V族加工基板の製造方法は、<110>または<111>の結晶方位を持つ第1のIII−V化合物からなる上側層(2)を備えたベース基板(I)を用意すること、第2のIII−V化合物からなるバッファ層(3)を少なくとも形成することを含んだ、中間層(II)を形成することであって、中間層(II)は、ベース基板の上側層(2)の上に位置し、これと接触するようにすること、IV族半導体材料からなる擬似格子整合パッシベーション層(4)を成長させることであって、擬似格子整合パッシベーション層は、中間層(II)の上に位置し、これと接触するようにすることを含む。

(もっと読む)

半導体基板、半導体基板の製造方法、および電子デバイス

【課題】同一基板に形成されるHBTとFETとの相互影響を低減する。

【解決手段】第1半導体と、第1半導体の上方に形成された第2半導体とを備え、第2半導体は、P型の伝導型を示す不純物またはN型の伝導型を示す第1不純物原子と、第2半導体が第1不純物原子を有する場合のフェルミ準位を、第2半導体が第1不純物原子を有しない場合のフェルミ準位に近づける第2不純物原子とを有する半導体基板を提供する。一例として、当該第2半導体の多数キャリアは電子であり、第2不純物原子は、第1不純物原子を有する第2半導体のフェルミ準位を下降させる。第2半導体は3−5族化合物半導体であり、第2不純物原子が、ベリリウム、ボロン、炭素、マグネシウム、および亜鉛からなる群から選択された少なくとも1つであってもよい。

(もっと読む)

半導体基板の製造方法および半導体基板

【課題】単一半導体基板上にHBTおよびFETのような複数異なる種類のデバイスを形成するに適した半導体基板を製造する方法を提供する。

【解決手段】半導体を結晶成長させる反応容器内に第1不純物原子を構成要素として有する単体または化合物を含む第1不純物ガスを導入する段階を含む複数の段階を繰り返して、複数の半導体基板を製造する方法であって、第1不純物ガスを導入する段階の後に、製造された半導体基板を取り出す段階と、反応容器内に第1半導体を設置する段階と、反応容器内に、第1半導体内で第1不純物原子と反対の伝導型を示す第2不純物原子を構成要素として有する単体または化合物を含む第2不純物ガスを導入する段階と、第1半導体を第2不純物ガスの雰囲気中で加熱する段階と、加熱した前記第1半導体上に第2半導体を結晶成長させる段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

半導体基板の作製方法

【課題】炭化シリコンを含む半導体基板の新たな作製方法を提供することを目的の一とする。

【解決手段】シリコン基板表面に炭化処理を施して炭化シリコン層を形成し、シリコン基板にイオンを添加することにより、シリコン基板中に脆化領域を形成し、シリコン基板とベース基板とを絶縁層を介して貼り合わせ、シリコン基板を加熱して、脆化領域においてシリコン基板を分離することにより、ベース基板上に絶縁層を介して炭化シリコン層とシリコン層の積層構造を形成し、シリコン層を除去して炭化シリコン層の表面を露出させることにより半導体基板を作製する。

(もっと読む)

半導体基板、半導体基板の製造方法、電子デバイス、および電子デバイスの製造方法

【課題】結晶薄膜を有する半導体基板の設計および上記結晶薄膜の膜質および膜厚の制御を容易にできる半導体基板を提供する。

【解決手段】ベース基板と、ベース基板上に、一体にまたは分離して設けられ、化合物半導体の結晶成長を阻害する阻害層とを備え、阻害層は、ベース基板まで阻害層を貫通する複数の開口を有する複数の第1開口領域を有し、複数の第1開口領域のそれぞれは、内部に同一の配置で設けられた複数の第1開口を含み、複数の第1開口の一部は、電子素子が形成されるべき第1化合物半導体が設けられている第1素子形成開口であり、複数の第1開口の他の一部は、電子素子が形成されない第1ダミー開口である半導体基板を提供する。

(もっと読む)

発光サイリスタ、発光素子アレイ、発光装置および画像形成装置

【課題】 ベース層のキャリア濃度および厚み寸法を大きく設定することなく、発光強度に対する電流増幅率βの影響を抑制することのできる発光サイリスタ、発光素子アレイ、発光装置および画像形成装置を提供することである。

【解決手段】 発光サイリスタは、基板上に第1半導体層、第1半導体層と反対導電型の第2半導体層、第1半導体層と同じ導電型の第3半導体層、および第1半導体層と反対導電型の第4半導体層がこの順に積層されており、第3半導体層のバンドギャップは、第2半導体層のバンドギャップと略同一、かつ、第1および第4半導体層のバンドギャップより狭幅であり、第3半導体層は、基板側の第1領域と基板と反対側の第2領域とからなり、かつ、第1領域の不純物濃度は1×1016(cm−3)未満である。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】電子デバイスのスイッチング速度等の性能を向上させる。半導体基板の結晶性を向上させる。

【解決手段】ベース基板と、絶縁層と、SixGe1−x結晶層とをこの順に有する半導体基板であって、SixGe1−x結晶層上に設けられる阻害層と、SixGe1−x結晶層に格子整合または擬格子整合している化合物半導体とを備え、阻害層はSixGe1−x結晶層にまで貫通する開口を有し、かつ化合物半導体の結晶成長を阻害する半導体基板を提供する。また、上記開口の内部でSixGe1−x結晶層に格子整合または擬格子整合する化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

21 - 40 / 150

[ Back to top ]