Fターム[5F152NN04]の内容

再結晶化技術 (53,633) | 基板材料(積層体を基板として扱う場合も含む) (4,266) | 半導体 (1,904) | 4族 (1,311) | Ge、SiGe (150)

Fターム[5F152NN04]に分類される特許

41 - 60 / 150

半導体装置の製造方法及び半導体装置

【課題】 電界効果型トランジスタの動作速度を向上させる半導体装置の製造方法、及び半導体装置を提供する。

【解決手段】 ゲルマニウム基板の上にシリコンゲルマニウムを含むエピタキシャル成長層を形成する工程と、エピタキシャル成長層上に酸化物層を形成する工程と、エピタキシャル成長層を熱処理する熱処理工程と、を含み、熱処理工程における熱処理は、加熱温度が600℃以上900℃以下であり、ゲルマニウム基板の上にシリコンゲルマニウムからなるエピタキシャル成長層を形成する工程は、エピタキシャル成長層にシリコンが5%以上20%以下、及びゲルマニウムが80%以上95%以下の割合で含有するように形成する。

(もっと読む)

III族窒化物半導体からなるHFETの製造方法

【課題】III 族窒化物半導体からなるHFETの製造方法において、素子分離領域を容易に形成する方法を提供すること。

【解決手段】i−AlGaN層12表面側からレーザーを照射して、HFETとして動作させる素子領域を囲うようにして溝15を形成する(図2(c))。溝15の深さは、i−AlGaN層12表面からi−GaN層11に達する深さとする。この溝15によってi−AlGaN層12が取り除かれたため、この取り除かれた領域において2次元電子ガス層が消滅する。その結果、HFETとして動作させる素子領域は、溝15による素子分離領域によって電気的に分離される。

(もっと読む)

非極性または半極性(Ga、Al、In、B)N基板上に成長させられる素子

非極性または半極性の(Ga、Al、In、B)N基板上の(Ga、Al、In、B)N薄膜の成長形態を改良する方法であって、(Ga、Al、In、B)N薄膜は、非極性または半極性の(Ga、Al、In、B)N基板あるいはテンプレート上に直接成長させられ、成長の際に使用されるキャリアガスの一部は、不活性ガスから構成される。非極性または半極性の窒化物LEDおよびダイオードレーザは、本発明によって成長させられる平滑(Ga、Al、In、B)N薄膜上に成長させられてもよい。  (もっと読む)

(もっと読む)

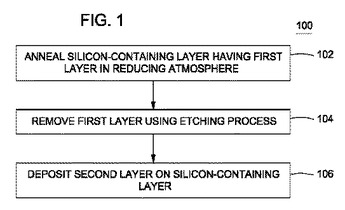

界面汚染を低減した層を堆積させる方法

本明細書では、界面汚染を低減した層の堆積方法を開示する。発明の方法は、有利には、堆積させた層間の汚染、例えば堆積させた層とその下にある基板または膜との間の界面の汚染を減少させる。幾つかの実施形態では、層の堆積方法は、第1の層が上に配置されたシリコン含有層を還元性雰囲気中でアニールすることと、アニールの後で、シリコン含有層を露出させるエッチングプロセスを使用して第1の層を除去することと、露出したシリコン含有層の上に第2の層を堆積させることとを含むことができる。  (もっと読む)

(もっと読む)

半導体材料の薄層の形成

GaAs、またはSiGeのようなゲルマニウム材料のいずれかの層を形成する方法を開示する。例えばゲルマニウム材料は、GaAs面上にエピタキシャル成長することができる。ゲルマニウム材料を一部の残留GaAsと共にレシーバ基板に転写するために、層転写が使用される。次いで残留GaAsは、GaAsとゲルマニウム材料との間の境界がエッチストップとなり、選択的エッチングによって除去することができる。 (もっと読む)

電界効果トランジスタ

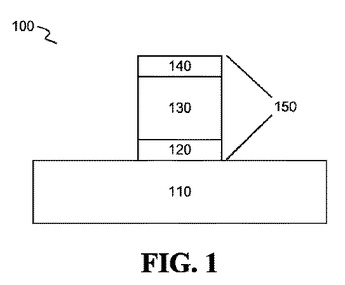

【課題】歪みチャネルを用いた場合のリーク電流を低減することができ、不良の発生を抑制して歩留まりの向上をはかる。

【解決手段】半導体基板10上に設けられた、基板10とは格子定数の異なる合金半導体からなる下地層20と、下地層20上に設けられた、下地層20とは格子定数が異なり、チャネル長方向及びチャネル幅方向の一方に引っ張り応力、他方に圧縮応力が付与されたチャネル半導体層30と、チャネル半導体層30を挟むように下地層20上に設けられたソース・ドレイン領域60,70と、チャネル半導体層30上にゲート絶縁膜40を介して設けられたゲート電極50とを備えた電界効果トランジスタであって、下地層20は、ソース・ドレイン領域60,70の下部に形成される空乏層61,71が下地層20内に収まる厚さよりも厚く形成され、且つ熱平衡臨界膜厚よりも薄く形成されている。

(もっと読む)

半導体装置、半導体装置の製造方法、半導体基板、および半導体基板の製造方法

【課題】化合物半導体と絶縁性材料との界面に形成される界面準位が低減した半導体装置を提供する。

【解決手段】閃亜鉛鉱型の結晶構造を有する3−5族化合物半導体と、3−5族化合物半導体の(111)面、(111)面と等価な面、または、(111)面もしくは(111)面と等価な面から傾いたオフ角を有する面に接する絶縁性材料と、絶縁性材料に接し、金属伝導性材料を含むMIS型電極とを備える半導体装置を提供する。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】基板と当該基板に形成される化合物半導体とを電気的に絶縁しつつ、結晶性に優れた化合物半導体を備えた半導体基板を提供する。

【解決手段】ベース基板と、ベース基板上に設けられたシード結晶と、シード結晶の上方に設けられた化合物半導体と、シード結晶と化合物半導体との間に設けられ、シード結晶よりも大きな抵抗率を有する高抵抗層とを備え、シード結晶と化合物半導体とが格子整合または擬格子整合している半導体基板を提供する。

(もっと読む)

ホウ素ドープ半導体ナノワイヤ及びその製造方法

【課題】成長軸方向に径の均一なホウ素ドープ半導体ナノワイヤ及びその製造方法を提供する。

【解決手段】成長軸方向に径の均一なホウ素ドープ半導体ナノワイヤは、次の工程を含む製造方法により製造できる。

工程(1):半導体原料ガスを用いて、基板上にIV族半導体ナノワイヤを成長させる;

工程(2):ジボランガスのみを導入することにより、前記半導体ナノワイヤの表面にホウ素膜を堆積させる;

工程(3):表面にホウ素膜を堆積させた前記ホウ素膜付き半導体ナノワイヤを、半導体ナノワイヤ(本体)の融点以下の温度で熱アニールする。

(もっと読む)

半導体基板の製造方法、半導体基板、電子デバイスの製造方法、および反応装置

【課題】耐熱性の低い部分を有する基板であっても加熱処理が可能となる、基板の熱処理方法を提供する。

【解決手段】熱処理される被熱処理部を備えるベース基板を熱処理して半導体基板を製造する方法であって、電磁波を吸収して熱を発生し、被熱処理部を選択的に加熱する被加熱部をベース基板上に設ける段階と、ベース基板に電磁波を照射する段階と、被加熱部が電磁波を吸収することにより発生する熱によって、被熱処理部の格子欠陥密度を低減する段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

半導体基板の製造方法、および半導体基板

【課題】改善された光子/電子の変換効率を備える半導体基板を製造する方法を提供する。

【解決手段】本発明は、半導体基板の製造方法に関する。当該方法は、絶縁型基板上に第1の半導体層(7)を設けるステップと、拡散バリア層(9)を設けるステップと、第2の半導体層(11)を設けるステップとを備える。拡散バリア層を設けることにより、高ドープされた第1の半導体層から第2の半導体層への拡散を抑制することが可能になる。本発明はまた、これに相当する半導体基板、および当該基板を備えるオプトエレクトロニクスデバイスに関する。

(もっと読む)

半導体装置の製造方法

【課題】横方向固相エピタキシャル成長法において単結晶膜成膜工程に要する時間を短縮し、半導体装置の製造を短時間で行う。

【解決手段】単結晶シリコン部403及び絶縁膜401が表面において露出したウエハ200を、構成元素としてSiを含むガスの雰囲気中に曝露し、単結晶シリコン部403及び絶縁膜401の上にアモルファスのシリコン膜402を成膜する成膜工程と、成膜工程後に、シリコン膜402を加熱して、単結晶シリコン部403を基にしてシリコン膜402を単結晶化させる加熱工程と、加熱工程後に、ウエハ200を構成元素としてSiを含むガス及び構成元素としてClを含むガスの混合雰囲気中に曝露し、単結晶化した部分を残留させつつ、単結晶化しなかった部分を除去する選択成長工程と、を含む半導体装置の製造方法であって、ウエハ200に対して、成膜工程、加熱工程及び選択成長工程を繰り返す。

(もっと読む)

歪み半導体デバイス用のゲルマニウム含有量が漸次変化した高ゲルマニウム化合物膜

ゲルマニウム含有量が漸次変化した高ゲルマニウム化合物領域を供する装置及び方法に係る実施例が全体として記載されている。他の実施例も記載及びクレームされている。  (もっと読む)

(もっと読む)

半導体デバイス用基板、半導体デバイス装置、設計システム、製造方法、および設計方法

【課題】結晶薄膜の膜質および膜厚を均一にする。

【解決手段】半導体デバイスを形成するためのデバイス用薄膜と、デバイス用薄膜を囲み、デバイス用薄膜の前駆体が結晶に成長することを阻害する阻害部と、前駆体が結晶に犠牲成長することによって形成された犠牲成長部であって、デバイス用薄膜の周辺に阻害部で隔てられて設けられた犠牲成長部と、犠牲成長部の上部を覆い、かつデバイス用薄膜の上部を露出する保護膜を備えた。保護膜はポリイミドであってもよい。

(もっと読む)

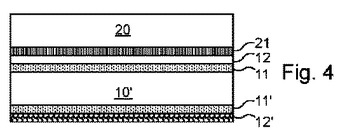

マイクロエレクトロニクス分野において単結晶膜を形成する方法

所定の材料の薄膜を形成する方法は次の工程を含む:表面上に上記所定の材料のアモルファスおよび/または多結晶膜12を有する第1の基板10が準備される;この第1の基板に疎水性直接結合(分子付着)によって、第2の基板20が結合され、上記第2の基板は、その表面上に所定の結晶配向の単結晶参照膜21を有する;少なくとも、アモルファスおよび/または多結晶膜に熱処理が適用され、上記熱処理は、このアモルファスおよび/または多結晶膜12の少なくとも一部に参照膜21の結晶配向に沿って固相再結晶を受けさせるように設計され、この参照膜は再結晶種として機能を果たす;少なくとも部分的に再結晶された膜は、参照膜の少なくとも一部から分離される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】高集積、高速且つ高性能な歪みSOI構造の縦型MISFETを得ること。

【解決手段】Si基板1上に酸化膜2を介して、横方向エピタキシャルSiGe層3が設けられ、SiGe層3は素子分離領域形成用の埋め込み絶縁膜4及び酸化膜2により島状に絶縁分離されている。SiGe層3上には選択的に縦方向エピタキシャルSiGe層7が設けられ、SiGe層7の側面には格子定数がやや小さい横方向エピタキシャル歪みSi層8が周設され、歪みSOI基板を形成しており、SiGe層7及び歪みSi層8の上部にはドレイン領域(10、11)が設けられ、SiGe層3全体、SiGe層7及び歪みSi層8の下部にはソース領域9が設けられ、歪みSi層8の側面にはゲート酸化膜12を介してゲート電極13が周設され、ドレイン領域11、ソース領域9及びゲート電極13には、それぞれ導電プラグ20を介してCu配線23が接続されている歪みSOI構造の縦型のMISFETを構成すること。

(もっと読む)

歪み層の緩和

第1のコンプライアント材料を含む第1の低粘度層を歪み材料層上に堆積するステップと、第2のコンプライアント材料を含む第2の低粘度層を歪み材料層上に堆積して第1のサンドイッチ構造を形成するステップと、第1の低粘度層および第2の低粘度層のリフローが引き起こされるように第1のサンドイッチ構造を加熱処理し、それによって歪み材料層を少なくとも部分的に緩和させるステップとを含む。 (もっと読む)

歪み層の弛緩及び転写

本発明は、ターゲット基板上に少なくとも部分的に弛緩された歪み物質を形成するための方法において、中間基板上の歪み物質層からアイランドを形成し、第1の熱処理により前記歪み物質アイランドを少なくとも部分的に弛緩し、前記少なくとも部分的に弛緩された歪み物質アイランドを前記ターゲット基板へと転写する、という順次行われるステップを含む方法に関する。 (もっと読む)

拡幅活性領域を有する半導体素子

半導体素子(10)を半導体層内に、そして半導体層の上に形成する方法が実現される。トレンチ(18,20,22)は、第1活性領域(24,26,28,30)に隣接して形成される。前記トレンチには、絶縁材料(32,34,36)が充填される。マスクパターン(48,50,52)を前記トレンチの中央部分の上に形成して、前記トレンチのうち、前記マスクパターンの第1側部と前記第1活性領域との間に位置する第1側部を露出させる。前記トレンチの前記第1側部を掘り込むエッチングを行なう工程によって、第1窪み(54,56,58,60)が前記トレンチに残る。第1エピタキシャル領域(62,66)を前記第1窪みに成長させて、前記第1活性領域を延長して前記第1窪みを包含することにより、第1拡幅活性領域を形成する。  (もっと読む)

(もっと読む)

異なる種類の表面を備えた基板及びそのような基板を得るための方法

より大きな密度の結晶欠陥を有する支持体と、前記支持体の前面の第1の領域上に配置された絶縁層と、前記絶縁層上に配置された表面層とを有する。追加層を、前記支持体の前記前面の少なくとも第2の領域に配置することができ、前記支持体の結晶欠陥を埋め込むのに十分な厚さを有する。基板は、前記支持体と前記絶縁層との間であって、前記支持体の前記前面の少なくとも前記第1の領域に渡って配置されたエピタキシャル層も含むことができる。また、前記表面層の前記第1の領域上にマスク層を形成するステップと、前記マスク層によって覆われていない前記第2の領域内の前記表面層及び前記絶縁層を除去するステップとによって基板を作製する方法を有する。前記追加層は、前記第2の領域に形成され、形成後に平坦化される。  (もっと読む)

(もっと読む)

41 - 60 / 150

[ Back to top ]