Fターム[5F152NN04]の内容

再結晶化技術 (53,633) | 基板材料(積層体を基板として扱う場合も含む) (4,266) | 半導体 (1,904) | 4族 (1,311) | Ge、SiGe (150)

Fターム[5F152NN04]に分類される特許

81 - 100 / 150

薄膜半導体、太陽電池および発光素子の製造方法

【課題】フレキシブルで、各種基板と一体化できる結晶性にすぐれたシリコン等の薄膜半導体を安価に製造することができ、これにより太陽電池を安価に製造することができるようにする。

【解決手段】半導体基体の表面を陽極酸化することにより多孔質度が異なる2層以上の層から構成される多孔質層12を形成し、多孔質層12の表面に太陽電池などの半導体膜13を成膜し、この半導体膜13を、多孔質層12を介して半導体基体から剥離する。陽極酸化する工程は、通電量の選定と、連続通電か間欠通電かの選定とにより、多孔質の異なる多孔質層のうち、比較的低多孔率の低多孔率層に対して、比較的高多孔率の高多孔率層の形成位置を制御する工程を含む。

(もっと読む)

高性能CMOS技術のための低コストの歪みSOI基板

【課題】エピタキシャル成長及びその後のウェハ接合処理ステップを回避するSSOI構造の製造方法を提供する。

【解決手段】歪み半導体オン・インシュレータ(SSOI)構造体を製造する。SOI基板上に歪み半導体領域を生成するために、歪み記憶技術が用いられる。半導体領域が歪んでいるので、歪み半導体領域上に形成されたトランジスタは、より高いキャリア移動度を有する。(i)薄いアモルファス化層を生成するためのイオン注入と、(ii)アモルファス化層上への高応力膜の堆積と、(iii)アモルファス化層を再結晶させるための熱アニールと、(iV)高応力膜の除去とを含む。再結晶化プロセスの間、SOI基板は応力を受けたので、最終的な半導体層も、応力を受ける。応力の量及び応力の極性(引張又は圧縮)は、高応力膜のタイプ及び厚さによって制御することができる。

(もっと読む)

歪み半導体基板の製造方法および歪みMOSFETの製造方法

【課題】歪み緩和バッファ層を設けることなく、結晶構造を有する半導体基板の表面に歪み半導体層を形成でき、したがって、簡単かつ低コストで歪み半導体基板を作製できる歪み半導体基板の製造方法を提供すること。

【解決手段】結晶構造を有する半導体基板の表面に絶縁膜を形成する(S1)。半導体基板の材料とは格子定数が異なる元素をその絶縁膜中にイオン注入する(S2)。その元素が絶縁膜中からはじき出されて半導体基板中に拡散して、その元素を要因とした歪みが半導体基板に生じるように熱処理を行う(S3)。

(もっと読む)

シリコンと炭素を含有するインサイチュリンドープエピタキシャル層の形成

【課題】 リンでドープされたシリコンと炭素を含有するエピタキシャル層を形成する方法を提供する。

【解決手段】 圧力は、堆積中100トール以上に維持される。方法は、置換型炭素を含む膜の形成を生じさせる。特定の実施形態は、半導体デバイス、例えば、金属酸化物半導体電界効果トランジスタ(MOSFET)デバイスにおけるエピタキシャル層の形成と処理に関する。

(もっと読む)

AlN系III族窒化物単結晶厚膜の作製方法

【課題】結晶品質に優れ、かつクラックのないAlN系III族窒化物単結晶厚膜を作製する方法を提供する。

【解決手段】エピタキシャル基板上に、HVPE法によってAlN系III族窒化物厚膜を得る場合に、通常の成長条件で厚膜層の形成を行う第1の工程と、その時点で形成されている厚膜層を第1の工程における厚膜層の形成温度T1以上の高温状態T2で保持することを主目的とする第2の工程とを適宜のタイミングで切り替えつつ繰り返し行うようにする。これにより、それぞれの第1の工程において厚膜層に内在する歪を第2の工程で逐次に緩和させつつ厚膜層を形成することができる。厚膜層の形成後に面内方向に作用する引張応力を、あらかじめ緩和させた状態の厚膜層を形成することができるので、厚膜層におけるクラックの発生を抑制することができる。

(もっと読む)

ハイブリッド・チャネル配向を有するCMOSデバイスおよびファセット形成エピタキシを用いてハイブリッド・チャネル配向を有するCMOSデバイを作製するための方法

【課題】別々の表面配向(すなわちハイブリッド表面配向)を有する半導体基板を提供する。

【解決手段】第一のデバイス領域2は、第一の等価結晶面の組の一つの方位に配向した実質的に平坦な表面16Aを有し、第二のデバイス領域は、第二の、別の等価結晶面の組の方位に配向した複数の交差する表面16Bを有する突起形半導体構造物18を含む。そのような半導体基板を用いて、半導体デバイス構造を形成することができる。詳しくは、第一のデバイス領域に第一の電界効果トランジスタ(FET)を形成することができ、第一のFETは、第一のデバイス領域の実質的に平坦な表面に沿って延在するチャネルを含む。第二のデバイス領域に第二の、相補FETを形成することができ、第二の、相補FETは、第二のデバイス領域にある突起形半導体構造物の複数の交差する表面に沿って延在するチャネルを含む。

(もっと読む)

半導体装置の製造方法

【課題】SBSI法において第1半導体層及び第2半導体層の膜形成の所要時間を短縮で

きるようにした半導体装置の製造方法を提供する。

【解決手段】単結晶の半導体基板1の表面領域2上にアモルファス又は多結晶構造の第1

半導体層11を形成する工程と、第1半導体層11上にアモルファス又は多結晶構造の第

2半導体層12を形成する工程と、第2半導体層12上から半導体基板1の表面領域2に

向けてSi又はArをイオン注入して、半導体基板1の表面領域2と、第1半導体層11

及び第2半導体層12をアモルファス化する工程と、イオン注入によるアモルファス化を

行った後で半導体基板1に熱処理を施して、半導体基板1の表面領域2と、第1半導体層

11及び第2半導体層12を単結晶化する工程と、を含む。

(もっと読む)

AlN系III族窒化物結晶の作製方法およびAlN系III族窒化物厚膜

【課題】比較的簡便な手法によって低転位のAlN系III族窒化物厚膜を得ることができる方法を提供する。

【解決手段】所定の基材上にMOCVD法によってAlN系III族窒化物成長下地層が形成されてなるエピタキシャル基板の上に、HVPE法によってAlN系III族窒化物厚膜をエピタキシャル形成する場合に、MOCVD法における加熱温度よりも高い温度で該エピタキシャル基板を加熱処理した上で、厚膜層の形成を行うようにすることで、厚膜層の低転位化を実現することができる。すなわち、HVPE法を用いた厚膜成長に先立って、加熱処理という比較的簡便な処理を施すだけで、HVPE法による成長に際して特別の構成を有する装置を用いたり、あるいは成長条件に特段の限定を加えたりしなくとも、低転位のAlN系III族窒化物からなる厚膜層を形成することができる。

(もっと読む)

選択的堆積

基板の表面上にシリコン含有材料をエピタキシャルに形成する方法は、プロセスチャンバー温度及び圧力の調整を通じてハロゲン含有ガスをエッチングガス及び担体ガスの両方として使用する。HClをハロゲン含有ガスとして使用するのが有益である。なぜなら、HClを担体ガスからエッチングガスへ変換することが、チャンバー圧力の調整で容易に遂行できるからである。 (もっと読む)

単結晶基板及びその製造方法

【課題】良質の単結晶基板及びその製造方法を提供する。

【解決手段】基板上に形成され、前記基板の一部が露出されるウィンドウを有する絶縁層と、前記ウィンドウに露出された前記基板の部分に形成される選択的結晶成長層と、前記絶縁層上で前記結晶成長層上に形成され、前記結晶成長層を結晶化シード層として用いて結晶化された単結晶層とを備える単結晶ウェーハである。これにより、ストッパによって結晶層の研磨深さを制御でき、従って良質の単結晶基板を製造できる。

(もっと読む)

層の緩和

【課題】電子工学、光学、又は光電子工学に応用するための、弾性的に歪みのない結晶材料製層を形成する方法の提供。

【解決手段】張力下で(又は圧縮して)弾性的に歪みのある第1の結晶層1と、圧縮して(又は張力下で)弾性的に歪みのある第2の結晶層2とを備え、前記第2の層が前記第1の層に隣接している構造体30を用いて、それらの2つの層間での拡散ステップを備え、それにより2つの層のそれぞれの組成物間の差がほぼ同じになるまで次第に低減され、その後、それらの2つの層が、全体として均質な組成物を有する、結晶材料製のただ単一の最終層を形成する。それらの2つの層のそれぞれの組成物と、厚さと、歪みの程度とを最初に選択することにより、拡散後に、全体として弾性的な歪みを示さない最終層を構成する材料が得られることを特徴とする。

(もっと読む)

半導体基板の製造方法及び半導体装置の製造方法

【課題】半導体基板に汚染物質が付着することを抑えトランジスタの特性を劣化させることなく製造することができる半導体基板の製造方法及び半導体装置の製造方法を提供する。

【解決手段】半導体基板41の製造方法は、シリコン基板11上におけるSOI素子形成領域13のみに、シリコンバッファ層18及びシリコンゲルマニウム層15が成長する条件でエピタキシャル成長させる。次に、シリコン基板11上の全面にシリコン層16を成長させる。そのあと、シリコンゲルマニウム層15に代えて埋め込み絶縁層31を埋め込む。これにより、引き続く工程において、シリコン基板11上に汚染の原因であるシリコンゲルマニウム層15が残ることを少なくすることができ、処理を行う炉の中にゲルマニウムが広がることを抑えることが可能となる。

(もっと読む)

基板、方法(1つまたは複数のSOI領域またはバルク半導体領域あるいはその両方を有するハイブリッド結晶表面配向基板)

【課題】単一スタック内で互いに結合された複数の絶縁体上半導体(SOI)ウエハを含む半導体デバイス用の基板を提供すること。

【解決手段】このスタックの遠位端は、第1表面配向を有するある厚さの第1半導体層を伴う第1のSOI領域を含む。この単一スタックの表面はさらに、非SOI領域、または少なくとも1つの第2のSOI領域、あるいはその両方を含み得る。この非SOI領域は、単一スタックのすべての絶縁体層を貫通して延び、かつ、第1シリコン層と異なる厚さを有するバルク・シリコンを含み得る。第2のSOI領域はそれぞれ、厚さが第1半導体層の厚さと異なるか、または表面配向が第1表面配向と異なるか、あるいはその両方とも異なる第2の半導体層を有する。そのため、この基板により、表面配向が異なるか、または厚さが異なるか、あるいはバルクまたはSOIと構造が異なるか、あるいはこれら異なるものが組み合わされた最適な基板領域上に異なるデバイスを形成することができる。

(もっと読む)

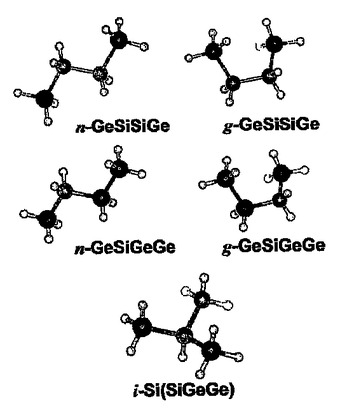

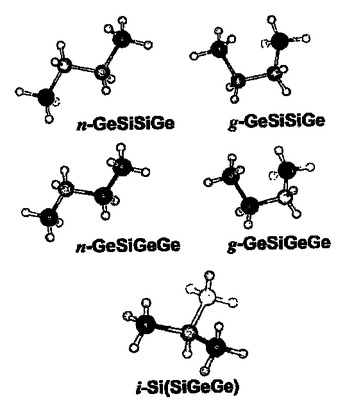

新規な水素化シリコンゲルマニウム、その製造法および使用法

本発明は、新規水素化シリコンゲルマニウム化合物、それらの合成法、それらの成膜法、およびそれらの新規化合物を用いて作製された半導体構造を提供する。これらの化合物は、式:(SiHn1)x(GeHn2)yによって定義される。式中、xは2,3または4であり;yは1,2または3であり;x+yは3,4または5であり;n1は、化合物中の各Si原子に関して独立に0,1,2または3であって原子価を満たし;n2は、化合物中の各Ge原子に関して独立に0,1,2または3であって原子価を満たし;但し、yが1のとき、n2は0ではなく;さらに、xが3、かつ、yが1のとき、n2は2または3であり;さらに、xが2、かつ、yが1のとき、n2は3である。  (もっと読む)

(もっと読む)

新規な水素化シリコンゲルマニウム、その製造法および使用法

本発明は、水素化シリコンゲルマニウム化合物、それらの合成法、それらの成膜法、およびそれらの化合物を用いて作製された半導体構造を提供する。これらの化合物は、式:SiHn1(GeHn2)yによって定義される。式中、yは2,3または4であり;n1は、0,1,2または3であって原子価を満たし;n2は、化合物中の各Ge原子に関して独立に0,1,2または3であって原子価を満たす。  (もっと読む)

(もっと読む)

歪み補償の準安定化合物ベースヘテロ接合バイポーラトランジスタ

歪み補償原子種を置換配列することにより、例えば、SiGe NPN HNTの電子装置(100)へ、その場で添加した歪み補償の準安定化合物基部(107)を電子装置(100)に擬似格子整合を増大し統一するための方法。本発明は歪みSiGe、MOSアプリケーションのSi、垂直薄膜トランジスタ(VTFT)、および様々なその他の電子装置型などの、その他の電子装置の歪み層にも適用する。例えば、GaAs、InP、およびAlGaAsの、SiGe以外の化合物半導体から形成される装置も本願に記載する有益な工程に適している。  (もっと読む)

(もっと読む)

薄膜半導体の製造方法

【課題】薄膜半導体を、低コストをもって容易、確実に得ることができるようにする。

【解決手段】半導体基体表面を、多孔質の表面層と、表面層下に形成され表面層に比して多孔率が大きい中間多孔率層と、中間多孔率層内部もしくは中間多孔率層の下層に形成され表面層および中間多孔率層に比して多孔率が大きい高多孔率層とを有するような多孔質層に変化させる工程と、多孔質層に半導体膜を形成する工程と、半導体膜を多孔質層を介して半導体基体から剥離する工程とを有する。

(もっと読む)

半導体ウェハの横方向に分断する方法およびオプトエレクトロニクス構成素子

半導体ウェハ(1)を横方向に分断する本発明の方法では、成長基板(2)を準備し、この成長基板(2)に半導体層列(3)をエピタキシ成長させる。ここではこの半導体層列には、分離層(4)として設けられた層と、成長の方向に見てこの分離層に続く少なくとも1つの機能半導体層(5)とが含まれている。引き続いてこの機能半導体層(5)を通して分離層(4)にイオン打ち込み、半導体層をこの分離層(4)に沿って分断し、上記の成長基板(2)を含む半導体ウェハ(1)の部分(1a)が切り離される。  (もっと読む)

(もっと読む)

III族窒化物の単結晶作製方法およびIII族窒化物単結晶層を含む積層体

【課題】簡便な方法によってAlNを含むAlN系III族窒化物の自立した状態の単結晶を作製する方法を提供する。

【解決手段】サファイア基材1の上にAlNの成長下地層2を形成した下地基板3の上に、第1中間層4を形成したうえで、さらにAlN単結晶層7をHVPE法によって形成し、積層体10を得る。ここで、第1中間層4は単結晶層7よりも分解温度の低い物質、好ましくはAlGaNなどのIII族窒化物により形成される。この積層体10を第1中間層4の分解温度よりも高く単結晶層7の分解温度よりも低い温度、例えば1650℃に加熱すると、第1中間層4が分解消失し、主としてAlN単結晶層7の部分からなる自立した状態のAlN系III族窒化物単結晶7aを得ることが出来る。

(もっと読む)

半導体ウエハの横方向分断のための方法及びオプトエレクトロニクス構成素子

本発明は、成長基板(2)と半導体層列(3)を含んでいる半導体ウエハの横方向切断のための方法に関している。この方法は成長基板(2)を設けるステップと、前記成長基板(2)において機能性半導体層(5)を含んだ半導体層列(3)をエピタキシャル成長させるステップと、マスキング領域(11)と非マスキング領域(12)の作成のために前記半導体層列(3)の部分領域にマスク層(10)を被着させるステップと、半導体ウエハ(1)におけるイオン打込み領域(13)作成のために非マスキング領域(12)を通してイオンを打ち込むステップと、前記イオン打込み領域(13)に沿って半導体ウエハ(1)を切断するステップとを有し、前記成長基板(2)又は少なくともその一部が半導体ウエハから分離されるようにしたことを特徴とする。  (もっと読む)

(もっと読む)

81 - 100 / 150

[ Back to top ]