Fターム[5F152NN06]の内容

再結晶化技術 (53,633) | 基板材料(積層体を基板として扱う場合も含む) (4,266) | 半導体 (1,904) | 3−5族 (475)

Fターム[5F152NN06]の下位に属するFターム

Fターム[5F152NN06]に分類される特許

21 - 40 / 60

SOI基板の作製方法及び該SOI基板を用いた半導体装置

【課題】結晶欠陥が存在する単結晶半導体基板を用いる場合においても優れた特性のSOI基板を提供することを目的の一とする。また、このようなSOI基板を用いた半導体装置を提供することを目的の一とする。

【解決手段】単結晶半導体基板の一表面に、エピタキシャル成長法による単結晶半導体層を形成し、単結晶半導体層に第1の熱酸化処理を施して第1の酸化膜を形成し、第1の酸化膜の表面に対してイオンを照射することにより、単結晶半導体層にイオンを導入し、第1の酸化膜を介して、単結晶半導体層とベース基板を貼り合わせ、熱処理を施すことにより、イオンが導入された領域において単結晶半導体層を分離して、ベース基板上に単結晶半導体層の一部を残存させ、ベース基板上に残存した単結晶半導体層に対してレーザ光を照射し、ベース基板上に残存した単結晶半導体層に第2の熱酸化処理を施して第2の酸化膜を形成した後、該第2の酸化膜を除去する。

(もっと読む)

III−V族化合物半導体層の製造方法、半導体光素子の製造方法、および半導体光素子

【課題】N原子を含むIII−V族化合物半導体層の結晶性をより向上させ得るIII−V族化合物半導体層の製造方法、半導体光素子の製造方法、および半導体光素子を提供する。

【解決手段】N原子を含むIII−V族化合物半導体層を製造する方法であって、III−V族化合物半導体層を構成する半導体結晶を半導体基板上に成長させてエピタキシャルウェハ1を形成する工程と、エピタキシャルウェハ1上におもり104を載せることで該半導体結晶に対して荷重を付与しつつ、該半導体結晶に対しその成長温度より高い温度で熱処理を行うアニール工程とを備える。

(もっと読む)

結晶基板およびGaN系結晶膜の製造方法

【課題】GaN系半導体デバイスの結晶成長用に適した、欠陥密度の小さい高品質のGaN系結晶膜連続膜を備えた結晶基板を得る。

【解決手段】GaN系半導体デバイス形成用基板として用いる結晶基板において、表面がC面のサファイア基板101と、該サファイア基板101上に形成されたGaNバッファ層102と、該GaNバッファ層102上に形成されたエピタキシャル成長GaN層103と、該エピタキシャル成長層103上に形成された、複数の開口部105を有するSiO2膜104と、該SiO2膜104の開口部105にGaN系化合物の選択再結晶化により形成された複数の島状GaN系結晶11と、該島状GaN系結晶11を核とするGaN系結晶の成長により形成されたGaN系結晶連続膜12とを備えた。

(もっと読む)

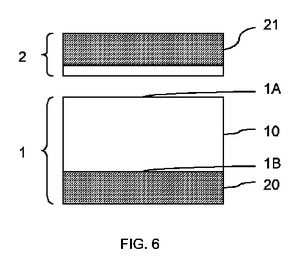

基板とその一方の面上に堆積させた層とを含む構造体の製造方法

本発明は、電子工学、光学、光電子工学または光起電力工学用の、基板(10)と前記基板(10)の一方の面上に材料を堆積させることにより形成された層(20)とを含む構造体(1)の製造方法に関し、この方法は、前記基板(10)の面(1B)が堆積した材料の層(20)により覆われ、前記基板の他の面(1A)が露出している前記構造体(1)を形成するように、−一方で前記基板(10)を、他方で残りの部分を画定する脆化区域を含む脆化された基板を形成する工程、−前記脆化された基板の2つの面のそれぞれの上に前記材料の層を堆積させる工程、−前記脆化された基板をへき開する工程を含むことを特徴とする。  (もっと読む)

(もっと読む)

SOI基板の作製方法および半導体装置の作製方法

【課題】SOI基板の作製時に発生する金属汚染の影響を抑える。

【解決手段】半導体基板に水素イオンを照射し損傷領域を形成した後、ベース基板と半導体基板を接合させる。加熱処理を行って、半導体基板を劈開させSOI基板を作製する。SOI基板の半導体層上に、Arなど第18族元素を含んだ半導体でなるゲッタリングサイト層を形成する。加熱処理を行って、半導体層中の金属元素をゲッタリングサイト層にゲッタリングさせる。エッチングにより、ゲッタリングサイト層を除去することで、半導体層の薄膜化を行う。

(もっと読む)

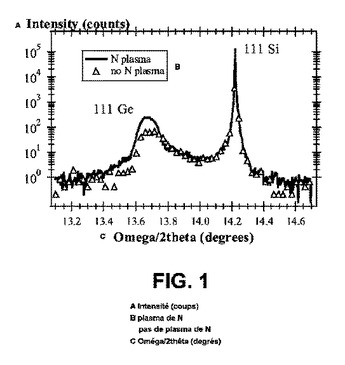

基板上に結晶ゲルマニウム層を形成する方法

本発明は、結晶表面を有する結晶ベース基板の上に結晶ゲルマニウム層を形成する方法を提供する。この方法は、ベース基板を洗浄して表面から汚染物および/または自然酸化物を除去する工程と、水素プラズマ、H2フラックス、またはGeH4の分解で得られる水素のような水素源および/またはN2、He、Ne、Ar、Kr、Xe、Rn、またはそれらの混合物のような非反応性ガス源にベース基板を露出させながら、ベース基板の表面上にアモルファスゲルマニウム層を形成する工程と、ベース基板をアニールしてアモルファスゲルマニウム層を結晶化して、結晶ゲルマニウム層を形成する工程と、を含む。また、この方法は、本発明の具体例にかかる方法を用いて光起電セルまたは光分解セルを形成する方法、またはCMOSデバイスを形成する方法、および本発明の具体例にかかる方法で形成した結晶ゲルマニウム層を含む基板を提供する。  (もっと読む)

(もっと読む)

化合物半導体の熱処理方法及びその装置

【課題】化合物半導体を用いた半導体デバイスにおける界面準位や結晶欠陥等を低減することが可能な化合物半導体の熱処理方法を提供する。

【解決手段】被処理体Wの表面に電磁波を照射することにより化合物半導体に関する熱処理を施すようにする。これにより、化合物半導体を用いた半導体デバイスにおける界面準位や結晶欠陥等を低減することができる。

(もっと読む)

窒化物半導体素子の製造方法

【課題】結晶性の良い窒化物半導体よりなる窒化物半導体基板を用い裏面に電極を形成した発光素子、受光素子等の窒化物半導体素子を提供する。

【解決手段】窒化物半導体と異なる材料よりなる基板の上に、窒化物半導体を100μm以上の膜厚で成長させ、前記基板を除去することによって得られた窒化物半導体基板であり、該窒化物半導体基板の表面の凹凸差が±1μm以下になるまで表面研磨した研磨面に成長される。好ましくは、前記表面の凹凸差が±0.5μm以下である。前記窒化物半導体基板はn型不純物がドープされている。

(もっと読む)

薄膜半導体、太陽電池および発光素子の製造方法

【課題】フレキシブルで、各種基板と一体化できる結晶性にすぐれたシリコン等の薄膜半導体を安価に製造することができ、これにより太陽電池を安価に製造することができるようにする。

【解決手段】半導体基体の表面を陽極酸化することにより多孔質度が異なる2層以上の層から構成される多孔質層12を形成し、多孔質層12の表面に太陽電池などの半導体膜13を成膜し、この半導体膜13を、多孔質層12を介して半導体基体から剥離する。陽極酸化する工程は、通電量の選定と、連続通電か間欠通電かの選定とにより、多孔質の異なる多孔質層のうち、比較的低多孔率の低多孔率層に対して、比較的高多孔率の高多孔率層の形成位置を制御する工程を含む。

(もっと読む)

高性能CMOS技術のための低コストの歪みSOI基板

【課題】エピタキシャル成長及びその後のウェハ接合処理ステップを回避するSSOI構造の製造方法を提供する。

【解決手段】歪み半導体オン・インシュレータ(SSOI)構造体を製造する。SOI基板上に歪み半導体領域を生成するために、歪み記憶技術が用いられる。半導体領域が歪んでいるので、歪み半導体領域上に形成されたトランジスタは、より高いキャリア移動度を有する。(i)薄いアモルファス化層を生成するためのイオン注入と、(ii)アモルファス化層上への高応力膜の堆積と、(iii)アモルファス化層を再結晶させるための熱アニールと、(iV)高応力膜の除去とを含む。再結晶化プロセスの間、SOI基板は応力を受けたので、最終的な半導体層も、応力を受ける。応力の量及び応力の極性(引張又は圧縮)は、高応力膜のタイプ及び厚さによって制御することができる。

(もっと読む)

半導体装置及び当該半導体装置の充電方法、並びに当該半導体装置を用いた通信システム

【課題】無線で充電可能なバッテリーが設けられた半導体装置に給電器を近接させない場合であっても、当該バッテリーの充電が可能な半導体装置を提供することを目的とする。

【解決手段】アンテナ回路と、前記アンテナ回路を介して無線通信を行う通信制御回路と、前記アンテナ回路を介して無線で供給される電力が充電されるバッテリーと、前記アンテナ回路を介して他の半導体装置のバッテリーに無線で電力の供給を行う発振回路とを設ける。

(もっと読む)

半導体ヘテロ構造

【課題】より小さな表面凹凸をもつ半導体ヘテロ構造を提供すること。

【解決手段】本発明は、第1の面内格子定数をもつ支持基板と、該支持基板上に形成されていて、上部に格子緩和状態おいて第2の面内格子定数をもつ緩衝構造と、および該緩衝構造上に形成された組成非傾斜層の多層積層とを備えた半導体ヘテロ構造に関するものである。表面凹凸の少ない、前記のタイプの半導体ヘテロ構造を提供することが本発明の目的である。前記の目的は、該組成非傾斜層が歪み層であり、かつ、該歪み層が前記第1および第2の格子定数の中間の第3の面内格子定数を格子緩和状態において有する半導体材料の、歪を有する平坦化層を少なくとも1つ含んで構成されることを特徴とする、前記のタイプのヘテロ構造によって達成される。

(もっと読む)

GaN薄膜貼り合わせ基板およびその製造方法、ならびにGaN系半導体デバイスおよびその製造方法

【課題】本発明は、半導体デバイスの製造コストを低減するために、GaNと化学組成の異なる異種基板にGaN薄膜が強固に貼り合わされているGaN薄膜貼り合わせ基板およびその製造方法、ならびに、GaN薄膜上に形成されている少なくとも1層のGaN系半導体層を含むGaN系半導体デバイスおよびその製造方法を提供する。

【解決手段】本GaN薄膜貼り合わせ基板1の製造方法は、GaNバルク結晶10にGaNと化学組成の異なる異種基板20を貼り合わせる工程と、異種基板20との界面から0.1μm以上100μm以下の距離を有する面10tでGaNバルク結晶10を分割して異種基板20上にGaN薄膜10aを形成する工程とを含み、GaNバルク結晶の貼り合わせ面の最大表面粗さRmaxが20μm以下であることを特徴とする。

(もっと読む)

ハイブリッド・チャネル配向を有するCMOSデバイスおよびファセット形成エピタキシを用いてハイブリッド・チャネル配向を有するCMOSデバイを作製するための方法

【課題】別々の表面配向(すなわちハイブリッド表面配向)を有する半導体基板を提供する。

【解決手段】第一のデバイス領域2は、第一の等価結晶面の組の一つの方位に配向した実質的に平坦な表面16Aを有し、第二のデバイス領域は、第二の、別の等価結晶面の組の方位に配向した複数の交差する表面16Bを有する突起形半導体構造物18を含む。そのような半導体基板を用いて、半導体デバイス構造を形成することができる。詳しくは、第一のデバイス領域に第一の電界効果トランジスタ(FET)を形成することができ、第一のFETは、第一のデバイス領域の実質的に平坦な表面に沿って延在するチャネルを含む。第二のデバイス領域に第二の、相補FETを形成することができ、第二の、相補FETは、第二のデバイス領域にある突起形半導体構造物の複数の交差する表面に沿って延在するチャネルを含む。

(もっと読む)

半導体装置の製造方法

【課題】SBSI法において第1半導体層及び第2半導体層の膜形成の所要時間を短縮で

きるようにした半導体装置の製造方法を提供する。

【解決手段】単結晶の半導体基板1の表面領域2上にアモルファス又は多結晶構造の第1

半導体層11を形成する工程と、第1半導体層11上にアモルファス又は多結晶構造の第

2半導体層12を形成する工程と、第2半導体層12上から半導体基板1の表面領域2に

向けてSi又はArをイオン注入して、半導体基板1の表面領域2と、第1半導体層11

及び第2半導体層12をアモルファス化する工程と、イオン注入によるアモルファス化を

行った後で半導体基板1に熱処理を施して、半導体基板1の表面領域2と、第1半導体層

11及び第2半導体層12を単結晶化する工程と、を含む。

(もっと読む)

半導体基板の製造方法

【課題】窒化物系の半導体デバイスを低コストで製造可能な半導体基板を提供すること。

【解決手段】第1の基板20上に設けられた窒化物系半導体結晶10に水素イオンを注入して、低転位密度領域12内に水素イオン注入層13を形成する。窒化物系半導体結晶10と第2の基板30とを貼り合わせ、この状態で外部から衝撃を付与して水素イオン注入層13に沿って窒化物系半導体結晶10の低転位密度領域12を分離して低転位密度領域12の表層部12bを第2の基板30上に転写(剥離)する。このとき、低転位密度領域12の下層部12aは第2の基板30上には転写されずに第1の基板20上に残存することとなる。低転位密度領域12の表層部12bが転写された第2の基板30は本発明の製造方法で得られる半導体基板とされ、低転位密度領域12の下層部12aが残存した状態の第1の基板20は再度エピタキシャル成長用の基板として利用される。

(もっと読む)

半導体基板の製造方法及び半導体装置の製造方法

【課題】半導体基板に汚染物質が付着することを抑えトランジスタの特性を劣化させることなく製造することができる半導体基板の製造方法及び半導体装置の製造方法を提供する。

【解決手段】半導体基板41の製造方法は、シリコン基板11上におけるSOI素子形成領域13のみに、シリコンバッファ層18及びシリコンゲルマニウム層15が成長する条件でエピタキシャル成長させる。次に、シリコン基板11上の全面にシリコン層16を成長させる。そのあと、シリコンゲルマニウム層15に代えて埋め込み絶縁層31を埋め込む。これにより、引き続く工程において、シリコン基板11上に汚染の原因であるシリコンゲルマニウム層15が残ることを少なくすることができ、処理を行う炉の中にゲルマニウムが広がることを抑えることが可能となる。

(もっと読む)

エピタキシャルウェーハの製造方法

【課題】 GaP基板上に結晶性の良好なAlGaInP系DH構造を有するエピタキシャルウェーハと当該ウェーハを使用した高輝度のLEDを提供すること。

【解決手段】 GaP化合物半導体基板上に、GaPバッファ層、AlGaInP第一段下部クラッド層、能動層としてAlGaInP下部クラッド層、AlGaInP活性層、AlGaInP上部クラッド層のダブルヘテロ構造を有するエピタキシャルウェーハの製造方法において、前記GaP化合物半導体基板上に前記GaPバッファ層を成長させ、その上に前記AlGaInP第一段下部クラッド層を成長させた後に、この前記AlGaInP第一段下部クラッド層表面をポリッシュし、その後、前記AlGaInP下部クラッド層、前記GaInP活性層、前記AlGaInP上部クラッド層のエピタキシャル成長を行う。

(もっと読む)

薄膜半導体の製造方法

【課題】薄膜半導体を、低コストをもって容易、確実に得ることができるようにする。

【解決手段】半導体基体表面を、多孔質の表面層と、表面層下に形成され表面層に比して多孔率が大きい中間多孔率層と、中間多孔率層内部もしくは中間多孔率層の下層に形成され表面層および中間多孔率層に比して多孔率が大きい高多孔率層とを有するような多孔質層に変化させる工程と、多孔質層に半導体膜を形成する工程と、半導体膜を多孔質層を介して半導体基体から剥離する工程とを有する。

(もっと読む)

歪み超格子とその上の応力層とを含む半導体デバイス、及びその製造方法

半導体デバイスは、積層された複数の層群を有する歪み超格子層(325)、及び歪み超格子層の上方の応力層を含んでいる。歪み超格子層の各層群は、ベース半導体部分を画成する積層された複数のベース半導体モノレイヤーと、隣接し合うベース半導体部分の結晶格子内に拘束された少なくとも1つの非半導体モノレイヤーとを含んでいる。  (もっと読む)

(もっと読む)

21 - 40 / 60

[ Back to top ]