Fターム[5F152NN08]の内容

再結晶化技術 (53,633) | 基板材料(積層体を基板として扱う場合も含む) (4,266) | 半導体 (1,904) | 3−5族 (475) | InP (69)

Fターム[5F152NN08]に分類される特許

1 - 20 / 69

複合基板の製造方法

【課題】結晶成長用基板に形成した半導体結晶層を転写先基板に転写する場合の犠牲層のエッチング速度を高める。

【解決手段】半導体結晶層形成基板の上に犠牲層および半導体結晶層を順に形成するステップと、犠牲層の一部が露出するように半導体結晶層をエッチングし、半導体結晶層を複数の分割体に分割するステップと、転写先基板に接することとなる半導体結晶層形成基板側の第1表面と、第1表面に接することとなる転写先基板側の第2表面と、が向かい合うように、半導体結晶層形成基板と転写先基板とを貼り合わせるステップと、半導体結晶層形成基板および転写先基板をエッチング液に浸漬して犠牲層をエッチングし、半導体結晶層を転写先基板側に残した状態で、転写先基板と半導体結晶層形成基板とを分離するステップと、を有し、前記半導体結晶層が、GexSi1−x(0<x≦1)からなる、複合基板の製造方法を提供する。

(もっと読む)

複合基板の製造方法および複合基板

【課題】結晶成長用基板に形成した半導体結晶層を転写先基板に転写する場合の犠牲層のエッチング速度を高める。

【解決手段】半導体結晶層形成基板の上に犠牲層および半導体結晶層を順に形成し、転写先基板に接することとなる前記半導体結晶層形成基板の第1表面と、前記第1表面に接することとなる前記転写先基板の第2表面と、が向かい合うように、前記半導体結晶層形成基板と前記転写先基板とを貼り合わせ、前記半導体結晶層形成基板および前記転写先基板の全部または一部をエッチング液に浸漬して前記犠牲層をエッチングし、前記半導体結晶層を前記転写先基板側に残した状態で、前記転写先基板と前記半導体結晶層形成基板とを分離する。ここで、前記転写先基板が、非可撓性基板と有機物層とを有し、前記有機物層の表面が、前記第2表面であるものとする。

(もっと読む)

半導体デバイス、半導体基板、半導体基板の製造方法および半導体デバイスの製造方法

【課題】単一基板上にソース・ドレインを同一工程で同時形成したIII−V族半導体のnMISFETおよびIV族半導体のpMISFETのソース・ドレイン領域抵抗または接触抵抗を小さくする。

【解決手段】第1半導体結晶層に形成された第1チャネル型の第1MISFETの第1ソースおよび第1ドレインと、第2半導体結晶層に形成された第2チャネル型の第2MISFETの第2ソースおよび第2ドレインが、同一の導電性物質からなり、当該導電性物質の仕事関数ΦMが、数1および数2の少なくとも一方の関係を満たす。

(数1) φ1<ΦM<φ2+Eg2

(数2) |ΦM−φ1|≦0.1eV、かつ、|(φ2+Eg2)−ΦM|≦0.1eV

ただし、φ1は、N型半導体結晶層の電子親和力、φ2およびEg2は、P型半導体結晶層の電子親和力および禁制帯幅。

(もっと読む)

半導体基板の製造方法および半導体基板

【課題】高性能なIII−V族MISFETの実現を可能にする、より効果的なIII−V族化合物半導体表面のパッシベーション技術を提供する。

【解決手段】エピタキシャル成長により化合物半導体層をベース基板上に形成するステップと、前記化合物半導体層の表面をセレン化合物を含む洗浄液で洗浄するステップと、前記化合物半導体層の上に絶縁層を形成するステップと、を有する半導体基板の製造方法を提供する。前記セレン化合物として、セレン酸化物が挙げられる。前記セレン酸化物として、H2SeO3が挙げられる。前記洗浄液が、水、アンモニアおよびエタノールからなる群から選択された1以上の物質をさらに含んでもよい。前記化合物半導体層の表面がInxGa1−xAs(0≦x≦1)からなる場合、前記絶縁層がAl2O3からなるものであることが好ましく、Al2O3は、ALD法により形成されることが好ましい。

(もっと読む)

キャップ層および埋込みゲートを有する窒化物ベースのトランジスタを作製する方法

【課題】埋込み部を形成する際のエッチングにより埋込みゲートが損傷をきたし、ゲート領域劣化が生じ得る。

【解決手段】ショットキーコンタクトなどのゲートコンタクトを形成する前にゲート埋込み部のアニーリングを行うことにより、ゲートリークが低減され、かつ/またはトランジスタなどの半導体デバイス内に高品質のゲートコンタクトを提供することができる。アニーリング中に封入層を使用することで、トランジスタのゲート埋込み部内の半導体への損傷がさらに低減される。アニーリングを、例えばデバイスのオーミックコンタクトのアニーリングによって提供することができる。

(もっと読む)

半導体デバイス、その製造方法及び集積回路

【課題】電極領域の抵抗を従来よりも一段と低減させることができる半導体デバイス、その製造方法及び集積回路を提供する。

【解決手段】III−V族化合物半導体層4上にニッケル層17を形成し、RTA処理により加熱することで、ニッケルIII−V族合金(Ni-InxGa1-xAsyP1-y合金)からなるソース領域5及びドレイン領域6が形成される。これにより、MOSFET1では、III−V族化合物半導体層4に対して単に不純物をインプラテーションで注入して形成された従来のソース領域及びドレイン領域の寄生抵抗に比べて、ソース領域5及びドレイン領域6の寄生抵抗を一段と低減させることができる。

(もっと読む)

化合物半導体基板、エピタキシャル基板、化合物半導体基板の製造方法及びエピタキシャル基板の製造方法

【課題】 表面において所望の電気特性を有する化合物半導体基板、エピタキシャル基板、化合物半導体基板の製造方法及びエピタキシャル基板の製造方法を提供する。

【解決手段】 化合物半導体基板10aは、p型の化合物半導体からなる基板12と、基板12の表面12aに結合しておりp型の不純物原子を含む物質14とを備える。

(もっと読む)

半導体薄膜基板および半導体薄膜基板を用いた半導体装置の作製方法

【課題】一層の半導体層から膜厚の異なる半導体層を有する半導体薄膜基板を提供することを目的の一とする。または、半導体薄膜基板を適用した半導体装置を提供することを目的の一とする。

【解決手段】基板上に半導体層を形成し、半導体層を加工して第1の島状半導体層および第2の島状半導体層を形成し、第1の島状半導体層にレーザー照射を行うことにより第1の島状半導体層を溶融させ、第1の島状半導体層から第2の島状半導体層より膜厚が厚い第3の島状半導体層を形成する、半導体薄膜基板の作製方法である。

(もっと読む)

半導体基板、半導体基板の製造方法、および電磁波発生装置

【課題】複数の異なる周波数を出力する半導体基板を提供する。

【解決手段】p型半導体またはn型半導体を含む第1の不純物半導体と、第1の不純物半導体に接する複数の空乏領域を有する空乏化半導体とを備え、複数の空乏領域のそれぞれは、第1の不純物半導体との第1界面と、第1界面と対向する表面とを有し、複数の空乏領域のそれぞれは、第1界面に垂直な方向における第1界面と表面との平均距離および組成の少なくとも一つが異なる半導体基板を提供する。

(もっと読む)

半導体複合体構造を形成する方法

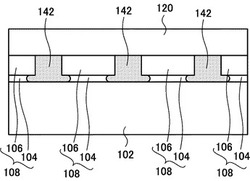

【課題】 パターン付けされたシリコン・オン・インシュレータ(SOI)/シリコン・オン・ナッシング(SON)複合構造体を多孔性Si技術によって形成すること。

【解決手段】 パターン付けされたSOI/SON複合構造体及びその形成方法を提供する。SOI/SON複合構造体においては、パターン付けされたSOI/SON構造体が、Siオーバーレイヤと半導体基板の間に挟まれる。パターン付けされたSOI/SON複合構造体を形成する方法は、SOI及びSON構造が共に形成される共有加工処理ステップを含む。本発明はまた、埋没導電/SON構造体を含む複合構造体の形成方法、及び、埋没ボイド平面だけを有する複合構造体の形成方法を提供する。

(もっと読む)

半導体薄膜の形成方法

【課題】所望の特性が得られる状態で、InPからなる基板の表面に付着した汚染物としての不純物による問題が解消できるようにする。

【解決手段】まず、Feが添加された半絶縁性のInPからなる基板101の上に、炭素(C)を添加したGaAsSbからなる半導体層(第1半導体層)102を形成する。半導体層102は、Cの添加によりp型とされている。また、添加されるCは、基板101の表面に付着している不純物とは逆の電気的特性を有する不純物となる。なお、半導体層102は、InおよびGaの少なくとも一方とAs,Sbとを少なくとも備える化合物半導体から構成されていればよく、AlzInxGa1-x-zAs1-ySby(0≦x≦0.2,0.3≦y≦1,0≦z≦1,0≦x+z≦1)から構成されていればよい。

(もっと読む)

歪み補償半導体構造および歪み補償半導体構造を製作する方法

【課題】歪みの程度がGaNの割れの閾値を上回るならば、GaNが割れ、GaNの半導体デバイスへの使用を受容できないものにする可能性がある。

【解決手段】この半導体構造は、第1の面内無歪み格子定数を有する基板と、基板上に設けられ、第1の面内無歪み格子定数とは異なる第2の面内無歪み格子定数を有する、第1の半導体材料を含む第1の層と、基板と第1の層の間に配置され、第2の半導体材料を含む可変不整合層とを含む半導体構造、およびこの半導体構造の製作方法が提供される。可変不整合層は、第1の層を基板上に直接成長させる場合に生じる応力を下回る程度にまで第1の層の応力が低減されるように構成される。可変不整合層は、第1の層の無歪み格子定数と実質的に整合する面内歪み格子定数を有する層であってもよい。

(もっと読む)

イオン注入III族窒化物半導体基板ならびにIII族窒化物半導体層接合基板およびIII族窒化物半導体デバイスの製造方法

【課題】反りが小さいイオン注入III族窒化物半導体基板、ならびにかかる基板を用いたIII族窒化物半導体層接合基板およびIII族窒化物半導体デバイスの製造方法を提供する。

【解決手段】本イオン注入III族窒化物半導体基板2は、両主面20a,20b側に両主面20a,20bからそれぞれ所定の深さDa,Dbで形成されているイオン注入領域20ia,20ibを含む。

(もっと読む)

SOI基板の作製方法及び半導体装置の作製方法

【課題】平坦性を確保しつつ、結晶性の高い半導体膜を有する、SOI基板の作製方法を提供することを、目的の一とする。

【解決手段】分離により絶縁膜上に単結晶の半導体膜を形成した後、該半導体膜の表面に存在する自然酸化膜を除去し、半導体膜に対して第1のレーザ光の照射を行う。第1のレーザ光の照射は、希ガス雰囲気下、窒素雰囲気下または減圧雰囲気下にて、半導体膜の任意の一点におけるレーザ光のショット数を7以上、より好ましくは10以上100以下とする。そして、第1のレーザ光の照射を行った後、半導体膜に対して第2のレーザ光の照射を行う。第2のレーザ光の照射は、希ガス雰囲気下、窒素雰囲気下または減圧雰囲気下にて、半導体膜の任意の一点におけるレーザ光のショット数を0より大きく2以下とする。

(もっと読む)

半導体装置、半導体装置の製造方法

【課題】 p型不純物が隣接する半導体結晶層中へ拡散することを抑え、ひいては良好で安定した特性を持つ半導体装置を提供する。

【解決手段】 P−InP基板401と、P−InP基板401に格子整合し、かつ、p型の不純物が注入されたp−ZnドープInPバッファ層402と、p−ZnドープInPバッファ層402よりも上層にあって、P−InP基板401に格子整合し、かつ、p型不純物、n型不純物のいずれか一方を含むn−SiドープInPクラッド層404、n−SiドープInGaAsキャップ層405と、を備え、n−SiドープInPクラッド層404、n−SiドープInGaAsキャップ層405に、Sbを含ませる。

(もっと読む)

半導体基板の製造方法

【課題】選択エッチング層のエッチング時の自然酸化による影響で化合物半導体層の損傷、結晶の転移が発生せず、信頼性の高い半導体基板の製造方法を提供する。

【解決手段】化合物半導体基板8上に、選択エッチング層3、応力緩和層9および応力緩和層9より大きいヤング率を有するIII−V族化合物半導体から成る化合物半導体層4をエピタキシャル成長法により順次積層させる積層工程と、選択エッチング層3、応力緩和層9および化合物半導体層4を所定パターンとなるようにエッチング除去するエッチング工程と、Si基板5の主面に化合物半導体層4の上面を直接接合法により接合させて、選択エッチング層3、応力緩和層9および化合物半導体層4が積層された化合物半導体基板8を貼りあわせる接合工程と、前記エッチング工程で残った選択エッチング層3をさらにエッチング除去することにより、Si基板5と化合物半導体基板8とを分離する分離工程とを含む。

(もっと読む)

半導体薄膜素子の製造方法並びに半導体ウエハ、及び、半導体薄膜素子

【課題】Si結晶層上に半導体素子を備えたSi以外の半導体単結晶層を備えた半導体薄膜素子の製造方法並びに半導体ウエハ、及び、半導体薄膜素子を提供する。

【解決手段】Si(111)基板(第1の基板)101の表面にバッファ層102と半導体単結晶層103とを順次形成する第1の工程と、半導体単結晶層101aとバッファ層102aとSi(111)基板の所定の厚さ部分102bとを含む分離島150を形成する第2の工程と、分離島の表面を覆う被覆層200を形成する第3の工程と、被覆層をマスクに前記Si(111)基板をSi(111)面に沿ってエッチングして剥離する第4の工程と、分離島の剥離面を別の基板(第2の基板)201の表面に接合する第5の工程とを備える。

(もっと読む)

発光サイリスタ、発光素子アレイ、発光装置および画像形成装置

【課題】 ベース層のキャリア濃度および厚み寸法を大きく設定することなく、発光強度に対する電流増幅率βの影響を抑制することのできる発光サイリスタ、発光素子アレイ、発光装置および画像形成装置を提供することである。

【解決手段】 発光サイリスタは、基板上に第1半導体層、第1半導体層と反対導電型の第2半導体層、第1半導体層と同じ導電型の第3半導体層、および第1半導体層と反対導電型の第4半導体層がこの順に積層されており、第3半導体層のバンドギャップは、第2半導体層のバンドギャップと略同一、かつ、第1および第4半導体層のバンドギャップより狭幅であり、第3半導体層は、基板側の第1領域と基板と反対側の第2領域とからなり、かつ、第1領域の不純物濃度は1×1016(cm−3)未満である。

(もっと読む)

電界効果トランジスタ

【課題】歪みチャネルを用いた場合のリーク電流を低減することができ、不良の発生を抑制して歩留まりの向上をはかる。

【解決手段】半導体基板10上に設けられた、基板10とは格子定数の異なる合金半導体からなる下地層20と、下地層20上に設けられた、下地層20とは格子定数が異なり、チャネル長方向及びチャネル幅方向の一方に引っ張り応力、他方に圧縮応力が付与されたチャネル半導体層30と、チャネル半導体層30を挟むように下地層20上に設けられたソース・ドレイン領域60,70と、チャネル半導体層30上にゲート絶縁膜40を介して設けられたゲート電極50とを備えた電界効果トランジスタであって、下地層20は、ソース・ドレイン領域60,70の下部に形成される空乏層61,71が下地層20内に収まる厚さよりも厚く形成され、且つ熱平衡臨界膜厚よりも薄く形成されている。

(もっと読む)

半導体装置、半導体装置の製造方法、半導体基板、および半導体基板の製造方法

【課題】化合物半導体と絶縁性材料との界面に形成される界面準位が低減した半導体装置を提供する。

【解決手段】閃亜鉛鉱型の結晶構造を有する3−5族化合物半導体と、3−5族化合物半導体の(111)面、(111)面と等価な面、または、(111)面もしくは(111)面と等価な面から傾いたオフ角を有する面に接する絶縁性材料と、絶縁性材料に接し、金属伝導性材料を含むMIS型電極とを備える半導体装置を提供する。

(もっと読む)

1 - 20 / 69

[ Back to top ]