Fターム[5F152NP23]の内容

再結晶化技術 (53,633) | 基板と活性層の間の層(バッファ層、マスク等)の材料 (2,042) | 結晶性 (107) | 非晶質 (46)

Fターム[5F152NP23]に分類される特許

1 - 20 / 46

シリコン基板、これを採用したエピ構造体及びシリコン基板の製造方法

III族窒化物半導体デバイスの製造方法

半導体装置、半導体基板、半導体装置の製造方法、及び半導体基板の製造方法

【課題】エピタキシャル層に残存する転位の数を少なくする。

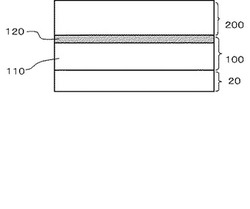

【解決手段】第2エピタキシャル層200は、第1エピタキシャル層100上にエピタキシャル成長している。第1エピタキシャル層100は、エピタキシャル成長層110及び欠陥層120を有している。欠陥層120は、エピタキシャル成長層110の上、かつ、第1エピタキシャル層100の表層に位置している。欠陥層120の欠陥密度は、5×1017cm−2以上である。欠陥層120を突き抜けた欠陥は、第2エピタキシャル層200の内部でループを形成している。

(もっと読む)

半導体結晶基板、半導体結晶基板の製造方法、半導体装置の製造方法、電源装置及び増幅器

【課題】基板の外周部においてクラックの発生が抑制される半導体結晶基板を提供する。

【解決手段】半導体結晶基板110と、基板110の表面に窒化物により形成された保護層120と、を有し、保護層120は、基板110の外周部となる周辺領域120aはアモルファス状態であり、基板110の周辺領域よりも内側の内部領域120bは結晶化している。

(もっと読む)

シリコン−オン−インシュレーター構造及びバルク基板に対するSiGeの堆積

【課題】欠陥を最小限としながら、SiGe−オン−インシュレーター構造を製造するため及びシリコン上に歪み緩和SiGe層を製造するための方法を提供する。

【解決手段】アモルファスSiGe層600が、トリシラン及びGeH4からCVDによって、ドーパントの1以下のモノレイヤー上に堆積される。これらのアモルファスSiGe層600は、融解または固相エピタキシー(SPE)プロセスによってシリコン上に再結晶される。融解プロセスは、好ましくは、全体のゲルマニウム含量を希釈するようなゲルマニウムの拡散も引き起こし、そして絶縁体の上層のシリコン500を実質的に消費する。SPEプロセスは、下地のシリコン500中へのゲルマニウムの拡散を用いてまたは用いずに実際され得、従って、SOI及び従来の半導体基板に適用可能である。

(もっと読む)

基板製造方法及び該方法によって得られた基板

【課題】活性材料要素をしじたいに移し替えるコストを低減する。

【解決手段】第1の材料から成る活性要素の表面上における支持体2への接合対象部位に非晶質材料6を蒸着する工程を備え、第2の材料が第1の材料よりも希少ではないことを特徴とする。更に、特に光学、電子工学又は光電子工学用の基板を製造する際に第1の材料から成る活性要素8を第2の材料から成る支持体2の表面に接合する操作を行う基板製造方法にも関する。この方法は、活性要素8又は支持体2が少なくともその表面上の接合対象部位に多結晶材料を含み、接合に先立ち、この多結晶材料を含む表面上に非晶質材料6の層を形成することを特徴とする。

(もっと読む)

半導体積層体とこれを含むHFETおよびそれらの製造方法

【課題】半導体積層体に含まれるチャネル層下の化合物半導体層を不純物ドーピングでp型化することなく、その半導体積層体を含むHFETのリーク電流の低減や耐電圧の向上などを可能とする。

【解決手段】半導体積層体は、基板(11)上において順次堆積された第1、第2および第3の化合物半導体層(13、14、15)を少なくとも含み、その第1化合物半導体層(13)の少なくとも部分的層(16)は非晶質に改質されており、第2化合物半導体層(14)は第1化合物半導体層(13)に比べて小さなバンドギャップを有して光吸収層として作用し得る。

(もっと読む)

微結晶シリコン膜の作製方法および薄膜トランジスタの作製方法

【課題】絶縁膜と微結晶シリコン膜との密着性を向上させた微結晶シリコン膜の作製方法を提供する。

【解決手段】絶縁膜55上に、後のプラズマ酸化等により完全に酸化される高さ(例えば0nmより大きく5nm以下)の微結晶シリコン粒、または後のプラズマ酸化等により完全に酸化される膜厚(例えば0nmより大きく5nm以下)の微結晶シリコン膜もしくはアモルファスシリコン膜を形成し、前記微結晶シリコン粒または前記微結晶シリコン膜もしくはアモルファスシリコン膜に酸素を含むプラズマ処理またはプラズマ酸化を施すことにより、前記絶縁膜上に酸化シリコン粒57aまたは酸化シリコン膜を形成し、前記酸化シリコン粒または前記酸化シリコン膜の上に微結晶シリコン膜59を形成する微結晶シリコン膜の作製方法である。

(もっと読む)

炭化珪素基板、半導体装置、炭化珪素基板の製造方法

【課題】炭化珪素基板を用いた半導体装置の製造コストの低減を実現可能な炭化珪素基板、半導体装置および炭化珪素基板の製造方法を提供する。

【解決手段】炭化珪素基板1は、炭化珪素からなるベース層10と、単結晶炭化珪素からなり、ベース層10上に配置され、ベース層10よりも不可避不純物の濃度が低いSiC層20と、炭化珪素からなり、ベース層10の、SiC層20とは反対側の主面10D上に形成され、ベース層10よりも不可避不純物の濃度が低い被覆層90とを備えている。

(もっと読む)

ボンディング層が消滅する間接ボンディング

【課題】支持基板に直接に接着することができない半導体材料によるSeOI構造を形成する方法を提供する。

【解決手段】下部層1及び上部層2を備える半導体ドナー基板が使用され、上部層2の材料の元素の拡散を受け入れる材料のボンディング層3を上部層2上に形成する工程と、そのボンディング接着を確実に行うためにボンディング層3を洗浄する工程と、あらかじめ上部層2上に形成され、そして、洗浄されたボンディング層3の側から、支持基板20に対してドナー基板を接着する工程と、この上部層2から元素をボンディング層3中に拡散して、このボンディング層及び上部層中の上記元素の濃度を均一化し、均一な薄層を支持基板20の表面上に形成する工程とを備える。

(もっと読む)

半導体基板、半導体基板の製造方法、電子デバイス、および電子デバイスの製造方法

【課題】結晶薄膜を有する半導体基板の設計および上記結晶薄膜の膜質および膜厚の制御を容易にできる半導体基板を提供する。

【解決手段】ベース基板と、ベース基板上に、一体にまたは分離して設けられ、化合物半導体の結晶成長を阻害する阻害層とを備え、阻害層は、ベース基板まで阻害層を貫通する複数の開口を有する複数の第1開口領域を有し、複数の第1開口領域のそれぞれは、内部に同一の配置で設けられた複数の第1開口を含み、複数の第1開口の一部は、電子素子が形成されるべき第1化合物半導体が設けられている第1素子形成開口であり、複数の第1開口の他の一部は、電子素子が形成されない第1ダミー開口である半導体基板を提供する。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】基板と当該基板に形成される化合物半導体とを電気的に絶縁しつつ、結晶性に優れた化合物半導体を備えた半導体基板を提供する。

【解決手段】ベース基板と、ベース基板上に設けられたシード結晶と、シード結晶の上方に設けられた化合物半導体と、シード結晶と化合物半導体との間に設けられ、シード結晶よりも大きな抵抗率を有する高抵抗層とを備え、シード結晶と化合物半導体とが格子整合または擬格子整合している半導体基板を提供する。

(もっと読む)

積層体、自立基板製造用基板、自立基板およびこれらの製造方法

【課題】Al系III族窒化物単結晶自立基板を製造するためのベース基板として好適に使用できる、結晶レベルでの歪みが低減されており、クラックおよび反りの発生が抑制された自立基板製造用基板を提供する。

【解決手段】不活性ガス中1000℃において分解しない無機物質であって、1000℃以上1600℃以下で還元性ガスと接触することにより分解して揮発性物質を生成する無機物質の単結晶からなるベース基板、ベース基板上に形成された、単結晶Al系III族窒化物、または単結晶Al系III族窒化物と非晶質Al系III族窒化物との混合物からなる厚さ3nm以上200nm以下のAl系III族窒化物薄膜層、Al系III族窒化物薄膜層上に形成された、Al系III族窒化物薄膜層の厚さの100倍以上の厚さを備えたIII族窒化物非単結晶層、を備えて構成される積層体とし、ベース基板とAl系III族窒化物薄膜層との界面に複数の空隙を設ける。

(もっと読む)

半導体装置とその製造方法

【課題】格子定数が異なる複数種類の半導体素子を同一の基板上に混載することが可能な半導体装置とその製造方法。

【解決手段】少なくとも第1、第2のSi1-xGex(0≦x≦1)層14a,14b,14cが絶縁膜13上に形成されている。第1、第2のSi1-xGex(0≦x≦1)層上に対応して少なくとも第1、第2の材料層15,16,17が形成されている。第1、第2のSi1-xGex(0≦x≦1)層層14a,14b,14cの格子定数はその上の第1、第2の材料層15,16,17の格子定数に整合されている。

(もっと読む)

半導体基板、半導体基板の製造方法および電子デバイス

【課題】安価な、また、放熱特性に優れたSi基板を用いて、良質なGaAs系の結晶薄膜を得る。

【解決手段】Siの基板と、基板の上に形成され、結晶成長を阻害する阻害層とを備え、阻害層は、基板の一部を覆う被覆領域と、被覆領域の内部に基板を覆わない開口領域とを有し、さらに開口領域に結晶成長されたGe層と、Ge層の上に結晶成長され、Pを含む3−5族化合物半導体層からなるバッファ層と、バッファ層の上に結晶成長された機能層と、を備える半導体基板を提供する。当該半導体基板において、Ge層は、結晶欠陥が移動できる温度および時間でアニールされることにより形成されてよい。

(もっと読む)

分子接合を含むマイクロエレクトロニクス構造体の製造方法

シリコンと異なる第1の材料を表面として有する第1の構造体(1)を作製することと、この第1の構造体の表面に、IBS(イオンビームスパッタリング)によって、第2の材料からなり、自由表面を有する厚さ1ミクロン未満の少なくとも1層の被膜層(3)を形成することと、この自由表面を第2の構造体(4)の1つの面に分子接合することを含み、被膜層が第1および第2の構造体の接合層を構成する、マイクロエレクトロニクス構造体の製造方法。  (もっと読む)

(もっと読む)

SiGeオンインシュレータ基板材料

【課題】 向上された緩和、かなり低い欠陥密度、および改善された表面品質を有する

緩和されたSiGeオンインシュレータ基板を形成する方法を提供すること。

【解決手段】 方法が、第1の単結晶Si層の表面上にSiGe合金層を形成するステ

ップを含む。第1の単結晶Si層は、Ge拡散に対する耐性がある下の障壁層との界面を

有する。次に、界面での、または界面付近での機械的な分断を可能にする欠陥を形成する

ことができるイオンが構造内に注入され、その後、注入されたイオンを含む構造に、第1

の単結晶Si層およびSiGe層を通るGeの相互拡散を可能にする加熱ステップを施し

て、障壁層の上に、実質的に緩和された単結晶であり均質のSiGe層を形成する。改善

された性質を有するSiGeオンインシュレータ、およびそれを含むヘテロ構造も提供さ

れる。

(もっと読む)

半導体ウェハ及びその製造法

【課題】高い結晶品質を有する、多様な材料からなる、完全に緩和した、又は歪んだ半導体層を積層するために絶縁体層の格子寸法を調整するための高い柔軟性を許容する、SOI構造の作製のための基板を提供する。

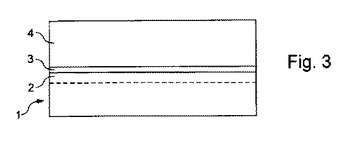

【解決手段】実質的にシリコンからなる単結晶基板ウェハ1、電気絶縁性材料を含み、かつ2nm〜100nmの厚さを有する第一非晶質中間層2、立方晶系Ia−3結晶構造と、(Me12O3)-1-x(Me22O3)xの組成と、基板ウェハの材料の格子定数と0%〜5%異なる格子定数とを有する単結晶第一酸化物層3を示される順序で含むことを特徴とする半導体ウェハ。

(もっと読む)

SOI基板の作製方法

【課題】ガラス基板など耐熱温度が低い基板を用いた場合にも、実用に耐えうるSOI層を備えたSOI基板を提供する。また、そのようなSOI基板を用いた半導体装置を提供する。

【解決手段】ガラス基板などのベース基板に、単結晶半導体基板を接合するため、接合層に、例えば有機シランを原材料としてCVD法で成膜した酸化シリコン膜を用いる。ガラス基板等の耐熱温度が700℃以下の基板でであっても接合部の結合力が強固なSOI基板を形成することができる。また、単結晶半導体基板から分離された半導体層にレーザ光を照射して、その表面を平坦化し、かつ、その結晶性を回復する。

(もっと読む)

半導体装置

【課題】銅めっきをアンテナに用いた、集積回路とアンテナが一体形成された半導体装置において、銅の拡散による回路素子の電気特性への悪影響を防止し、また、集積回路とアンテナが一体形成された半導体装置において、アンテナと集積回路の接続不良に伴う半導体装置の不良を防止する装置を提供する。

【解決手段】半導体装置によると、同一の基板102上に集積回路100とアンテナ101とが一体形成された半導体装置において、銅めっき層108をアンテナ101の導体に用いた場合に、アンテナ101の下地層107に所定の金属の窒化膜を用いているので銅の回路素子への拡散を防ぎ、銅の拡散による回路素子の電気特性への悪影響を低減できる。また、アンテナの下地層の金属の窒化物の一つにニッケルの窒化物を用いることで、アンテナと集積回路の接続不良を低減することができる。

(もっと読む)

1 - 20 / 46

[ Back to top ]