Fターム[5F152NQ05]の内容

再結晶化技術 (53,633) | 動作層、活性層、素子構成層の材料 (2,604) | 半導体 (2,300) | 3−5族 (966)

Fターム[5F152NQ05]の下位に属するFターム

Fターム[5F152NQ05]に分類される特許

21 - 40 / 256

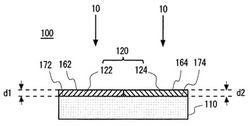

半導体基板、半導体基板の製造方法、および電磁波発生装置

【課題】複数の異なる周波数を出力する半導体基板を提供する。

【解決手段】p型半導体またはn型半導体を含む第1の不純物半導体と、第1の不純物半導体に接する複数の空乏領域を有する空乏化半導体とを備え、複数の空乏領域のそれぞれは、第1の不純物半導体との第1界面と、第1界面と対向する表面とを有し、複数の空乏領域のそれぞれは、第1界面に垂直な方向における第1界面と表面との平均距離および組成の少なくとも一つが異なる半導体基板を提供する。

(もっと読む)

半導体基板、半導体デバイスおよび半導体基板の製造方法

【課題】中間層としてGe結晶を用いる場合の化合物半導体へのGe原子の混入を抑制する。

【解決手段】ベース基板と、ベース基板上に形成された第1結晶層と、第1結晶層を被覆する第2結晶層と、第2結晶層に接して形成された第3結晶層とを備え、第1結晶層が、ベース基板における第1結晶層と接する面と面方位が等しい第1結晶面、及び、第1結晶面と異なる面方位を有する第2結晶面を有し、第2結晶層が、第1結晶面と面方位が等しい第3結晶面、及び、第2結晶面と面方位が等しい第4結晶面を有し、第3結晶層が、第3結晶面及び第4結晶面のそれぞれの少なくとも一部に接しており、第1結晶面に接する領域における第2結晶層の厚みに対する第2結晶面に接する領域における第2結晶層の厚みの比が、第3結晶面に接する領域における第3結晶層の厚みに対する第4結晶面に接する領域における第3結晶層の厚みの比よりも大きい半導体基板を提供する。

(もっと読む)

半導体基板の製造方法および半導体デバイスの製造方法

【課題】シリコンデバイス等耐熱性の低い部位がSi基板に設けられた場合でも、Ge結晶に熱アニールを施し、十分な結晶品質のGe結晶薄膜を得る。

【解決手段】表面がSiであるベース基板と、前記ベース基板の上に形成され、組成がCxSiyGezSn1−x−y―z(0≦x<1、0≦y<1、0<z≦1、かつ、0<x+y+z≦1)である第1結晶層と、前記第1結晶層が形成された部分以外の前記ベース基板の上に形成された第1半導体素子と、を有する半導体基板の製造方法であって、前記第1半導体素子には電磁波を照射することがなく、前記第1結晶層の一部または全部に電磁波を照射する工程を有する半導体基板の製造方法を提供する。

(もっと読む)

半導体薄膜の形成方法

【課題】所望の特性が得られる状態で、InPからなる基板の表面に付着した汚染物としての不純物による問題が解消できるようにする。

【解決手段】まず、Feが添加された半絶縁性のInPからなる基板101の上に、炭素(C)を添加したGaAsSbからなる半導体層(第1半導体層)102を形成する。半導体層102は、Cの添加によりp型とされている。また、添加されるCは、基板101の表面に付着している不純物とは逆の電気的特性を有する不純物となる。なお、半導体層102は、InおよびGaの少なくとも一方とAs,Sbとを少なくとも備える化合物半導体から構成されていればよく、AlzInxGa1-x-zAs1-ySby(0≦x≦0.2,0.3≦y≦1,0≦z≦1,0≦x+z≦1)から構成されていればよい。

(もっと読む)

半導体基板、電子デバイス及び半導体基板の製造方法

【課題】シリコン基板上の一部の領域に形成する3族窒化物半導体の結晶性を高める製造方法を提供する。

【解決手段】表面がシリコン結晶であるベース基板102と、シリコン結晶上の一部の領域に形成されたSixGe1−xC(0≦x<1)エピタキシャル結晶104と、SixGe1−xC(0≦x<1)エピタキシャル結晶104上に形成された3族窒化物半導体結晶106とを含む半導体基板100を提供する。一例として、当該半導体基板100は、シリコン結晶上に形成され、かつ、シリコン結晶を露出する開口110を有し、結晶の成長を阻害する阻害体108をさらに含み、SixGe1−xC(0≦x<1)エピタキシャル結晶104は、開口110の内部に形成されている。

(もっと読む)

薄膜半導体の製造方法

【課題】薄膜半導体を、低コストをもって容易、確実に得ることができるようにする。

【解決手段】半導体基体表面に複数回の陽極化成処理を行い、多孔率の異なる複数の層からなる多孔質層を形成する工程を有する。そして、形成した多孔質層の表面を、酸素雰囲気中でアニール処理した後、水素雰囲気中でアニール処理する工程を有数する。さらに、多孔質層上にエピタキシャル半導体膜を形成する工程と、多孔質層においてエピタキシャル半導体膜を半導体基体から剥離する工程とを有する。

(もっと読む)

共通基板上にカラムIII−VトランジスタとともにシリコンCMOSトランジスタを有する半導体構造

半導体構造は、ある結晶方位を有するシリコン基板(12)と、シリコン基板(12)の上方に配置された絶縁性層(18/22)と、絶縁性層の上方に配置され、基板の結晶方位とは異なる結晶方位を有するシリコン層(20)と、シリコン基板上に配置され、基板と同じ結晶方位を有するカラムIII−Vトランジスタデバイス(34)とを有する。一実施形態では、カラムIII−Vトランジスタデバイスが、基板と接触する。別の実施形態では、デバイスは、GaNデバイスである、または基板の結晶方位が<111>であり、シリコン層の結晶方位が<100>である。一実施形態では、CMOSトランジスタが、シリコン層内に配置される。一実施形態では、カラムIII−Vトランジスタデバイスが、カラムIII−Nデバイスである。一実施形態では、カラムIII−Asデバイス、カラムIII−Pデバイス、またはカラムIII−Sbデバイスが、<100>シリコン層の上面上に配置される。  (もっと読む)

(もっと読む)

半導体基板、半導体デバイスおよび半導体基板の製造方法

【課題】単一のシリコン基板上に種類の異なる半導体結晶層をエピタキシャル成長させる場合に、表面の平坦性を向上し、半導体デバイスの信頼性を高める。

【解決手段】第1窪みおよび第2窪みが形成されたシリコン結晶を表面に有するベース基板と、第1窪みの内部に形成され、露出されている第1のIVB族半導体結晶と、第2窪みの内部に形成された第2のIVB族半導体結晶と、第2窪みの内部の第2のIVB族半導体結晶上に形成され、露出されているIII−V族化合物半導体結晶とを備える半導体基板を提供する。

(もっと読む)

半導体基板及び半導体基板の製造方法

【課題】半導体基板のアライメントマークを繰り返し使用する。

【解決手段】ベース基板にアライメントマークを形成する段階と、アライメントマークを形成する段階の後に、ベース基板上のアライメントマークを含む領域に、結晶成長を阻害する阻害層を形成する段階と、アライメントマークの位置を基準とする開口を形成すべき位置を示す情報に基づいて、阻害層におけるアライメントマークが設けられていない領域に、ベース基板を露出する開口を形成する段階と、開口内に半導体結晶を成長させる段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

SOI基板の作製方法

【課題】低温での固相エピタキシャル成長法を用いて、単結晶半導体層の膜厚の厚いSOI基板を提供することを課題の一とする。その際に、予めシード層となる単結晶半導体層の結晶欠陥を修復しなくとも、良好にエピタキシャル成長が進む方法を提供することを課題の一とする。また、シード層の結晶欠陥を修復する工程を別に設けなくとも、固相エピタキシャル成長によりシード層である単結晶半導体層の結晶性が回復したSOI基板を提供することを課題の一とする。

【解決手段】絶縁層を介して基板に設けられた第1単結晶半導体層上に、非晶質半導体層を形成する。非晶質半導体層は、成膜温度100℃以上275℃以下、シラン系ガスを希釈しないで用いるCVD法により形成する。熱処理を行って、非晶質半導体層を固相エピタキシャル成長させて、単結晶半導体層の膜厚の厚いSOI基板を作製する。

(もっと読む)

SOI基板の作製方法およびSOI基板

【課題】ベース基板(例えばガラス基板)と半導体基板(例えば単結晶シリコン基板)とを貼り合わせてSOI基板を作製する際の半導体層(例えば単結晶シリコン層)の表面の荒れを抑制することを目的の一とする。

【解決手段】溝部が設けられた半導体基板に、イオンを照射して半導体基板中に脆化領域を形成し、絶縁層を介して半導体基板とベース基板を貼り合わせると共に、半導体基板の溝部とベース基板とにより囲まれた空間を形成し、熱処理を施すことにより、脆化領域において半導体基板を分離して、ベース基板上に絶縁層を介して半導体層を形成する。

(もっと読む)

半導体基板の再生方法、再生半導体基板の作製方法、および、SOI基板の作製方法

【課題】半導体基板の再生に適した方法を提供することを目的の一とする。

【解決手段】損傷半導体領域と絶縁層とを含む凸部が周縁部に存在する半導体基板に対し、絶縁層が除去されるエッチング処理と、半導体基板を構成する半導体材料を酸化する物質、酸化された半導体材料を溶解する物質、および、半導体材料の酸化の速度および酸化された半導体材料の溶解の速度を制御する物質、を含む混合液を用いて、未損傷の半導体領域に対して損傷半導体領域が選択的に除去されるエッチング処理と、損傷半導体領域が選択的に除去されるエッチング処理の後に、半導体基板の表面に研磨を行う半導体基板の再生方法である。

(もっと読む)

半導体基板、電子デバイスおよび半導体基板の製造方法

【課題】シリコン基板を用いてGaAs系の良質な半導体結晶膜を形成する。

【解決手段】第1領域と第2領域とを表面に有する基板と、前記第1領域の上方に形成された第1半導体と、を含み、前記基板は、表面がSixGe1−x(0≦x≦1)であり、前記第1領域は、前記第2領域により囲まれ、前記第1半導体は、砒素を含有する3−5族化合物半導体であり、単結晶であり、且つ前記SixGe1−xと格子整合または擬格子整合し、前記第2領域は、前記第1領域とは性状が異なる半導体基板を提供する。

(もっと読む)

半導体素子の製造方法

【課題】 半導体層のエッチング時間の短縮化が望まれている。

【解決手段】 第1の膜及び半導体膜がこの順番に形成された積層基板の前記半導体膜の上に、マスクパターンを形成する。マスクパターンをエッチングマスクとして、半導体膜をエッチングすることにより、凹部を形成するとともに、凹部の底面の一部の領域に第1の膜が露出し、他の領域には、半導体膜の残渣が残っている状態でエッチングを停止させる。凹部の底面に露出した第1の膜を厚さ方向及び横方向にエッチングすることにより、残渣の下に空洞を形成する。積層基板を浸漬させた液体に超音波を印加することにより、空洞の上に残留している残渣を積層基板から脱離させる。

(もっと読む)

SOI基板の作製方法及び半導体装置の作製方法

【課題】平坦性を確保しつつ、結晶性の高い半導体膜を有する、SOI基板の作製方法を提供することを、目的の一とする。

【解決手段】分離により絶縁膜上に単結晶の半導体膜を形成した後、該半導体膜の表面に存在する自然酸化膜を除去し、半導体膜に対して第1のレーザ光の照射を行う。第1のレーザ光の照射は、希ガス雰囲気下、窒素雰囲気下または減圧雰囲気下にて、半導体膜の任意の一点におけるレーザ光のショット数を7以上、より好ましくは10以上100以下とする。そして、第1のレーザ光の照射を行った後、半導体膜に対して第2のレーザ光の照射を行う。第2のレーザ光の照射は、希ガス雰囲気下、窒素雰囲気下または減圧雰囲気下にて、半導体膜の任意の一点におけるレーザ光のショット数を0より大きく2以下とする。

(もっと読む)

SOI基板の作製方法およびSOI基板

【課題】ベース基板(例えばガラス基板)とボンド基板(例えば単結晶シリコン基板)とを貼り合わせてSOI基板を作製する際の半導体層(例えば単結晶シリコン層)の表面の荒れを抑制することを目的の一とする。または、上記荒れを抑えて半導体装置の歩留まりを向上することを目的の一とする。

【解決手段】ボンド基板にイオンを添加して該ボンド基板に脆化領域を形成し、ベース基板にレーザー光の照射による複数の凹凸部を形成し、絶縁層を介してボンド基板とベース基板とを貼り合わせる際に、複数の凹凸部をボンド基板とベース基板との位置合わせの指標として用いると共に、複数の凹凸部の一を含む領域に、ボンド基板とベース基板とが貼り合わない領域であってその外周が閉じられた領域を形成し、熱処理を施すことにより、脆化領域においてボンド基板を分離して、ベース基板上に半導体層を形成する。

(もっと読む)

半導体装置の作製方法

【課題】半導体膜への不純物の拡散を抑えつつ、歩留まりの低下を抑えることができるSOI基板の作製方法を提供することを、目的の一とする。

【解決手段】半導体基板の表面を熱酸化させることで、酸化膜が形成された半導体基板を形成する。そして、窒素原子を有するガス雰囲気下においてプラズマを発生させることにより、上記酸化膜の一部をプラズマ窒化させ、酸化膜上に窒素原子を含む絶縁膜が形成された半導体基板を得る。そして、窒素原子を含む絶縁膜とガラス基板を接合させた後、半導体基板を分離することで、ガラス基板上に窒素原子を含む絶縁膜、酸化膜、薄膜の半導体膜が順に積層されたSOI基板を形成する。

(もっと読む)

ナノスケールのエピタキシー技術(Nano−ScaleEpitaxyTechnology)を用いた高品質のヘテロエピタキシー

【課題】ナノスケールのエピタキシー技術を用いた高品質のヘテロエピタキシーを提供する。

【解決手段】集積回路構造は、第一半導体材料からなる半導体基板と、半導体基板の二つの絶縁体と、二つの絶縁体間にあってそれらの側壁に隣接する半導体領域とを備える。半導体領域は、第一半導体材料と異なる第二半導体材料からなり、幅は約50 nmより小さい。

(もっと読む)

半導体デバイスおよび半導体構造の製造方法

【課題】 半導体結晶材料の作製またはこの半導体結晶材料を含む構造を提供する。

【解決手段】 第1の半導体結晶材料の表面の粗さは、低減されている。半導体デバイスは、第1の結晶材料の表面上に低欠陥の歪んだ第2の半導体結晶材料を含む。歪んだ第2の半導体結晶材料の表面の粗さは、低減されている。一実施例は、第1および第2の半導体結晶材料間の界面境界の不純物を減少させるプロセスパラメータを作成することによって、粗さが低減された表面を得ることを含む。一実施の形態では、第1の半導体結晶材料は、アスペクト比トラッピング技術を用いて欠陥をトラップするのに十分なアスペクト比を有する絶縁体の開口によって限定されることができる。

(もっと読む)

ハニカムヘテロエピタキシーを含む半導体装置

【課題】ハニカムヘテロエピタキシーを含む半導体装置を提供する。

【解決手段】ハニカムヘテロエピタキシーを含む半導体装置とその製造方法が開示される。一実施例は、貫通する複数のナノサイズの開口を有するマスクをシリコン基板上に定義するステップと、定義ステップ後、マスク開口を介して露出したシリコン基板表面の一部に、本質的に無欠陥の非シリコン半導体ナノアイランドを作成するステップと、作成ステップ後、ナノアイランド上に、高kゲート誘電体を蒸着するステップと、蒸着ステップ後、ナノアイランド上に、トランジスタを構成するステップとを備える方法である。

(もっと読む)

21 - 40 / 256

[ Back to top ]