Fターム[5H420NB26]の内容

電気的変量の制御(交流、直流、電力等) (13,664) | 出力部 (2,015) | 出力制御回路に付加された素子 (700) | コンデンサ (32)

Fターム[5H420NB26]に分類される特許

1 - 20 / 32

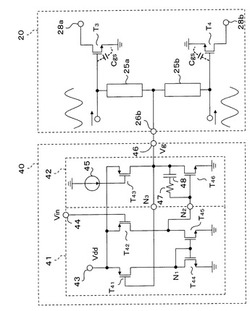

定電圧回路及び増幅回路

【課題】ゲート容量が大きなトランジスタを有する増幅器に接続しても発振を防止できる定電圧回路及び増幅回路を提供する。

【解決手段】定電圧回路40は、所定の電圧が印加される第1の入力端子44と、出力端子46に接続された第2の入力端子とを備えた差動増幅部41と、ソースが接地され、ドレインが出力端子46に接続され、ゲートに差動増幅部41の出力が与えられるトランジスタT46を備えたソース接地型増幅器42とを有する。そして、トランジスタT46のゲートとドレインとの間には、抵抗47とコンデンサ48とが直列に接続されている。定電圧回路40から出力される電圧Vgは、増幅器20のバイアス端子26bからバイアス給電用インダクタ25a,25bを介してトランジスタT3,T4に供給される。

(もっと読む)

差動増幅回路、レギュレータモジュール及びハイパワーアンプ

【課題】製造時の工程及び製品の消費電力の点で優れたレギュレータモジュール、及びそれを用いたバイアス回路を提供する。

【解決手段】パワーアンプモジュールとレギュレータモジュール801を含むパワーアンプをバイポーラトランジスタと電界効果トランジスタとを同一基板上に備える技術によって1チップで構成する。レギュレータモジュール801はデプリーション型トランジスタによる差動増幅回路を内包する。該差動増幅回路の一方のFETQ4のソース端子を、ダイオード接続したバイポーラトランジスタQ7を介して、FETQ3のソース端子と接続することで、バイポーラトランジスタQ7の電位差をレギュレータの出力電圧とすることが可能となる。

(もっと読む)

基準電圧回路

【課題】回路規模が小さく、電圧に連続性があるソフトスタート機能を有した基準電圧回路を提供する。

【解決手段】デプレッションタイプMOSトランジスタとエンハンスメントタイプMOSトランジスタから構成される基準電圧部と、ゲートが第一のエンハンスメントタイプMOSトランジスタのゲート及びドレインと接続され、ドレインが基準電圧回路の出力端子に接続されたエンハンスメントタイプMOSトランジスタと、一方の端子が基準電圧部の出力端子に接続され、他方の端子がエンハンスメントタイプMOSトランジスタのドレインに接続されたMOSスイッチと、電源と接地間に直列に接続された定電流源及び容量と、から構成されるソフトスタート回路と、を備えた基準電圧回路。

(もっと読む)

電流源回路

【課題】矩形波の信号入力に応じて出力する出力電流の波形を矩形波に近づけることが可能な電流源回路を提供する。

【解決手段】電流源回路は、電圧端子に一端が接続された第1のMOSトランジスタと、第1のMOSトランジスタの他端に一端が接続され、出力端子に他端が接続された第2のMOSトランジスタと、電圧端子に一端が接続された第3のMOSトランジスタと、第3のMOSトランジスタの他端に一端が接続され、出力端子に他端が接続された第4のMOSトランジスタと、を備える。この電流源回路は、第1のMOSトランジスタおよび第4のMOSトランジスタに電流が流れるように第1の入力端子にバイアス電圧が印加された状態で、第2の入力端子に印加されるスイッチ電圧に応じて、第2のMOSトランジスタおよび第3のMOSトランジスタのオン/オフを同期して制御する。

(もっと読む)

半導体装置

【課題】所定レベルの電圧を早期に生成するとともに、回路規模の増大を防ぐことが可能な半導体装置を提供する。

【解決手段】半導体装置101は、第1の電源電圧が供給される第1電源ノードと第1の電源電圧よりも低い第2の電源電圧が供給される第2電源ノードとの間に接続され、第1電源ノードからキャパシタCが電気的に接続されるべき基準ノードへ電流を流すことにより、キャパシタCを充電し、基準ノードの電位を所定電圧レベルにするための基準電圧生成回路11と、第1電源ノードと基準ノードとの間に直列接続された抵抗およびスイッチ、または第1電源ノードと基準ノードとの間に接続されたトランジスタを含み、第1電源ノードから基準ノード経由でキャパシタCへ電流を流すことにより、基準電圧生成回路11よりも速くキャパシタCを充電することが可能な充電加速回路10とを備える。

(もっと読む)

バンドギャップリファレンス回路及びこれを備えるADコンバータ、並びに、バンドギャップリファレンス回路の調整方法

【課題】温度依存性を持たないバンドギャップリファレンス回路を提供する。

【解決手段】第1及び第2の入力端に供給される電位差に基づいて電流経路PA,PBに流れる電流量を制御することによりリファレンス電圧を生成するオペアンプOPと、第1及び第2の入力端が電流経路PA,PBに含まれる接続点A,Bにそれぞれ接続されている場合に得られるリファレンス電圧VREF1と、第1及び第2の入力端が接続点B,Aにそれぞれ接続されている場合に得られるリファレンス電圧VREF2との中間値を生成するローパスフィルタLPFとを備える。これにより、オペアンプOPのオフセット電圧がキャンセルされることから、オフセット電圧がゼロである場合に得られる理想的なリファレンス電圧VREFを生成することが可能となる。

(もっと読む)

進相コンデンサ制御装置

【課題】変圧器ロスの増加を抑制するとともに、フェランチ現象も抑制できる進相コンデンサ制御装置を提供する。

【解決手段】構内配電系統に設けられ、進相コンデンサ開閉器の投入開放制御を行う進相コンデンサ制御装置において、測定された変圧器の2次電流値と、想定電圧値と負荷の想定力率値とにより上記変圧器を通過する無効電力を推定し、あるいは受電点で測定された有効電力と負荷の想定力率値とにより受電点における無効電力を推定する無効電力推定部と、この無効電力推定部が推定した無効電力を補償するように、進相コンデンサ開閉器の投入開放制御の判断をおこない、進相コンデンサ開閉器に対し投入するまたは開閉する制御指令を出す制御決定部とを設けた。

(もっと読む)

基準電圧発生回路

【課題】雑音を低減するローパスフィルタの容量を高速で充電して、高速に出力電圧を整定することが可能な基準電圧発生回路を提供する。

【解決手段】基準となる直流電圧を発生する基準電圧源1と、基準電圧源の出力に接続されたローパスフィルタ2と、基準電圧源の出力が入力端子に接続されローパスフィルタの出力が出力端子に接続された電圧ゲインが1倍の第1電圧バッファ回路10と、基準電圧源の出力が一方の入力端子に接続されローパスフィルタの出力が他方の入力端子に接続されたヒステリシスコンパレータ11とを備える。起動時に基準電圧源の出力とローパスフィルタの出力の電圧差が所定値を超えている期間は、ヒステリシスコンパレータの出力信号により第1電圧バッファ回路の出力インピーダンスが制御される。起動時にローパスフィルタを低インピーダンスで急速に充電することにより、整定の時間を早めることができる。

(もっと読む)

スイッチング電源装置

【目的】過負荷状態が発生して出力電圧Voutが低下しても素早くリカバーし、しかもその後の出力電圧のオーバーシュートを対策することのできるスイッチング電源装置を提供する。

【構成】時刻t0で過負荷が発生すると、出力電圧Voおよびフィードバック信号VFBが減少する。ソフトスタート信号VSOFTもクランプ回路の働きによりVFBに追従して減少する。基準電圧Vref≧ソフトスタート信号VSOFTとなるt1〜t2の期間は、ソフトスタート信号VSOFTとフィードバック信号VFBが比較されて誤差信号Error Signalが生成される。従い、誤差信号を生成するための、フィードバック信号VFBとその比較相手との差分は△V以上に大きくならないから、誤差信号およびスイッチング素子のオンデューティが過大になることを防ぐことができ、これにより出力電圧回復時のオーバーシュートを抑制することができる。

(もっと読む)

過電流保護回路

【課題】広範囲のデューティ比に対応して過電流検出できるようにする。

【解決手段】過電流保護回路12が、コイルL1、コンデンサC1、微分回路8、過電流判定回路11を主とした回路によって形成されている。微分回路8は、コンデンサC1の時間変動に基づくノードN4の電圧Vkの変動を検出して出力電圧V0とする。過電流判定回路11はこの出力電圧V0の出力結果に基づいてNMOSトランジスタ4に通ずる電流が過電流であるか否かを判定する。

(もっと読む)

階段電圧生成回路

【課題】導体の接続形態に係る回路構成の自由度を高めた階段電圧生成回路を提供する。

【解決手段】N−1個の導体系D1〜D4と、直流電源電位の導体D5と、回路グランド電位の導体D0とを有し、N−1個の導体系からN−1個の端子を取り出し、当該N−1個の端子の各々と出力端子との間と、直流電源電位の導体D5と出力端子との間と、回路グランド電位の導体D0と出力端子との間とをスイッチ素子T0〜T5でそれぞれ接続すると共に、負荷容量CLを出力端子に接続し、回路グランド電位の導体に接続されたスイッチ素子をオンT0にし、次に、N−1個の端子に接続されたN−1個のスイッチ素子T1〜T4をあらかじめ定めた任意の順番で順次オンにし、直流電源に接続されたスイッチ素子T5をオンに制御した後に、逆の順番で各スイッチ素子を順次オンに制御することを繰り返えす階段電圧生成回路。

(もっと読む)

電流負帰還回路およびそれを用いるDC−DCコンバータ

【課題】簡便な回路で高速に電流モード制御のためのインダクタンス電流に略比例する、もしくはインダクタンスの充電電流の2次関数となる電流を生成・出力可能とし且つスイッチングノイズの影響を低減できる電流負帰還回路およびそれを用いるDC-DCコンバータを提供する。

【解決手段】カレントミラー回路を構成する第一のPch MOSFET 21と第二のPch MOSFET 22、電流調整抵抗20、電流検出抵抗12、および、定電流源23とで電流検出部300を構成し、定電流源24、第一のスイッチ素子であってキャパシタ27への充電経路となるPch MOSFET 25、第二のスイッチ素子であってキャパシタ27の放電経路となるNch MOSFET 26、及び、キャパシタ27でもって鋸歯状波生成部400を構成し、電流検出部300と鋸歯状波生成部400とで電流負帰還回路500を構成する。

(もっと読む)

閉路判定装置および配電系統システム

【課題】 同一相の位相差を迅速かつ正確に求め、開閉器の開閉可否を早期に判断することで、配電系統に影響を与える横流を防止しつつ、円滑にループ切替を実施させることを目的としている。

【解決手段】 本発明にかかる代表的な構成は、異なる配電系統それぞれに接続され異なる配電系統間を開閉する開閉器110に併設される閉路判定装置120であって、開閉器における異なる配電系統それぞれの3相線路総ての電圧を連続的に測定する電圧測定部122と、測定された各電圧波形の、ゼロクロス点と基準時刻との相対時間を計数し、相対位相角を導出する相対位相角導出部124と、異なる配電系統間で対応する相同士の相対位相角の差分である位相差を計算する位相差計算部126と、計算された位相差が横流を許容できる所定範囲内であれば、開閉器の閉路を許可する閉路許可部128と、を備えることを特徴とする。

(もっと読む)

電源装置

【課題】コスト増を伴うことなくセラミックコンデンサを使用した電源回路において位相補償を可能とする電源装置を提供する。

【解決手段】回路基板70は、電源回路72の出力側に接続され、負荷回路71に対して並列的に配設されるセラミックコンデンサ73と、セラミックコンデンサ7の一方端側に接続され、負荷回路71に対して並列的に配設される配線抵抗74と、により構成される。また、配線抵抗74は、所定領域内に収めるために、屈曲形状により形成する。

(もっと読む)

チャージポンプ回路

【課題】 温度が変動しても出力電圧である昇圧電圧が変動しにくいチャージポンプ回路を提供する。

【解決手段】 補正用ダイオードD1に発生した順方向電圧Vfにより、チャージポンプ回路の出力電圧である昇圧電圧4VrefはダイオードD2〜D5に発生した順方向電圧Vfを含まなくなるので、温度が変動してダイオードD2〜D5に発生する順方向電圧Vfが変動しても、昇圧電圧4Vrefは変動しにくくなる。よって、温度が変動しても、昇圧電圧4Vrefはバラツキが抑制されるので、チャージポンプ回路による昇圧速度のバラツキも抑制される。

(もっと読む)

定電圧回路、定電圧供給システム、および定電圧供給方法

【課題】 入力電圧から出力電圧への電圧変換経路にローパスフィルタを備える構成により、入力電圧の過渡的な変動が抑制され安定した定電圧を出力することが可能な定電圧回路、定電圧供給システム、および定電圧供給方法を提供すること

【解決手段】 PMOSトランジスタM1のゲート端子に入力される入力電圧信号VINは、定電流源ISによりPMOSトランジスタM1のソース端子を介して流されるバイアス電流I1に応じて、ソース端子においてPMOSトランジスタM1のゲート・ソース間電圧でレベルシフトされた電圧値に変換される。変換された電圧は、容量素子C1を経てソースフォロア回路から出力される。入力電圧信号VINからソースフォロア回路に至る信号経路には、PMOSトランジスタM1のインピーダンスと容量素子C1とによりローパスフィルタが構成される。

(もっと読む)

き電線電圧補償装置

【課題】車両突入電流の直流成分により直列コンデンサに発生する直流電圧成分の影響を受けることのないき電線電圧補償装置を提供する。

【解決手段】三相交流電力を単相2座の電力に変換するき電変圧器1と、前記き電変圧器1の2次側のT座とき電線2Tとを結ぶ電路に介挿された直列コンデンサ3Tと、前記き電変圧器1の2次側のM座とき電線2Mとを結ぶ電路に介挿された直列コンデンサ3Mとを備え、前記き電変圧器1のT座および前記直列コンデンサ3Tの共通接続点5Tと、前記き電変圧器1のM座および前記直列コンデンサ3Mの共通接続点5Mとの間に接続され、単相インバータ12T,12M、インバータ用変圧器11T,11Mおよび直流コンデンサ13を有し、無効電力の補償機能および有効電力の三相平衡化機能を有して前記き電線2T、2Mの電圧補償を行う電圧補償装置20を具備した。

(もっと読む)

基準電圧発生回路

【課題】電源電圧が高い場合でも、オン状態となるために必要な電圧Vtが比較的低いトランジスタを用いてスタートアップ回路を構成する。

【解決手段】スタートアップ回路30aの定電流源として機能するPMOSトランジスタ31aの出力側に、PMOSトランジスタ34のソースが接続される。PMOSトランジスタ34のゲートには、差動増幅器20aの入力端として機能するPMOSトランジスタ22および23のソース電位が印加されている。この結果、スタートアップ回路30aのPMOSトランジスタ34のドレイン電位は1.5V程度となるため、NMOSトランジスタ33のVtが比較的低いトランジスタを適用でき、さらに出力ノードN1が基準電位に達するまでには確実にオン状態となり、スタートアップ回路30aは安定して動作する。

(もっと読む)

電力品質改善装置

【課題】軽負荷時に発生する電圧上昇や高調波過電流の増大を抑制できる電力品質改善装置を提供することである。

【解決手段】制御装置24は、無効電力計22で検出された無効電力が所定の進相無効電力以上であるときは、半導体スイッチ21の開指令を出力して電力用コンデンサ20を系統から切り離し、一方、無効電力計22で検出された無効電力が所定の遅相無効電力以上であるときは、電力用コンデンサ20に流れる突入電流のピーク値が所定値より小さくなる受電母線の電圧位相で半導体スイッチ21の閉指令を出力し、電力用コンデンサ20を系統に接続する。

(もっと読む)

基準電圧生成回路

【課題】外部電源のノイズの影響を阻止しつつ、基準電圧を生成する。

【解決手段】電流制御部30のトランジスタNM31のゲートは、トランジスタNM13,NM14のゲートに接続されて、トランジスタNM13,NM14にそれぞれ流れるドレイン電流と同じ量のドレイン電流がトランジスタNM31に流れる。このドレイン電流は、定電流回路部20のトランジスタPM22にも流れる。トランジスタPM21とトランジスタPM22のチャンネル幅の比は、3対1に設定され、トランジスタPM21には、トランジスタPM22の3倍の電流が流れる。トランジスタPM21,PM22は飽和領域で動作し、電圧VCの外部電源から供給された電流を定電流化し、基準電圧Vrefを生成するバンドギャップ回路部10に供給する。バンドギャップ回路部10に供給される電流が定電流化されるので、外部電源に重畳したノイズの影響は阻止される。

(もっと読む)

1 - 20 / 32

[ Back to top ]