Fターム[5H420NB27]の内容

電気的変量の制御(交流、直流、電力等) (13,664) | 出力部 (2,015) | 出力制御回路に付加された素子 (700) | (定)電流源 (48)

Fターム[5H420NB27]に分類される特許

1 - 20 / 48

基準電圧回路及び半導体基板

【課題】電源電位が接地電位に対して変動するハイサイド回路又はローサイド回路において、電源電位の変動の影響を回避し、安定した基準電圧を出力することができる基準電圧回路及び半導体基板を提供する。

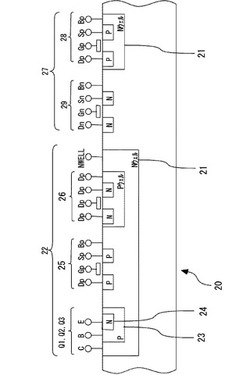

【解決手段】本発明は、P型半導体基板20上のNウェル層21内に形成したハイサイド回路中において、Nウェル層21をコレクタとし、Nウェル層21内に形成したP領域23をベースとし、ベースの上層に形成したN領域24をエミッタとし、ハイサイド回路素子22を構成する基板を、コレクタとしてのNウェル層21とで共通化した。

(もっと読む)

定電圧発生回路

【課題】定電圧発生回路の回路面積及び消費電流を削減しながら、負荷の直流的及び過渡的な変化に対する出力電圧の変化を小さくする。

【解決手段】FET4は、電圧源端子に接続されたドレインと出力端子に接続されたソースとを備える。FET2は、FET4のソースに接続されたゲートと、FET4のゲートに接続されたドレインとを有する。FET1は、FET2のソースと接地端子との間に設けられ、ダイオード接続されている。FET3は、電圧源端子とFET2のドレインとの間に接続され、そのドレインとソースとの間に所定の電位差を有し、第1の定電流源として機能する。FET5は、出力端子と接地端子との間に接続される。FET1及びFET5によりカレントミラー回路を構成することにより、FET5は第2の定電流源として機能する。

(もっと読む)

バンドギャップ基準電圧装置

【課題】基準電圧立ち上がり時間の短縮が図れ、起動時間の遅延を防止することができるバンドギャップ基準電圧装置の提供。

【解決手段】バンドギャップ基準電圧装置は、出力端子300aより所定の基準電圧VREFを出力するバンドギャップ回路10と、バンドギャップ回路10に電流を供給して該バンドギャップ回路10を起動させる定電流源11と、バンドギャップ回路10の起動時に、出力端子300aからバンドギャップ回路10に電流を供給する電流供給部と、を備えたことを特徴とする。

(もっと読む)

半導体集積回路

【課題】安定に動作する半導体集積回路を提供する。

【解決手段】ラッチ回路部105は、ダイオード接続されたトランジスタM7と、そのトランジスタM7からの電流が流入する静電容量素子C1との接続点であるノードN4の電位上昇に応じて、定電流回路部12へ起動電流を供給するトランジスタM5を駆動制御する。ラッチ回路部105内のインバータT1に入力されたノードN4の電位が論理“H”と認識され、インバータT1の出力が論理“L”となって、ラッチ回路部105内のトランジスタM8が導通状態になることで、トランジスタM5の非導通状態が維持され、ノードN4の電位が電源電圧に保持される。

(もっと読む)

定電圧回路及び増幅回路

【課題】ゲート容量が大きなトランジスタを有する増幅器に接続しても発振を防止できる定電圧回路及び増幅回路を提供する。

【解決手段】定電圧回路40は、所定の電圧が印加される第1の入力端子44と、出力端子46に接続された第2の入力端子とを備えた差動増幅部41と、ソースが接地され、ドレインが出力端子46に接続され、ゲートに差動増幅部41の出力が与えられるトランジスタT46を備えたソース接地型増幅器42とを有する。そして、トランジスタT46のゲートとドレインとの間には、抵抗47とコンデンサ48とが直列に接続されている。定電圧回路40から出力される電圧Vgは、増幅器20のバイアス端子26bからバイアス給電用インダクタ25a,25bを介してトランジスタT3,T4に供給される。

(もっと読む)

内部電源電圧生成回路

【課題】ロジック回路の動作時、貫通電流が、製造ばらつきの影響により過大とならず、消費電流を抑えることが可能な、内部電源電圧生成回路の提供。

【解決手段】内部電源端子の内部電源電圧を生成し、前記内部電源電圧をロジック回路に供給する内部電源電圧生成回路であって、ゲートに与えられる電圧をソースフォロワ出力するトランジスタと、前記ゲートに与えられる電圧をソースフォロワ出力するトランジスタの最大電流を制限する電流制限回路と、を備え、ロジック回路への最大電流、及び消費電流を抑えることが可能な構成とした。

(もっと読む)

定電流回路

【課題】より低い電源電圧で動作できる定電流回路を提供する。

【解決手段】電源電圧VDDがディプレッション型NMOSトランジスタ10のドレイン・ソース間電圧Vds10とNMOSトランジスタ15のゲート・ソース間電圧Vgs15との加算電圧よりも高ければ、定電流回路は動作できる。定電流回路の電源電圧VDDとして、1つのドレイン・ソース間電圧と1つのゲート・ソース間電圧との加算電圧が必要になり、1つのドレイン・ソース間電圧と2つのゲート・ソース間電圧との加算電圧は必要ならないので、定電流回路の最低動作電源電圧が低くなる。

(もっと読む)

半導体集積回路、該回路を備えるスイッチング電源及び該電源を備える制御システム

【課題】寄生素子の動作を起因とする不安定動作を防ぐことができる、半導体集積回路を提供すること。

【解決手段】入出力を異なる電流値にする入出力比特性を有するカレントミラーを構成する一対のトランジスタ(63,65)と、前記カレントミラーの出力電流に応じて基準電圧を生成する出力トランジスタとを備える半導体集積回路であって、一対のトランジスタ(63,65)のうち前記電流値が小さい方のトランジスタ63側のコレクタ領域85Aの総面積と一対のトランジスタ(63,65)のうち前記電流値が大きい方のトランジスタ65側のコレクタ領域82と88とを合わせた総面積とが等しくなるように構成されたことを特徴とする、半導体集積回路。

(もっと読む)

基準電圧発生回路とこれを用いた駆動装置、プリントヘッド及び画像形成装置

【課題】電源電圧の変動による基準電圧の変動を抑制し、駆動電流の変動をなくして印刷濃度むらを防止する。

【解決手段】基準電圧発生回路60では、PMOS61a,61bからなる第1のカレントミラー回路とNMOS61c,61dからなる第2のカレントミラー回路とを縦続接続して構成したカレントミラー回路部61を用いて、NPNTR65,66を駆動する構成にしている。そのため、カレントミラー回路部61の出力側のノードN3とノードN4の電位を略等しくすることができる。これにより、電源電圧VDDの値が変化しても、NPNTR66のコレクタ電位の変動を僅少にでき、基準電圧発生回路60から出力される基準電圧Vrefの変動を無視しうる程度にまで減少させることができる。

(もっと読む)

基準電圧回路

【課題】回路規模が小さく、電圧に連続性があるソフトスタート機能を有した基準電圧回路を提供する。

【解決手段】デプレッションタイプMOSトランジスタとエンハンスメントタイプMOSトランジスタから構成される基準電圧部と、ゲートが第一のエンハンスメントタイプMOSトランジスタのゲート及びドレインと接続され、ドレインが基準電圧回路の出力端子に接続されたエンハンスメントタイプMOSトランジスタと、一方の端子が基準電圧部の出力端子に接続され、他方の端子がエンハンスメントタイプMOSトランジスタのドレインに接続されたMOSスイッチと、電源と接地間に直列に接続された定電流源及び容量と、から構成されるソフトスタート回路と、を備えた基準電圧回路。

(もっと読む)

内部電源電圧生成回路

【課題】内部電源電圧を供給されるロジック回路の貫通電流が電源電圧に依存しない内部電源電圧生成回路を提供する。

【解決手段】電流源1の定電流に基づき、基準電圧VREFは電源電圧VDDに依存しないで生成され、基準電圧VREFに基づき、ソースフォロアによって内部電源電圧DVDDが電源電圧VDDに依存しないで生成される。内部電源電圧DVDDに基づき、ロジック回路9の貫通電流が流れる。よって、ロジック回路9の貫通電流は電源電圧VDDに依存しない。また、内部電源電圧DVDDは、ロジック回路9が仕様上動作できる最低のロジック回路9用の電源電圧である。よって、ロジック回路9の貫通電流は少ない。

(もっと読む)

内部電圧発生器

【課題】プルアップ駆動部とプルダウン駆動部が同時に駆動される期間を相殺して、常に一定の内部電圧を維持することができる内部電圧発生器を提供すること。

【解決手段】本発明の内部電圧発生器は、基準電圧を用いて内部電圧のレベルを検出する検出部210と、該検出部の出力信号に応じて、前記内部電圧を出力する内部電圧端を放電駆動する第1の駆動部220と、該第1の駆動部に流れる放電電流を感知する電流感知部230と、該電流感知部の出力信号に応じて、前記内部電圧端を充電駆動する第2の駆動部240とを備える。

(もっと読む)

基準電圧発生回路

【課題】内部にバンドギャップ電圧を生成することなく、バンドギャップ電圧より低く、かつバンドギャップ温度特性を有する基準電圧を発生する基準電圧発生回路を提供する。

【解決手段】接合型素子の順方向電圧をそれに比例する第1の電流に電流変換する第1の比例電流生成回路と、電流密度を変えた一対の接合型素子の順方向電圧の差をそれに比例する第2の電流に電流変換する第2の比例電流生成回路と、第1の電流と第2の電流との差をそれに比例する第1の電圧に電圧変換する電流電圧変換回路と、接合型素子の順方向電圧から第1の電圧を減じた電圧を基準電圧として出力するバッファ回路とを備える。

(もっと読む)

低ドロップアウト線形レギュレータ(LDO)、LDOを提供するための方法、およびLDOを動作させるための方法

【課題】PSRRが改良された低ドロップアウト線形レギュレータを提供する。

【解決手段】LDOは、差動増幅器と調整されたカレントミラーとを結合し、それぞれ差分信号を受信するように構成された2つのノードを有する。調整されたカレントミラーは、差分信号をシングルエンド信号に変換および増幅するように構成される。LDOは、周波数補償用に構成された第1のコンデンサを有し、第1のコンデンサは、第1の段と第2の段との間に結合される。LDOは、第1のカスコード回路の容量性負荷を平衡化するための第2のコンデンサを有し、第2のコンデンサは、第1の段と電源電圧との間に結合される。第1のカスコード回路は、電源電圧の変動によって生じるコンデンサの入出力間の差電圧を抑制するように構成される。LDOは、差動増幅器の電源の変動を抑制するように構成された第2のカスコード回路を有する。

(もっと読む)

電圧発生回路

【課題】低消費電力および高精度な電圧発生回路を提供する。

【解決手段】例えば、電源電圧VCCと接地電源電圧GNDの間に、ソース−ドレイン経路が直列接続される複数のNMOSトランジスタMN1,MN2と、MN1,MN2をサブスレッショルド領域で動作させるための定電流源IS1を備える。MN1,MN2のゲートは、MN2のドレインに共通される。MN1のゲート幅W1およびゲート長L1とMN2のゲート幅W2およびゲート長L2は、例えば、L1=L2かつW2>W1とされる。これにより、MN1のドレイン電圧(Vout_2n)は、GNDを基準に正の温度特性となり、例えば、その後段で負の温度特性のデバイスを加算することで温度依存性が小さい電圧を生成できる。

(もっと読む)

半導体集積回路装置

【課題】温度特性が小さい高精度のバンドギャップ基準電圧発生回路を提供する。

【解決手段】バンドギャップ基準電圧発生回路21内に可変抵抗を設け、可変抵抗の抵抗値を変化させることにより、バンドギャップ基準電圧発生回路21の出力電圧を調整する。調整するバンドギャップ基準電圧発生回路21の出力電圧の値は温度特性ができるだけ小さくなる値に設定する。可変抵抗の抵抗値の可変は、複数の抵抗を設け、その抵抗に接続されたトランジスタ等のスイッチをオンまたはオフさせることにより、各抵抗を有効化あるいは無効化させることによりなされる。バンドギャップ基準電圧発生回路21の出力電圧を最適な値にするための可変抵抗の抵抗値の固定はヒューズ等のトリミング素子を用いて実施する。

(もっと読む)

電流生成回路、電流生成方法及び電子機器

【課題】補正対象の信号の温度特性に対する補正精度を向上させることのできる電流生成回路を提供する。

【解決手段】電流生成回路1aは、温度に依存しない温度特性を備える第1基準電流IMを流す第1電流源10aと、温度に対して所定の傾斜で変化する温度特性を備える第2基準電流IPを流す第2電流源20aとを備える。第1及び第2電流源10a,20a間のノードN1にドレインが接続されるPMOSトランジスタTP1には、第1基準電流IMから第2基準電流IPを減算した第1差分電流IOP(=IM−IP≧0)が流れる。この第1差分電流IOPがカレントミラー回路40aを介して第3基準電流IMSから減算されて出力電流IOが生成される。

(もっと読む)

スイッチング電源装置

【目的】過負荷状態が発生して出力電圧Voutが低下しても素早くリカバーし、しかもその後の出力電圧のオーバーシュートを対策することのできるスイッチング電源装置を提供する。

【構成】時刻t0で過負荷が発生すると、出力電圧Voおよびフィードバック信号VFBが減少する。ソフトスタート信号VSOFTもクランプ回路の働きによりVFBに追従して減少する。基準電圧Vref≧ソフトスタート信号VSOFTとなるt1〜t2の期間は、ソフトスタート信号VSOFTとフィードバック信号VFBが比較されて誤差信号Error Signalが生成される。従い、誤差信号を生成するための、フィードバック信号VFBとその比較相手との差分は△V以上に大きくならないから、誤差信号およびスイッチング素子のオンデューティが過大になることを防ぐことができ、これにより出力電圧回復時のオーバーシュートを抑制することができる。

(もっと読む)

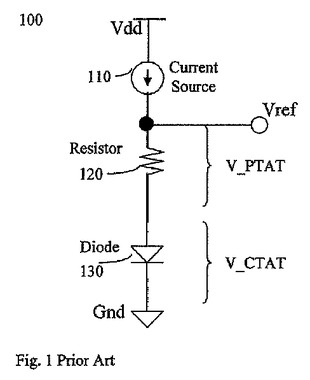

バンドギャップ基準電圧の二次補正回路および方法

より正確なバンドギャップ基準電圧を得るための、一次および二次誤差が同時に補正されるシステムおよび方法が提供される。一次誤差の補正に含まれる成分を用いることによって二次誤差が補正されて、有利なことにはプロセス変動が少なくなる。  (もっと読む)

(もっと読む)

分圧回路

【課題】電圧源からソース電流が流れず、かつ電圧源に対してシンク電流が流れ込まず、高い精度にて入力電圧を所定の比により分圧する分圧回路を提供する

【解決手段】本発明の分圧回路は、入力電圧に対応して第1抵抗に流れる電流を定電流として出力する定電流回路と、定電流が入力電流となり、第1出力電流を出力する第1カレントミラー回路と、第1出力電流が入力電流となり、第2出力電流を出力する第2カレントミラー回路と、第2カレントミラー回路の第2出力電流が出力される出力端子に接続された第2抵抗とを有し、第1カレントミラー回路及び第2カレントミラー回路のカレントミラー比と、第2抵抗及び第1抵抗の抵抗比とにより、第2抵抗の両端の電位差である分圧電圧を調整する。

(もっと読む)

1 - 20 / 48

[ Back to top ]