Fターム[5H420NB36]の内容

電気的変量の制御(交流、直流、電力等) (13,664) | 出力部 (2,015) | その他の特徴 (214) | 出力回路にカレントミラー回路を用いているもの (196)

Fターム[5H420NB36]に分類される特許

1 - 20 / 196

半導体集積回路、および、半導体記憶装置

基準電圧回路及び半導体基板

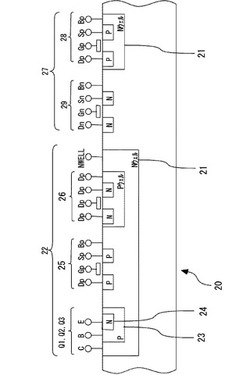

【課題】電源電位が接地電位に対して変動するハイサイド回路又はローサイド回路において、電源電位の変動の影響を回避し、安定した基準電圧を出力することができる基準電圧回路及び半導体基板を提供する。

【解決手段】本発明は、P型半導体基板20上のNウェル層21内に形成したハイサイド回路中において、Nウェル層21をコレクタとし、Nウェル層21内に形成したP領域23をベースとし、ベースの上層に形成したN領域24をエミッタとし、ハイサイド回路素子22を構成する基板を、コレクタとしてのNウェル層21とで共通化した。

(もっと読む)

基準電圧回路

【課題】出力電圧における温度補償をする際の抵抗のばらつきの影響を低減する。

【解決手段】基準電圧(Vref)を生成して出力端から出力するバンドギャップリファレンス回路(1)と、基準電圧の分割電圧(ノードAの電圧)とダイオード(36)の順方向電圧との差電圧に応じて差電圧を電流に変換する電圧電流変換回路(3に相当)と、を備え、電圧電流変換回路は、変換された電流(19)を出力端にフィードバックする。

(もっと読む)

スイッチング電源回路

【課題】バイパス容量の容量値を大きくすることなく、供給電流の変動を抑制する。

【解決手段】負荷の状態に応じて予め設定したピースワイズリニア信号に基づき、負荷が重負荷のとき所定の電流値、軽負荷のとき零となり、重負荷と軽負荷との間で切り替わるとき前記所定の電流値と零との間で線形に変化する電流Im12を入力電圧Vinから生成する。また、前記ピースワイズリニア信号に基づき、負荷が前記重負荷のとき零、前記軽負荷であるとき前記所定の電流値となり、重負荷と軽負荷との間で切り替わるとき零と前記所定の電流値との間で線形に変化する電流Im13を出力電圧Voutから生成する。前記電流Im12と前記電流Im13との和を供給電流Isup1とし、これを制御回路Ctrl1に供給する。

(もっと読む)

基準電圧回路

【課題】プロセス変動によるバラつき要因が少ない基準電圧回路の提供。

【解決手段】第1のMOSトランジスタと、ゲート端子が第1のMOSトランジスタのゲート端子に接続され、第1のMOSトランジスタのしきい値の絶対値とK値より高いしきい値の絶対値とK値を有する第2のMOSトランジスタと、第1のMOSトランジスタと第2のMOSトランジスタのしきい値の絶対値の差に基づく電流を流すカレントミラー回路と、カレントミラー回路の電流を流す第3のMOSトランジスタと、第3のMOSトランジスタのしきい値の絶対値とK値より高いしきい値の絶対値とK値を有し、カレントミラー回路の電流を流す第4のMOSトランジスタを備え、第3のMOSトランジスタと第4のMOSトランジスタのしきい値の絶対値とK値の差に基づく定電圧を基準電圧として出力する、構成とした。

(もっと読む)

電圧発生回路、定電圧回路および電圧発生回路の電流検出方法

【課題】低消費電流で低電圧な定電圧を安定して得られる定電圧回路を提供すること。

【解決手段】定電圧回路Aは、閾値電圧が極小でゲート長が特大のMOSトランジスタN1を用いて低電流を作り出し、基準電圧VREFを発生するMOSトランジスタN2、これと対を成してカレントミラー回路を構成する各MOSトランジスタN3、N4、N7、及びその他の各MOSトランジスタN5、N6の何れについても低閾値電圧タイプとし、且つMOSトランジスタN2、N3、N4、N7のゲート長LをMOSトランジスタP1、P2のゲート長Lよりも増大させている。これにより、各MOSトランジスタN2〜N7のドレイン電極−ソース電極間の電圧Vdsが0.1V以上の飽和領域で動作する電圧値を保ち、所望の低い基準電圧VREFを発生でき、カレントミラー回路を構成する際に正常動作が可能となり、定電圧出力端子4から低消費電流で低電圧な定電圧が得られる。

(もっと読む)

基準電圧回路

【課題】温度依存性が少ない低電圧(1.25V以下)の定電圧を発生する、基準電圧回路を提供すること。

【解決手段】二つのPN接合を有し、いずれかのPN接合に基づいた電圧Vkと、二つのPN接合の電圧の差に基づいた電流Ikと、を出力するバンドギャップ電圧発生回路と、電圧Vkを分圧する分圧回路と、を備え、分圧回路は入力する電流Ikにより分圧電圧を補正して、基準電圧として出力する、構成とした。

(もっと読む)

定電圧発生回路

【課題】定電圧発生回路の回路面積及び消費電流を削減しながら、負荷の直流的及び過渡的な変化に対する出力電圧の変化を小さくする。

【解決手段】FET4は、電圧源端子に接続されたドレインと出力端子に接続されたソースとを備える。FET2は、FET4のソースに接続されたゲートと、FET4のゲートに接続されたドレインとを有する。FET1は、FET2のソースと接地端子との間に設けられ、ダイオード接続されている。FET3は、電圧源端子とFET2のドレインとの間に接続され、そのドレインとソースとの間に所定の電位差を有し、第1の定電流源として機能する。FET5は、出力端子と接地端子との間に接続される。FET1及びFET5によりカレントミラー回路を構成することにより、FET5は第2の定電流源として機能する。

(もっと読む)

電圧生成回路およびパワーオンリセット回路

【課題】電源電圧が一時的に低下した場合であっても、その後電源電圧が上昇すれば基準電圧を素早く出力できるようにした電圧生成回路、および、リセット信号を素早く出力できるようにしたパワーオンリセット回路を提供する。

【解決手段】トランジスタMP5およびMP6が第1電源線N1およびノードN6間に直列接続されている。トランジスタMP5が起動電流Isをセンシングし、トランジスタMP6が基準電流Ipをセンシングする。電源電圧VDDが低下したとしても、両トランジスタMP5およびMP6には閾値電圧以上となる電圧がゲートソース間に与えられる虞がなくなり、充電回路8には充電電流Ioが充電されにくくなる。したがって、電源電圧VDDが再復帰して電源電圧が上昇したときには、トランジスタMP4が起動電流IsをノードN5に素早く供給でき、電流生成回路6は基準電流Ipを素早く生成できる。

(もっと読む)

半導体集積回路

【課題】電源の立ち上がりが遅くても安定に動作する半導体集積回路を提供する。

【解決手段】PチャンネルMOSトランジスタMP1のソース電極Sを電源に接続し、そのドレイン電極DにデプレッショントランジスタND1のドレイン電極Dを接続する。さらに、デプレッショントランジスタND1のソース電極Sを、抵抗R1を介して電位VSSとするとともに、PチャンネルMOSトランジスタとデプレッショントランジスタ双方のゲート電極Gを電位VSSとした電源起動回路部11を設ける。そして、PチャンネルMOSトランジスタMP1のドレイン電極DとデプレッショントランジスタND1のドレイン電極Dの相互接続点を定電流回路部12及びスタートアップ回路部14の電源ノードとして、定電流回路部12及びスタートアップ回路部14に動作電源を供給する構成とする。

(もっと読む)

バイアス回路及び増幅回路

【課題】低電圧までの広い電圧範囲で動作可能で、バイアス電流の温度係数を設定可能なバイアス回路及び増幅回路を提供する。

【解決手段】電流生成回路と、電圧生成回路と、を備えたことを特徴とするバイアス回路が提供される。前記電流生成回路は、接合部の面積の異なる2つのPN接合の順方向電圧の電圧差に基づいて第1の電流を生成し、前記2つのPN接合のうちの接合部の面積の小さいPN接合の順方向電圧に基づいて前記第1の電流の温度係数と異なる極性の温度係数を有する第2の電流を生成する。前記電圧生成回路は、前記第1の電流と前記第2の電流とを合成した電流から基準電圧を生成する。

(もっと読む)

電源回路

【課題】カレントミラー回路によって、複数の回路を電流駆動させる場合に、各回路の動作に対するばらつきを低減することができる電源回路を提供する。

【解決手段】FET1、2、3と、スイッチング素子であるスイッチ6〜9とで電源回路を構成している。FET1、2、3でカレントミラー回路を構成している。スイッチ6、7、8、9によって選択回路50が構成される。選択回路50は、スイッチ6〜9の切り替えにより、ミラー電流Ib2をオペアンプ4又はオペアンプ5のいずれかに供給し、さらに、ミラー電流Ib1をオペアンプ4又はオペアンプ5のいずれかに供給する。すなわち、ミラー電流Ib1とミラー電流Ib2とを入れ替えて交互に、オペアンプ4、5にそれぞれ供給する。

(もっと読む)

トンネル電流回路

【課題】消費電力の少ない基準電圧を発生する回路を、従来並みのサイズで提供することを目的とする。

【解決手段】

半導体接合に異なる電流密度の電流を流したときの差電圧に比例する電圧と、半導体接合に生ずる順方向電圧に比例する電圧とを加算して出力電圧とするバンドギャップリファレンス回路において、

前記差電圧が印加される第一のトンネル電流素子と、

第二のトンネル電流素子もしくは第二の複数のトンネル電流素子を直列接続した回路と、

前記第一のトンネル電流素子に流れる電流に比例した電流を前記第二のトンネル電流素子に流す手段によって、

上記「差電圧に比例する電圧」を発生させることを特徴とする。

(もっと読む)

基準電圧発生回路、駆動装置、プリントヘッド及び画像形成装置

【課題】発光素子の駆動装置に与える基準電圧として、温度特性が良好で、電源電圧の変動に対して変動の少ない基準電圧を生成する。

【解決手段】基準電圧Vrefを発生する基準電圧発生回路100において、バイポーラトランジスタのベース・エミッタ間電圧の負の温度係数に依存して生じる負の温度係数を持った第1カレントミラー回路120と、前記負の温度係数に依存して生じる正の温度係数を持った第2カレントミラー回路140とを備えている。そして、電流減算回路150により、第1カレントミラー回路110の出力電流から、第2カレントミラー回路140の出力電流を減じた電流を作成し、これと比例する基準電圧Vrefを出力する。

(もっと読む)

定電流源回路

【課題】動作の信頼性の向上を図る。

【解決手段】定電流源回路は、複数のPMOSトランジスタを含む第1カレントミラー回路11、複数のNMOSトランジスタを含む第2カレントミラー回路12を備え、正の温度特性を有する第1電流を発生する第1電流発生回路10と、前記複数のNMOSトランジスタの閾値電圧に依存し、負の温度特性を有する第1電圧が入力され、前記第1電圧と等しい第2電圧を出力するフィードバック回路21を備え、前記第2電圧に基づいて負の温度特性を有する第2電流を発生する第2電流発生回路20と、前記第1電流と前記第2電流とを加算することで、任意の温度特性を有する定電流を発生する電流合成回路30と、を具備する。

(もっと読む)

基準電圧回路

【課題】温度特性の良い基準電圧回路を提供する。

【解決手段】ゲートとソースが接続された第一のデプレッショントランジスタに流れる電流に基づいた電流を、同じしきい値の第三のデプレッショントランジスタに流して、ゲートとソース間に電圧を発生させ、ゲートとソースが接続された第二のデプレッショントランジスタに流れる電流に基づいた電流を、同じしきい値の第四のデプレッショントランジスタに流して、ゲートとソース間に電圧を発生させる。この二つの電圧の差電圧を基に基準電圧を発生させることで、温度変化に対して電圧変動の少ない基準電圧を得る。

(もっと読む)

電流源回路及びその調整方法

【課題】負荷回路の温度依存性を低減することができる電流源回路及びその調整方法を提供すること。

【解決手段】本発明の一態様である電流源回路100は、出力端子3、端子5、NチャネルMOSトランジスタNM1〜NMn、抵抗R1及び選択回路1を有する。NチャネルMOSトランジスタNM1〜NMnは、出力端子3及び端子5間に並列に接続され、ゲートに定電圧Viが印加され、それぞれ異なるディメンジョンを有する。抵抗R1は、NチャネルMOSトランジスタNM1〜NMnと端子5との間に接続される。選択回路1は、抵抗R1と出力端子3との間でNチャネルMOSトランジスタNM1〜NMnと直列に接続され、NチャネルMOSトランジスタNM1〜NMnと直列に接続され、NチャネルMOSトランジスタNM1〜NMnいずれかに選択的に出力電流を出力させる。

(もっと読む)

温度補償型基準電圧回路

【課題】ダイオードのアノード側電圧を用いて出力電圧を生成する基準電圧回路において、ダイオード温度非直線性を補正し、基準電圧回路の出力電圧の温度係数を小さくすること。

【解決手段】温度補償型基準電圧回路は、ダイオードのアノード側の電圧に基づいて出力電圧を生成する基準電圧回路と、第1のトランジスタおよび第2のトランジスタから成る差動対を有する温度補償回路とを備え、第1のトランジスタは定電流源とダイオードのアノード端子との間に接続され基準電圧回路の第1のノードの電圧をゲート電極に受け、第2のトランジスタは定電流源と基準電位点との間に接続され記基準電圧回路の第2のノードの電圧をゲート電極に受け、第1のノードの電圧の温度依存性は第2のノードの電圧の温度依存性よりも大きい。

(もっと読む)

基準電流出力装置及び基準電流出力方法

【課題】基準電流の大きさを温度勾配を維持したまま調整することができる基準電流出力装置を提供する。

【解決手段】基準電圧・電流出力回路12により基準電流i3’を出力し、変換出力回路14により、基準電圧・電流出力回路12から出力された基準電圧を調整用電流i4に変換して出力し、重畳出力部16により、基準電流i3’に調整用電流i4を重畳して重畳電流i6を出力する。

(もっと読む)

集積回路装置及び電子機器

【課題】電圧発生回路の電源電圧が低下した場合でも、その構成を変更することなく、該電圧発生回路が発生した電圧の変動を抑制できる集積回路装置等を提供する。

【解決手段】集積回路装置100は、第1の電圧V1と第2の電圧V2との差を動作電圧として第3の電圧V3を発生し、第3の電圧V3を出力電圧供給線に供給する電圧発生回路120と、動作電圧が低下したとき、所与の期間、出力電圧供給線PLOへの電流の流し込み又は該出力電圧供給線からの電流の引き込みを行う電圧変動抑制回路130とを含む。

(もっと読む)

1 - 20 / 196

[ Back to top ]