Fターム[5H730DD13]の内容

DC−DCコンバータ (106,849) | スイッチング部(主変換部の) (10,397) | スイッチング素子の接続態様 (1,078) | 並列接続 (141)

Fターム[5H730DD13]に分類される特許

1 - 20 / 141

半導体装置と、それを用いたインバータ、コンバータおよび電力変換装置

【課題】性能のばらつきが小さな半導体装置を提供する。

【解決手段】この半導体装置は、ノードN1,N2間に直列接続された第1のスイッチング素子(高耐圧のトランジスタQ1)および第2のスイッチング素子(抵抗素子R1および低耐圧のトランジスタQ2)と、第2のスイッチング素子に並列接続された第3のスイッチング素子(低耐圧のトランジスタQ3)とを含む。トランジスタQ2をオンさせるとトランジスタQ1がオンし、さらにトランジスタQ3をオンさせるとノードN1,N2間が導通状態になる。したがって、オン抵抗値の高い第1のスイッチング素子をオンさせて高耐圧のトランジスタQ1をオンさせるので、ターンオン時間のばらつきが小さくなる。

(もっと読む)

電子装置

【課題】

回路基板からの空間伝播する電磁ノイズの影響を抑え、寄生インダクタンスを低減したフィルタ回路を備え、十分にノイズ低減された電圧を出力することができる電子装置を提供する。

【解決手段】

上記課題を解決するために、本発明は、筐体101と、筐体内に設けられた回路基板132と、筐体に設けられた貫通孔を貫通し、回路基板の出力を外部に出力する出力端子122と、を備えた電子装置において、フィルタコンデンサ142aを有するフィルタ手段142と、出力端子と、筐体と、それらを接続する配線142b、142cで構成されるループを構成し、筐体に接続する配線142cを、出力端子に近い位置に接続することで、ループが小さくなるような構造とする。また、フィルタ手段と回路基板との間に、シールド102を設ける。

(もっと読む)

DC−DCコンバータの異常電流防止回路

【課題】回路規模が小さくて遅延が少なく且つ特性に与える素子バラツキの影響が小さいDC-DCコンバータの異常電流防止回路を提供する。

【解決手段】電流検出抵抗12を流れる電流を所定の基準電流と比較して過電流の有無を判定する電流コンパレータ30を備える。検出抵抗12の電圧は通常時(正常時)には負電圧であるが異常時に逆電流が生じた場合には正電圧が現れるようになる。電流コンパレータ30は検出抵抗12の電圧を監視し、検出抵抗12の電圧が負電圧の間はハイ出力をラッチ10を介してAND回路20に送ってPWM比較器9の出力信号がローサイド側スイッチ素子14,19に伝わるようにし、検出抵抗12の電圧が正電圧になると電流コンパレータ30の出力電圧はローになり、ローサイド側スイッチ素子14,19を強制的にOFFにする。

(もっと読む)

電力変換装置

【課題】DC−DCコンバータ装置において、スイッチング素子の冷却は放熱プレートへの放熱手段のみで、発熱量の大きいパワーMOSFETなどを並べて配置する場合は効率よく放熱するためには熱抵抗の低減や水冷装置の冷却経路の複雑化などの課題があった。

【解決手段】DC−DCコンバータ装置の電圧変換するためのインダクタ素子に流れる電流を制御する複数のスイッチング素子を金属製のケースよりも伝熱特性が良い金属製の放熱体に伝熱性を有する絶縁材を介して金属製のケースに固定する。隣接するスイッチング素子との間で熱の流れが交錯するのが少なくなって熱干渉が少なくなることで、熱拡散が良くなりスイッチング素子冷却効率をより高めることができる。

(もっと読む)

広域入力型スイッチング電源および風力発電装置

【課題】発電源から出力される変動幅の大きな電圧に対処し得るスイッチング電源および風力発電装置を提供する。

【解決手段】スイッチング電源1Aは、変圧器24と、変圧器24に生じた電圧波形を整流平滑する整流平滑回路25と、それぞれの一方の端が変圧器24の捲線比が異なる位置に接続された複数のインダクタを含む直列インダクタ23と、交流入力電圧を直流入力電圧に変換する三相整流ダイオード21と、直流入力電圧に対して並列に接続されるとともに、複数のインダクタの他方の端にそれぞれ接続された複数のコンバータを含む順次制御型ブリッジコンバータ22と、交流入力電圧の実効値に応じた制御信号を出力する入力電圧検出部31と、入力電圧検出部31から出力された制御信号に応じて複数のコンバータをスイッチング動作させるゲート順次制御部32と、を備える。

(もっと読む)

スイッチング制御装置

【課題】スイッチング回路全体の導通損失を低減しつつ、スイッチング回路を構成するスイッチング素子の損傷を防止する。

【解決手段】スイッチング制御装置10は、ハイ側スイッチング回路21又はロー側スイッチング回路22を非導通状態から導通状態に遷移させる際には、ユニポーラ型半導体素子をオフからオンに切り替えた後にバイポーラ型半導体素子をオフからオンに切り替え、導通状態から非導通状態に遷移させる際には、バイポーラ型半導体素子をオンからオフに切り替えた後にユニポーラ型半導体素子をオンからオフに切り替える。ハイ側スイッチング回路21又はロー側スイッチング回路22の導通状態において、ユニポーラ型半導体素子(SiC)の温度検出値TSiCが高温判定閾値Th以上である場合には、バイポーラ型半導体素子をオンに維持しつつユニポーラ型半導体素子をオンからオフに切り替える。

(もっと読む)

電源装置

【課題】力率を改善するため、オン抵抗が小さく、スイッチング速度が速いスイッチング素子を用いた電源装置において、スイッチング素子のソース−ドレイン間に寄生容量があると、スイッチング損失が発生する。スイッチング損失がない、効率を改善した電源装置を提供する。

【解決手段】電源装置は、整流回路に接続されるインダクタと正極端子との間に接続される第1整流素子と、前記第1整流素子の入力端子と負極端子との間に接続される第1スイッチング素子と、前記第1スイッチング素子に並列に接続される第2スイッチング素子及びトランスと、前記第2スイッチング素子と前記トランスの接続部と、前記正極端子との間に接続され、前記接続部から前記正極端子に向かう整流方向を有する第2整流素子と、前記トランスと前記正極端子との間に接続され、前記トランスから前記正極端子に向かう整流方向を有する第3整流素子を有する。

(もっと読む)

昇圧回路

【課題】損失を抑制すると共により迅速に昇圧を行なう。

【解決手段】チャージポンプ20からの出力電圧VCがトリガ電圧を超えると、スイッチ70がオンし、クロック信号供給回路30は出力電圧VCの振幅のクロック信号CKmos,CKBmosをチャージポンプ20に出力し、クロック信号供給回路40は出力電圧VCの振幅のクロック信号CKmosを用いてクロック信号CKcap,CKBcapを生成してチャージポンプ20に出力し、チャージポンプ20では、各トランジスタのゲートへ出力電圧VCの振幅のクロック信号CKmos,CKBmosが供給され、各キャパシタの他端へ立ち上がり時間の小さいクロック信号CKcap,CKBcapが供給される。これにより、昇圧回路10全体の損失を抑制すると共により迅速に出力電圧VCを目標出力電圧に昇圧することができる。

(もっと読む)

バスバーモジュール及び電力変換装置

【課題】より軽量化できるバスバーモジュールと、該バスバーモジュールを用いた電力変換装置を提供する。

【解決手段】バスバーモジュール1は、導体からなる複数のバスバー2と、複数のバスバー2の一部を封止してこれらを一体化する封止部材3とからなる。バスバー2は、封止部材3に封止された被封止部22と、被封止部22から延出し封止部材3から露出した露出部20と、パワー端子に接続される端子接続部21とを備える。露出部20の延出方向(Y方向)と封止部材3の長手方向(X方向)とは直交している。被封止部3は屈曲形成され、被封止部22の一部222は、X方向に延びている。封止部材3は、複数の被封止部22がY方向に重ならないように、複数のバスバー2を封止している。

(もっと読む)

半導体装置

【課題】体格及びコストの増大が抑制された半導体装置を提供する。

【解決手段】直流電源とグランドとの間に直列接続された2つの単位回路と、単位回路を制御する制御部と、を備え、2つの単位回路の中点に誘導性負荷が接続された半導体装置であって、2つの単位回路それぞれは、第1スイッチ素子と、第1スイッチ素子と逆並列接続された還流ダイオードと、還流ダイオードと第1スイッチ素子それぞれと並列接続されたバイパス部と、を有し、バイパス部は、直列接続された第2スイッチ素子及び抵抗を有し、制御部は、2つの単位回路の第1スイッチ素子をOFF状態にするデッド期間を挟んで、2つの第1スイッチ素子を交互にON状態とし、デッド期間において、一方の第1スイッチ素子がOFF状態からON状態に移行するまで、一方の第1スイッチ素子と並列接続された第2スイッチ素子をON状態にする。

(もっと読む)

スイッチング素子の駆動方法

【課題】並列接続されたスイッチング素子に均等に損失と発熱を分散させることができるスイッチング素子の駆動方法を提供すること。

【解決手段】スイッチング素子のスイッチング損失の異状増加をもたらす状態変化を検出するステップと、前記状態変化が検出されない場合に、前記各スイッチング素子の内の第1のスイッチング素子のオフタイミングと残る第2のスイッチング素子のオフタイミングとが一致するように前記第1、第2のスイッチング素子を駆動するステップと、前記状態変化が検出された場合に、前記第1のスイッチング素子と前記第2のスイッチング素子とを、それらの一方のオフタイミングが他方のオフタイミングよりも早くなるように駆動するステップとを含む。

(もっと読む)

スイッチング素子の駆動方法

【課題】並列接続されたスイッチング素子に均等に損失と発熱を分散させることができるスイッチング素子の駆動方法を提供すること。

【解決手段】スイッチング素子のスイッチング損失の異状増加をもたらす状態変化が検出されない場合、第1のスイッチング素子のオフタイミングと残る第2のスイッチング素子のオフタイミングとが一致するように第1、第2のスイッチング素子を駆動する第1の駆動ステップと、状態変化が検出された場合に、第1のスイッチング素子のオフタイミングと第2のスイッチング素子のオフタイミングとがずれるように第1、第2のスイッチング素子を駆動する第2の駆動ステップでは、第1のスイッチング素子が第2のスイッチング素子よりも早くオフする状態と、第2のスイッチング素子が第1のスイッチング素子よりも早くオフする状態とが前記周期ごとに交互に実現される。

(もっと読む)

スイッチング回路装置及びそれを有する電源装置

【課題】スイッチング時の電流の急激な変化を抑制しオン状態でのオン抵抗を抑制する。

【解決手段】電源回路内の第1のノードと第2のノードとの間に設けられるスイッチング回路装置であって,前記第1または第2のノードにインダクタが接続され,第1のノードと第2のノードとの間に設けられ第1のゲート幅を有する第1のトランジスタと,第1のノードと第2のノードとの間に第1のトランジスタに並列に設けられ第1のゲート幅より大きい第2のゲート幅を有する第2のトランジスタと,電源回路の出力電圧に応じて生成される制御信号に応答して,第1のトランジスタをオン,オフに駆動する第1の駆動信号と,第2のトランジスタをオン,オフに駆動する第2の駆動信号とを,時間的にずらして出力する駆動信号生成回路とを有する。

(もっと読む)

パワーモジュール及び該パワーモジュールを搭載したハイブリッド車又は電気自動車

【課題】クロスポイントの高いパワー半導体素子を使用して低電流駆動する場合に、その損失をより低減することが可能なパワーモジュールを得る。

【解決手段】パワーモジュール(14)は、パワー半導体素子(3a、4a、3b、4b)と、パワー半導体素子の温度を調整する温度調整装置(7)と、パワー半導体素子の駆動電流を検知する電流検知装置(9)と、電流検知装置(9)によって検知された前記駆動電流に基づいて、温度調整装置(7)を制御する制御装置(11)と、を備えて構成される。

(もっと読む)

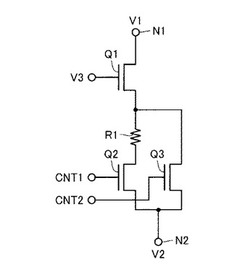

半導体装置と、それを用いたインバータ、コンバータおよび電力変換装置

【課題】ターンオン時間のばらつきが小さな半導体装置を提供する。

【解決手段】この半導体装置は、ノードN1,N2間に直列接続された高耐圧、高GmのトランジスタQ1および低耐圧、低GmのトランジスタQ2と、トランジスタQ2に並列接続された低耐圧、高GmのトランジスタQ3とを含む。トランジスタQ2をオンさせるとトランジスタQ1がオンし、さらにトランジスタQ3をオンさせるとノードN1,N2間が導通状態になる。したがって、低耐圧のトランジスタQ2をオンさせて高耐圧のトランジスタQ1をオンさせるので、ターンオン時間のばらつきが小さくなる。

(もっと読む)

半導体装置と、それを用いたインバータ、コンバータおよび電力変換装置

【課題】ターンオン時間のばらつきが小さな半導体装置を提供する。

【解決手段】この半導体装置は、ノードN1,N2間に直列接続された高耐圧、高GmのトランジスタQ1および低耐圧、低GmのトランジスタQ2と、トランジスタQ2に並列接続された低耐圧、高GmのトランジスタQ3とを含む。トランジスタQ2をオンさせるとトランジスタQ1がオンし、さらにトランジスタQ3をオンさせるとノードN1,N2間が導通状態になる。したがって、低耐圧のトランジスタQ2をオンさせて高耐圧のトランジスタQ1をオンさせるので、ターンオン時間のばらつきが小さくなる。

(もっと読む)

スイッチング電源装置およびスイッチング電源装置の制御方法

【課題】部品コストおよび実装面積を低減しつつリカバリ電流の発生を抑制することができるスイッチング電源装置を提供することである。

【解決手段】本発明にかかるスイッチング電源装置は、電源P_INとノードLXとの間に接続された主スイッチ素子SW1と、電源P_INとノードLXとの間に接続された補助スイッチ素子SW2と、補助スイッチ素子SW2を介してノードLXに流れる電流を制限する電流制限手段R1と、接地電源とノードLXとの間に接続されたスイッチ素子SW3と、ノードLXと出力端子P_OUTとの間に設けられた平滑回路3と、制御回路4とを備える。制御回路4は、主スイッチ素子SW1をオン状態とする前に、補助スイッチ素子SW2をオン状態とすることでスイッチ素子SW3と並列に生成された寄生ダイオードD3のノードLX側をプルアップする。

(もっと読む)

車両用電力供給システム

【課題】 高圧バッテリ200と電磁サスペンション装置の電動モータ40とを接続する双方向性のDC/DCコンバータ100の過熱を防止する。

【解決手段】 DC/DCコンバータ100の1次側スイッチング回路110および2次側スイッチング回路120は、それぞれスイッチングする部位に、2つのスイッチング素子Sを並列に接続したスイッチング素子対SPを備えている。スイッチ制御部140は、各スイッチング素子対SPの片側のスイッチング素子Sに流れる電流と、1次側トータル電流i1と、2次側トータル電流i2とに基づいて、スイッチング素子対SPの故障を検出する。

(もっと読む)

レギュレータ回路

【課題】ショットキーバリアダイオードを使用することなく、デッドタイムによる効率低下を改善したレギュレータ回路を提供する。

【解決手段】電源線とインダクタとの間に接続される第1のトランジスタと、第1のトランジスタのソースと基準電圧線との間に接続される第2のトランジスタと、第1のトランジスタのソースと負荷との間に接続される第3のトランジスタとを備え、デッドタイムにおいて第3のトランジスタのゲートにしきい値電圧未満であってかつ略しきい値電圧である電圧をゲート電圧として供給することで、デッドタイムに、インダクタ、負荷、及び第3のトランジスタによる電流経路で電流を流し続け、デッドタイムによる効率低下を改善する。

(もっと読む)

基準電圧発生回路及びそれを用いた電源装置

【課題】温度依存性をもたない基準電圧を発生させる。

【解決手段】SOI層膜厚のみが異なることで互いにしきい値電圧が異なる2つの完全空乏型SOI−MOSFETMN1,MN2について、ソース及びボディを接地し、ゲート及びドレインを定電流源CCS1,CCS2とボルテージフォロア回路Amp1−1,1−2の入力端子に接続し、ボルテージフォロア回路Amp1−1,1−2の出力端子に第1抵抗R1−1,R1−2と第2抵抗R2−1,R2−2を直列に接続する。第2抵抗R1−2を接地し、第1抵抗R2−1と第2抵抗R2−1の間の端子を差動増幅器Amp2の非反転入力端子に接続する。第2抵抗R2−2を差動増幅器Amp2の出力端子に接続し、第1抵抗R1−2と第2抵抗R2−2の間の端子を差動増幅器Ampの反転入力端子に接続する。差動増幅器Amp2の出力電圧を基準電圧Vrefとして出力する。

(もっと読む)

1 - 20 / 141

[ Back to top ]