Fターム[5J022AA01]の内容

アナログ←→デジタル変換 (13,545) | A/D変換器の型式 (1,573) | A/D非特定 (659)

Fターム[5J022AA01]に分類される特許

101 - 120 / 659

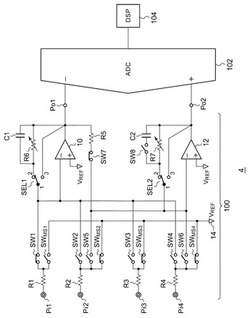

入力セレクタおよび信号処理回路

【課題】さまざまな入力形式の信号に柔軟に適応可能な汎用性の高い入力セレクタを提供する。

【解決手段】第1抵抗R1〜第4抵抗R4は、それぞれの第1端子が対応する入力ポートPi1〜Pi4に接続される。第1スイッチSW1〜第4スイッチSW4はそれぞれ、対応する抵抗と第1演算増幅器10の反転入力端子の間に設けられる。第5スイッチSW5、第6スイッチSW6はそれぞれ、対応する抵抗と、第2演算増幅器12の反転入力端子の間に設けられる。第5抵抗R5および第7スイッチSW7は第1演算増幅器10の出力端子と第2演算増幅器12の反転入力端子の間に直列に設けられる。第6抵抗R6は第1演算増幅器10の出力端子と反転入力端子の間に設けられ、第7抵抗R7は第2演算増幅器12の出力端子と反転入力端子の間に設けられる。

(もっと読む)

アナログ・ディジタル変換装置

【課題】画像処理などに利用可能な高速AD変換装置を提供する。

【解決手段】複数個のAD変換器11を個数分のクロック周波数で駆動させるAD変換装置1において、各AD変換器の出力をFFT処理し、その演算結果から基準AD変換器(ADC0)と他のAD変換器(ADC1、ADC2、ADC3)とのオフセットエラー、ゲインエラー、位相エラーを算出する。オフセットエラーは周波数がfs/2のFFT演算結果から算出し、ゲインエラーは周波数がfin、fs/2+fin、またはfs/2−finのFFT演算結果から算出し、位相エラーは周波数がfs/2−finまたはfs/2+finのFFT演算結果から算出する。

(もっと読む)

AD変換装置およびAD変換装置の調整方法

【課題】入出力変換特性の調整に適したノイズ環境下で調整可能なAD変換装置を得る。

【解決手段】入力信号をAD変換した結果である複数のAD変換値をAD変換値保存部9へ格納するAD変換器7と、AD変換値保存部9に格納された複数のAD変換値の平均値を計算し平均値保存部10に格納する平均値演算部18と、AD変換値保存部9に格納された複数のAD変換値の分散を計算し分散保存部11に格納する分散演算部19と、平均値及び分散に基づいてAD変換値の不確かさを判定する不確かさ判定部20と、AD変換値保存部9に格納された複数のAD変換値に正規分布検定を行い、正規性の有無を判定する正規分布検定部17と、不確かさ判定部20において不確かさが所定の許容値より小さいと判定され、且つ正規分布検定部17において正規性を有すると判定された場合に、平均値に基づいてAD変換器7の入出力変換特性の調整を行う調整処理部23とを備える。

(もっと読む)

A/D変換器およびそれを使用した受信装置

【課題】A/D変換器を構成するサンプル/ホールド回路、コンパレータを低消費電力化すること。

【解決手段】アナログ入力信号をクロック信号に応答してサンプルしてホールドするサンプル/ホールド回路(SHC)とその回路からのホールド出力信号の信号レベルを弁別するコンパレータ(COP)を含む。コンパレータは、サンプル/ホールド回路からのホールド出力信号を増幅するプリアンプ(AMP)、プリアンプから生成される差動出力信号をラッチするラッチ回路(LCH)、プリアンプから生成される差動出力信号のレベル差に応答してプリアンプのバイアス電流の電流値を制御するバイアス制御回路(BCC)を含む。差動出力信号のレベル差が小さい時にはバイアス制御回路はプリアンプのバイアス電流を大きな電流値に制御して、差動出力信号のレベル差が大きい時にはバイアス制御回路はプリアンプのバイアス電流を小さな電流値に制御する。

(もっと読む)

サンプルホールド回路及びA/D変換装置

【課題】本発明は、サンプルホールド回路及びA/D変換装置に係り、ホールド出力を行ううえでオペアンプの入力オフセット分の除去性能を向上させることにある。

【解決手段】ホールド出力を行うオペアンプを備えるサンプルホールド回路において、所定複数の異なるタイミングで入力電圧をサンプリングするサンプリングキャパシタと、サンプリングキャパシタでサンプリングされた各入力電圧を加減算する加減算手段と、加減算手段により各入力電圧が加減算された後、該加減算により得られる電圧に含まれるオペアンプの入力オフセット電圧分を除去するオフセット電圧除去手段と、を備え、オペアンプは、オフセット電圧除去手段によりオペアンプの入力オフセット電圧分が除去された電圧をホールドして出力する。

(もっと読む)

信号処理装置

【課題】電子制御装置から要求信号を受けてからデジタルデータを電子制御装置に送信する迄に生じる遅延時間を短くする。

【解決手段】通信装置24が電子制御装置10から要求信号を受信すると、メモリ23に記憶されたデジタルデータを電子制御装置10に送信する。また、通信周期推定部25は、前々回に要求信号を受けたタイミングと前回に要求信号を受けたタイミングとに基づいて、次回に要求信号を受けるタイミングを推定する。タイミング発生部26は、次回に要求信号を受けるタイミングから処理時間を引いたタイミングを求め、そのタイミングになるとA/D変換器22によりセンサ信号をA/D変換させる。そのA/D変換されたセンサ信号(デジタルデータ)はメモリ23に記憶され、次回の送信に用いられる。

(もっと読む)

AD変換回路

【課題】本発明は、内部に小規模の回路を追加し、この回路を利用して、自身が備えるDACのリニアリティエラーを測定することのできるAD変換回路を実現することを目的とする。

【解決手段】本発明は、外部から入力したアナログ信号から、自身のレジスタのデジタルコードに応じたアナログ信号を出力するDAコンバータの出力を、減算して出力する減算器と、この減算器の出力値の正負に応じて、それぞれ1または0のデータを出力するコンパレータと、このコンパレータの出力に応じて、デジタルコードを前記DAコンバータへ出力するとともに、前記デジタルコードを外部に出力する逐次比較レジスタロジック部と、を備えたAD変換回路において、前記減算器の出力を積分し前記コンパレータに出力する積分器と、前記コンパレータの出力に基づいて前記DAコンバータの微分非直線誤差を検出するとともに、前記DAコンバータにデジタルコードを出力するDNL測定部と、を備えたことを特徴とする。

(もっと読む)

信号処理回路及び信号処理方法

【課題】高サンプリングレートにおいて高精度でDC信号をAD変換可能な信号処理回路を提供する。

【解決手段】入力信号電圧に応じた振動幅で振動する電圧波形を生成する変調回路と、電圧波形を受け取る入力端と出力端との間を容量結合又は誘導結合するAC結合回路と、AC結合回路の出力端に現れる出力電圧をAD変換しデジタル値を出力するAD変換回路と、デジタル値に基づいて入力信号電圧のAD変換値を求める演算回路とを含む。

(もっと読む)

車載制御装置、車載制御装置の検査方法

【課題】異常検出のための特別な回路を設けることなく、AD変換器の異常を検出することのできる車載制御装置を提供する。

【解決手段】入力されたアナログ電圧をデジタル値に変換するAD変換器と、車両の制御動作を記述したプログラムを実行する演算部と、演算部の指示にしたがって時間を計測するタイマと、を備え、演算部は、AD変換器が変換を実行するために要する変換所要時間、または変換を実行する時間間隔に相当する変換周期のうち少なくともいずれかを、タイマを用いて計測し、変換所要時間または変換周期の計測値が、あらかじめ定められた規定範囲内に収まっているか否かにより、AD変換器が正常に動作しているか否かを検査する。

(もっと読む)

パイプライン型A/Dコンバータ

【課題】熱雑音および演算増幅器に要求されるオープンループゲインを大きくさせることなく、入力レンジおよびディジタル出力信号のビット数を大きくすることのできるパイプライン型A/Dコンバータを提供する。

【解決手段】サンプルホールド用のコンデンサの個数MをN分割し、さらに基準電圧をN倍することで、基準電圧を加減算するために用いることが出来るコンデンサの数を増加させて入力レンジを広げ、ディジタル出力信号のビット数を大きくする。この場合、全てのコンデンサでアナログ信号をサンプルするため、コンデンサを分割する前後で熱雑音を劣化させない。さらに、アナログ信号を増幅するための帰還素子として用いるコンデンサと、残りのコンデンサとの比はコンデンサを分割する前後で変わらないため、演算増幅器128に要求されるオープンループゲインを増加させない。

(もっと読む)

ADコンバータのクロック位相を調整可能なシステム

【課題】クロック雑音干渉が存在するときの性能を改善したアナログ/デジタルコンバータを提供する。

【解決手段】クロック位相シフタ85を備え、干渉雑音に対して最適なサンプリング時間間隔でコンバータが動作できるように制御される。この位相シフタは、複数のサンプリングクロック位相を生成するための装置と、最適なクロック位相を選択するために複数の位相入力に接続されるマルチプレクサ82とを備え、最適なクロック位相を1つ選択しアナログ/デジタルコンバータを動作させる。

(もっと読む)

マルチチャネルサンプルホールド回路及びそれを用いたAD変換器

【課題】低消費電力化と高速及び高精度化とを両立する。

【解決手段】本発明に係るサンプルホールド回路500は、SC群100、200、300及び400のそれぞれに対して、複数の入力端子45〜48のいずれかの電圧に相当する電荷を当該SC群に含まれる容量に蓄積させるサンプリング動作と、当該SC群に含まれる容量に蓄積されている電荷を保持させるホールド動作と、当該SC群に含まれる容量に蓄積されている電荷を出力端子51に出力する転送動作とを、サンプリング動作、ホールド動作及び転送動作の順番で実行し、連続する期間のそれぞれにおいて、SC群100、200、300及び400ののうち、1つのSC群に対してサンプリング動作を実行し、他の1つのSC群に対してホールド動作を実行し、他の1つのSC群に対して転送動作を実行する。

(もっと読む)

AD変換回路

【課題】タイミング設計が容易となり、補正フィルタの規模増大を防止できるようにする。

【解決手段】入力された信号を、第1の周期で、かつ、互いに異なったタイミングでデジタル信号に変換し、第1および第2のデジタル信号列を生成するADコンバータ11、12と、第2のタイミングの基準値からの誤差を補正する補正フィルタ30と、ADコンバータ11、12の出力デジタル信号列を受け取り、同一のタイミングで、第1および第2の同位相化デジタル信号列として出力するFIFO21、22を備える。補正フィルタ30は、第1および第2の分解化補正フィルタ32,33を含み、前記第1の同位相化デジタル信号列と、前記第2の同位相化デジタル信号列が第1の分解化補正フィルタ32を通過した信号列とを加算した、第1の補正済みデジタル信号列を生成するとともに、第2の分解化補正フィルタ33を通過した第2の補正済みデジタル信号列を生成する。

(もっと読む)

入力モジュール

【課題】演算処理部の出力に異常レベルのノイズが重畳する状態において、その異常の要因がアナログ入力信号に重畳されたノイズによるものなのか、入力モジュールの故障によるものかを判定可能とした入力モジュールを実現する。

【解決手段】アナログ入力信号に重畳するノイズをローパスフィルタで軽減してADコンバータによりデジタル変換し、ファームウェアフィルタを備える演算処理部で処理して上位装置に出力する入力モジュールにおいて、

前記アナログ入力信号に重畳するノイズが設定された所定の閾値の範囲か否かを検出してこのノイズのレベル異常を判定する第1監視部を具備する入力ノイズ検出部と、

前記演算処理部の出力より前記アナログ信号のノイズレベルを推定演算し、これが前記所定の閾値の範囲か否かを検出してレベル異常を判定する第2監視部と、

前記第1監視部の判定出力と前記第2監視部の判定出力とを入力し、異常原因を特定して上記上位装置に出力する診断部と、

を備える。

(もっと読む)

AD変換回路、及び、誤差補正方法

【課題】AD変換誤差を確実に補正し、アナログ信号をより高精度でデジタルデータに変換可能なAD変換回路、および、誤差補正方法を提供する。

【解決手段】入力電圧Vinをデジタルデータに変換し、このデジタルデータの誤差を補正するマイコン10において、電圧変動を含まない標準電源が供給された場合にAD変換器15が基準電圧VrefをAD変換することで得られる第1の変換値と、通常動作用の電源Vccが供給された状態でAD変換器15が基準電圧VrefをAD変換して得られる第2の変換値とをもとに、電源Vccが有する電圧変動ΔVccを算出し、算出した電圧変動ΔVccに基づいて、AD変換器15がアナログ信号をAD変換した変換値を補正する。

(もっと読む)

制御装置

【課題】A/D変換器に簡便なA/D変換処理をさせると共に、電気部品を制御するに必要なデジタル信号データの全てを精度よく得ることのできる制御装置を提供する。

【解決手段】制御部12が、A/D変換器11に対して、複数のセンサSR1〜SR8のうちで、電気部品の動作を制御するために制御部が実行すべき処理において必要とされるセンサからのアナログ信号のみをA/D変換させることにより、処理において必要とされるデジタル信号データのみを得て、処理において必要とされるデジタル信号のみを読み出す。

(もっと読む)

A/D変換装置

【課題】装置構成に要する費用が嵩んだり、装置が大型化することを防止し、変換周期を短縮する。

【解決手段】A/D変換装置10の記憶部12は、アナログ信号が入力される複数のチャンネルCH1,…,CHn毎に対応付けられた複数の基準電圧Vrefを予め記憶する。電圧選択部13は、記憶部12に記憶された複数の基準電圧Vrefの何れか1つを選択して基準電圧出力部14から出力させ、全チャンネルCH1,…,CHnのA/D変換が完了する毎に基準電圧Vrefの選択を変更して、全て基準電圧Vrefを順次出力させる。A/D変換器15は、全ての基準電圧Vrefと全チャンネルCH1,…,CHnとの組み合わせ毎のデジタル信号のうち、予め記憶部12に記憶された基準電圧Vrefと各チャンネルとの対応付けに等しい組み合わせのデジタル信号を出力する。

(もっと読む)

様々なレートによる効率的な同時サンプリング

アナログ入力二重化装置およびアナログ入力二重化方法

【課題】アナログ入力二重化構成において、現地調整時には稼動側のみについて現地調整を実施すれば足り、片側故障時のモジュール交換の際には現地調整を不要として作業効率を向上させること。

【解決手段】入力するアナログ値の範囲とデジタル値の範囲の対応関係を稼動側と待機側の両方に共通の設定値として設定し、稼動側と待機側のそれぞれでA/D変換誤差を修正するための校正値を入力し、該校正値と前記対応関係から調整用スケール変換データを計算し、稼動側において、外部機器の特性に合わせるための機器調整値を入力し、該機器調整値を稼動側の調整用スケール変換データによってスケール変換して補正値を算出して待機側へ送信し、待機側において、受信した補正値と待機側の調整用スケール変換データを用いて、待機側の機器調整値を計算し、入力した計測値を夫々が保持する機器調整値を用いて修正する。

(もっと読む)

信号処理装置、デジタル出力マイクロホンユニット

【課題】広い温度範囲内で周囲の温度変化に対するデジタル出力の変動を安定化させる。

【解決手段】 マイクロホン(1)によって音から変換されたアナログ電気信号をデジタル電気信号にアナログ−デジタル変換して出力する信号処理装置(13)において、マイクロホン(1)から出力されたアナログ電気信号を増幅するプリアンプ(15)と、プリアンプ(15)から出力されたアナログ電気信号を基準電圧Vrefと比較してアナログ−デジタル変換するアナログ−デジタル変換器(12)と、基準電圧Vrefを生成してアナログ−デジタル変換器(12)に供給する基準電圧生成回路(14)と、を備え、基準電圧生成回路(14)は、信号処理装置(13)を構成する電気回路素子の中でその他の電気回路素子と比べてその電気的性質の温度依存性が高い素子を備え、この素子の両端子間電圧に応じた基準電圧Vrefを生成する。

(もっと読む)

101 - 120 / 659

[ Back to top ]