Fターム[5J022AA01]の内容

アナログ←→デジタル変換 (13,545) | A/D変換器の型式 (1,573) | A/D非特定 (659)

Fターム[5J022AA01]に分類される特許

81 - 100 / 659

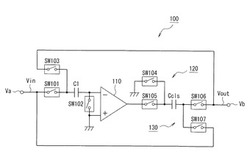

スイッチトキャパシタ回路、サンプル・ホールド回路、および、A/D変換装置

【課題】CLS技術を用いたスイッチトキャパシタ回路に適用する演算増幅器の動作速度に関する所要水準を抑制しつつ比較的振幅の大きい入力信号にも適合するという優位性を維持したスイッチトキャパシタ回路等を実現する。

【解決手段】コンデンサCclsおよびスイッチSW104、SW105、SW106を含んでCLS回路120を構成する一方、スイッチSW107が介挿された導体部、および、SW104、SW105、SW106により切替え回路130を構成し、この切替え回路130によってレベルシフト用コンデンサCclsを、サンプリングフェーズで、アナログ入力信号Vinで充電されるように接続し、レベルシフトフェーズで、アナログ信号出力端子Vbと演算増幅器110の出力端子との間に介挿されるように接続関係を切替えるように構成する。

(もっと読む)

信号処理装置、及び電源装置

【課題】本発明は、信号処理結果の精度を維持しつつ、信号処理の応答性を改善する。

【解決手段】信号処理装置100は、複数の入力信号に基づいて生成される情報を、複数の入力信号からなる組と入力信号の取得順序(0〜(N−1))とに対応させて記憶するデータレジスタ部30と、複数の入力信号に基づいた情報を生成するAD変換部20と、複数の入力信号からなる入力信号の組を示す識別情報(0〜(M−1))と、組を成す複数の入力信号の取得順序を示す順序情報(0〜(N−1))とに対応させて、入力信号に基づいて生成された情報をデータレジスタ部30に記憶させる制御部90と、複数の入力信号の組を成す入力信号に対応する記憶された情報に対するフィルタ処理を行うフィルタ処理部40とを備える。

(もっと読む)

AD変換装置

【課題】差分増幅回路を用いたAD変換装置において、量子化誤差の蓄積を抑圧するように補償して、AD変換出力信号のSNRを従来例に比較して大幅に改善する。

【解決手段】差動増幅回路1AとAD変換器3Aとデジタル復調回路4Aとを備えたAD変換装置において、減算器42,52は、AD変換器3Aからのデジタル信号をアナログ信号にDA変換するDA変換器41,51と、差動増幅回路1Aからのアナログ出力信号からDA変換器41,51からのアナログ信号を減算して、AD変換器3Aの量子化誤差を示す減算結果信号を出力する。AD変換器30は、減算器42,52からの減算結果信号をデジタル信号にAD変換し、加算器43,53は、AD変換器3Aからのデジタル信号にAD変換器30からのデジタル信号を加算することにより量子化誤差が実質的にゼロとなるように補償して、加算結果信号をデジタル復調回路4Aに出力する。

(もっと読む)

アナログデジタル変換装置

【課題】デジタル回路とアナログ回路とを、単一電源電圧かつ低消費電力で混載することを可能にする。

【解決手段】A/D変換部32は、電源端子と接地端子との間に接続され、入力電圧に応じてハイレベルの出力またはローレベルの出力を生成するデジタル信号生成部32aと、接地端子とデジタル信号生成部32aとの間における電位差としてのオフセット電圧Vofsを発生するオフセット電圧発生部32bとを有する。ここで、オフセット電圧発生部32bは、デジタル信号生成部32aに印加される電源電圧を低減すべく、オフセット電圧Vofsを発生する。

(もっと読む)

AD変換システム

【課題】AD変換部の数が増加しても回路規模の増大を最小限に抑えるAD変換システムを提供する。

【解決手段】複数のアナログ信号をシリアルなデジタル信号に変換するAD変換システムは、複数のアナログ信号の各々を同一タイミングでAD変換する複数のAD変換部と、複数のデジタル信号を並直列変換してシリアルなデジタル信号を出力する並直列変換部と、制御信号を並直列変換部に供給する制御部とを備える。並直列変換部は、「AD変換システムを構成するAD変換部の数+1」個のDフリップフロップ(D−FF)が直列に接続して構成され、制御部からの制御信号が入力されるシフト回路と、AD変換部と同数のゲート回路から構成され、各段のD−FFの出力信号に応じて、各ゲート回路に入力されたデジタル信号の出力を制御する並直列変換回路と、最前段のD−FF及び最後段のD−FFの各出力信号に基づいて、AD変換部の動作許可信号を出力するAD変換動作制御部を有する。

(もっと読む)

A/D変換回路および受信機

【課題】大きなバイアス電流を用いることなく高速動作および低消費電力を可能とするAD変換回路を実現する。

【解決手段】本発明の一態様としてのA/D変換回路は、第1サンプリング容量と、第1サンプリングスイッチと、バッファ回路と、第2サンプリング容量と、第2サンプリングスイッチと、第1変換手段と、第1リセットスイッチと、第2リセットスイッチとを備える。第1および第2サンプリングスイッチをオンにして、第1サンプリング容量に電圧をトラックし、バッファ回路を介して第2サンプリング容量にバッファ電圧をサンプルする。第1サンプリングスイッチをオフにして電圧をホールドする。第2サンプリングスイッチをオフにし、第1変換手段により第2サンプリング容量から電圧を読み出してA/D変換する。その後、第1および第2リセットスイッチにより、第1および第2サンプリング容量をリセットする。

(もっと読む)

半導体集積回路装置

【課題】消費電流を増加させることなく短時間で、アナログ信号をデジタル信号に高精度に変換する。

【解決手段】デルタシグマ型A/D変換器2において、デジタルフィルタ111によるA/D変換が開始される。デジタルフィルタ111のA/D変換時間が約1/2経過すると、デジタルフィルタ112がA/D変換を開始する。デジタルフィルタ111からA/D変換結果K1が出力されると、デジタルフィルタ111はリセットした後、再びA/D変換を開始する。そして、デジタルフィルタ111のA/D変換時間の約1/2が経過すると、デジタルフィルタ112のA/D変換が終了し、A/D変換結果K2が出力される。このように、A/D変換結果の出力間隔を、1つのデジタルフィルタによる構成と比べて2倍とすることにより、消費電流を増加させることなくA/D変換を高速化する。

(もっと読む)

音声処理装置

【課題】大きなヘッドルームを設定したアナログ信号をデジタル処理回路で増幅したときのS/N特性を向上する。

【解決手段】音声処理系統11〜1nは、アナログ増幅回路21〜2n、AD変換回路31〜3n、デジタル処理回路41〜4nを有する。第1の音声処理系統11に入力されたアナログ信号は、分配スイッチ62を介して第1と第2の音声処理系統のアナログ増幅回路21、22に分配される。分配されたアナログ信号は、26dBに設定されたヘッドルームに基づいてアナログ増幅回路21、22で増幅され、AD変換回路31、32で−26dBFSのデジタル信号に変換される。これらのデジタル信号は、切換スイッチ71、72を介して、デジタル信号の加算・処理回路40に入力される。これらのデジタル信号は、デジタル信号の加算・処理回路40において加算、増幅され、一般的基準の出力レベルである−20dBFSのデジタル信号として出力される。

(もっと読む)

AD変換器及びAD変換回路の電圧制御方法

【課題】AD変換の際のアナログ入力振幅の収束時間を短縮させつつ、AD変換回路が想定する量子化分解能を最大限に活用することが可能なAD変換器を提供する。

【解決手段】アナログ信号からデジタル信号に変換するAD変換回路へ、アナログ信号の入力の振幅を可変させて出力するAGC回路と、AGC回路が出力するアナログ信号の出力範囲と、既定の電圧の範囲と比較して、該比較の結果に基づいてAGC回路が出力するアナログ信号の出力範囲を制御する第1検波部と、を備える、AD変換器が提供される。これにより、AD変換の際のアナログ入力振幅の収束時間を短縮させつつ、AD変換回路が想定する量子化分解能を最大限に活用することが可能なAD変換器を提供することができる。

(もっと読む)

集積回路装置及び電子機器

【課題】センサーデバイスのチャネル信号が第1、第2信号で構成される場合に第1、第2信号の差分に対応する信号の精度の高いA/D変換を実現する集積回路装置等の提供。

【解決手段】集積回路装置は、センサーデバイスからの第1信号SG1が第1期間において入力され、第1信号SG1とペアーとなってセンサーデバイスのチャネル信号を構成する第2信号SG2が第2期間において入力され、第1信号SG1と第2信号SG2の差分に対応する信号を出力する増幅回路と、増幅回路の出力信号についてのA/D変換を行うA/D変換器を含む。増幅回路は、増幅回路が有する演算増幅器のオフセット電圧をキャンセルするスイッチドキャパシター回路により構成される。

(もっと読む)

音声伝送システム

【課題】多数段の音声処理装置を経由しても信号の劣化が少ない音声伝送システムを提供する。

【解決手段】ルーター1に、(1)入力されたアナログ音声信号をデジタル信号に変換するAD変換装置2、(2) デジタル音声信号に種々の処理を加える複数の音声処理装置3、(3) 処理されたデジタル信号を任意のアナログ音声信号に変換して出力するDA変換装置4を接続する。ルーター1に、他の音声処理システム10に接続される外部端子と、本システムを構成する各機器を制御するコンソール11を接続する。各装置2,3,4とルーター間で授受する信号を、32Bit浮動小数点フォーマットとする。

(もっと読む)

半導体集積回路およびそのテスト方法

【課題】サンプリングクロックの位相ノイズがDACおよびADCの変換特性に与える影響を検出することができ、ループバックテストのテスト品質を向上させることができる半導体集積回路およびそのテスト方法を提供する。

【解決手段】半導体集積回路は、サンプリングクロックに同期して動作し、デジタル信号をアナログ信号に変換するDACと、サンプリングクロックに同期して動作し、アナログ信号をデジタル信号に変換するADCと、基準クロックに基づいて、位相ノイズ特性の異なる第1および第2のサンプリングクロックを発生するサンプリングクロック発生回路と、DACから出力されるアナログ信号をADCに入力、あるいはADCから出力されるデジタル信号をDACに入力するループバックテスト時に、DACおよびADCの一方に第1のサンプリングクロックを供給し、他方に第2のサンプリングクロックを供給するサンプリングクロック切替回路とを備える。

(もっと読む)

集積回路装置及び電子機器

【課題】センサーデバイスからの検出信号の精度の高いA/D変換を実現できる集積回路装置及び電子機器等の提供。

【解決手段】集積回路装置は、電源電圧VDDAを生成する電源回路60と、電源回路60から電源電圧VDDAが供給され、供給された電源電圧VDDAに基づいて動作し、電源電圧VDDAにより規定されるA/D変換範囲で、センサーデバイス30からの検出信号に対応する信号についてのA/D変換を行うA/D変換器ADCと、電源回路60から電源電圧VDDAが供給され、供給された電源電圧VDDAをセンサーデバイス30に供給する電源端子PVDAを含む。

(もっと読む)

アナログ−デジタル変換回路、照度センサ、近接センサ、測距センサ、携帯電話、およびデジタルカメラ

【課題】微小なアナログ入力電流を高い精度で検出することが出来るアナログ−デジタル変換回路を提供する。

【解決手段】アナログ−デジタル変換回路1は、アナログ入力電流Iinをデジタル変換してデジタル値ADCOUTを得るADC2(アナログ−デジタル変換部)を備えるアナログ−デジタル変換回路であって、所定期間毎に得られた所定個数のデジタル値ADCOUTを記憶するレジスタユニットと、レジスタユニットが記憶しているデジタル値ADCOUTを全て加算することによって加算値ADD[N]を算出する加算器と、加算値ADD[N]と所定の閾値とを比較するとともに、当該比較の結果に従ってデジタル出力信号DOUTを出力する比較回路5とを備える。

(もっと読む)

スイッチトキャパシタ型回路及びそれを用いたAD変換回路

【課題】消費電力を増大させることなく、高精度な基準電圧の下で動作するスイッチトキャパシタ型回路を提供する。

【解決手段】(1)第1のスイッチトキャパシタ(スイッチ11〜13及び帰還容量Cf)とサンプリング容量Csと増幅回路100とを含むスイッチトキャパシタ型増幅回路110aと、(2)スイッチトキャパシタ型増幅回路110aに基準電圧Vrefを供給する基準電圧回路110bとを備え、基準電圧回路110bは、基準電圧Vrefを出力するバッファ回路1と、バッファ回路1の出力端子111とスイッチトキャパシタ型増幅回路110aに基準電圧Vrefを供給するための基準電圧入力端子112との間に接続された第2のスイッチトキャパシタ(スイッチ10及び容量Cc)とを有する。

(もっと読む)

変換装置、及び計測装置

【課題】温度調整手段が別途不要で内部の温度調整対象を適温に制御可能な構成とすることで、使用環境温度が変化しても安定して高精度な計測結果が得られる計測装置を提供する。

【解決手段】デジタル処理回路での処理にかかるA/Dコンバータの待機時間での通常モードと待機モードとの時間割合(時間ta,tbの割合)をアナログ回路の周囲温度の検出温度に基づいて変更し、各モードの異なる電力消費に基づく発熱量の違いにてその周囲温度の温度制御を行うようにした。つまり、A/Dコンバータの動作不要な時間にA/Dコンバータ自身を温度調整手段として機能させることでその温度制御が行われる。

(もっと読む)

アナログ入力モジュール保護装置

【課題】アナログ入力モジュールを過電圧から保護すること。

【達成手段】本発明の保護装置は、複数のプラス/マイナスアナログ信号の電圧レベルがアナログ入力モジュールのプラス/マイナス動作電圧よりも大きい場合、前記複数のプラス/マイナスアナログ信号の電圧を前記アナログ入力モジュールに供給する安定化部を含む。

(もっと読む)

アナログ−デジタル変換器

【課題】必要な分解能を達成しながらより低い電力を達成する引き続く要望がある。従って、電力をさらに低減するのは望ましい。従って、必要な分解能を達成しながらより低電力を達成すること。

【解決手段】アナログ入力信号をデジタル出力信号に変換するようにとなっている変換器200が、アナログ入力信号を受信するためにアナログ入力端子205、該アナログ入力端子に接続した冗長符号桁(RSD)段210、デジタル部分220を含む。RSD段は、該アナログ入力端子で該アナログ入力信号を受信するように構成され、第1クロックサイクルの第1半分中該アナログ入力信号からデジタル出力でビットの第1の数を生成するように構成され、第1クロックサイクルの第2半分中該アナログ入力端子でアナログ入力信号の残留フィードバック信号を供給するように構成され、第2クロックサイクルの第1半分中該残留フィードバック信号からデジタル出力でビットの第1の数よりも少ないビットの第2の数を生成するように構成される。

(もっと読む)

抵抗の誤差訂正を用いるコンパレータベースのバッファ

【課題】スイッチトキャパシタの負荷を有する高利得増幅器の駆動容量を高めるコンパレータベースのバッファ方法及びシステムを提供することを目的とする。

【解決手段】電流源と、コンパレータと、スイッチと、サンプリングキャパシタと、オーバーシュート訂正抵抗を含む。充電経路内の抵抗及び訂正位相を使用する訂正の解決法は、電力消費を制約し、コンポーネントを最小化する一方で、出力電圧のオーバーシュートを低減する。Spectre(登録商標)シミュレーションは、本発明の効果を確証する。

(もっと読む)

AD変換装置、AD変換方法、及び電子機器

【課題】AD変換の精度を向上させる。

【解決手段】AD変換装置1は、大きさが互いに異なるn(nは2以上の自然数)個の偏移信号δkを生成する偏移信号生成部20と、偏移信号生成部20を制御する偏移信号制御部10と、入力アナログ信号Cinとn個の偏移信号δkとを順次加算してn個の第1信号S1を生成する偏移信号加算部30と、n個の第1信号S1をAD変換してn個の第2信号S2を生成するAD変換部40と、n個の第2信号S1に平均処理を施して出力デジタル信号Coutを生成する信号処理部50とを備える。

(もっと読む)

81 - 100 / 659

[ Back to top ]