Fターム[5J022AA02]の内容

アナログ←→デジタル変換 (13,545) | A/D変換器の型式 (1,573) | 逐次比較型A/D (217)

Fターム[5J022AA02]の下位に属するFターム

追従型(U、Dカウンタ) (8)

再循環(再巡回)型 (12)

直列接続型(CCD、BBD) (18)

Fターム[5J022AA02]に分類される特許

1 - 20 / 179

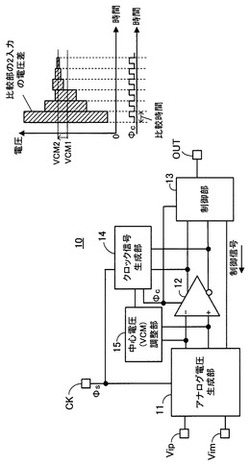

AD変換回路及びAD変換方法

【課題】ビット判定時に比較部での比較時間が長くなることによりAD変換時間が長くなることを抑制する。

【解決手段】アナログ電圧生成部11が、受信したアナログ信号を外部クロック信号Φsに同期してサンプリングし、制御信号に基づいて第1のアナログ電圧及び第2のアナログ電圧を生成し、比較部12がクロック信号Φcに同期して第1のアナログ電圧と第2のアナログ電圧の大きさを比較し、制御部13が第1のアナログ電圧と第2のアナログ電圧の電圧差を縮小させていき、比較部12の比較結果に基づいて、外部クロック信号Φsに同期してサンプリングされたアナログ信号に応じたデジタル信号を生成し、中心電圧調整部15が、クロック信号Φcの信号遷移の回数が閾値以上になると、比較部12の入力トランジスタに流れる電流が増加するように、第1のアナログ電圧と第2のアナログ電圧の中心電圧を調整する。

(もっと読む)

逐次近似アナログ・デジタル変換

【課題】アナログ入力信号をデジタル出力信号に変換するためのシステム及び方法を提供する。

【解決手段】システムは、DAC電流を供給するための電流モード(CM)デジタル・アナログ変換器(DAC)回路210を含む。比較器回路250は、DAC電流及びアナログ入力信号に基づいて決定されたエラー信号に応答して比較器信号を発生する。逐次近似レジスタ回路270は、比較器信号に応答して、DACコード信号274又はデジタル出力信号272のうちの少なくとも1つを発生する。DACコード信号をCM DAC回路によって用いて、DAC電流を制御する。

(もっと読む)

マルチビット遂次比較型ADC

【課題】いくつかの逐次比較サイクルでサイクル当たり1つよりも多いビットに変換するアナログ/デジタル変換器(ADC)を提供する。

【解決手段】システムは、容量性サブDAC回路410及び比較器430を含み、スイッチS2は、1つ又はそれよりも多くの最初のサイクル中に容量性サブDAC回路を隔離し、かつ1つ又はそれよりも多くの最終サイクル中にサブDAC回路を融合し、逐次比較型レジスタ(SAR)440は、デジタル出力信号又はDACデジタル信号を発生させる。また、システムは、DAC回路を含み、アナログ入力信号及びDACアナログ信号のうちの少なくとも一方で入力キャパシタCinを予充電し、プログラマブル利得増幅器420は、誤差信号を増幅し、マルチビットADCは、増幅された誤差信号をマルチビットデジタル信号に変換し、SARは、マルチビットデジタル信号を使用してDACデジタル信号又はデジタル出力信号を発生させる。

(もっと読む)

アナログ・デジタル変換装置

【課題】予測変換を行なう逐次変換方式のAD変換装置において、従来よりも予測精度を向上させる。

【解決手段】アナログ・デジタル変換装置1において、変化量算出部22は、変換部11によって入力信号のAD変換が実行される度に、新たに得られたAD変換結果と1つ前に得られたAD変換結果との変化量を算出する。変化量記憶部23は、前回までのAD変換結果に基づいて算出された所定数の変化量を記憶する。最大変化量抽出部24は、変化量記憶部23に記憶されている所定数の変化量のうちで最大変化量を抽出する。変換値予測部30は、抽出された最大変化量に基づいて、AD変換によって求める全ビットのうちの1または複数ビットの予測値を決定する。変換部11は、変換値予測部30によって予測値が決定された1または複数ビットを除く残余のビットの値を逐次比較方式によって決定する。

(もっと読む)

A/D変換器

【課題】 キャパシタの誤差の影響を少なくし、A/D変換器の精度を高める。

【解決手段】 アナログ信号更新部100は、キャパシタC1PおよびC1Nが差動増幅器150の入力側に入力キャパシタとして接続され、キャパシタC2PおよびC2Nが差動増幅器150の入出力間に帰還キャパシタとして接続された第1の状態またはキャパシタC2PおよびC2Nが差動増幅器150に入力キャパシタとして接続され、キャパシタC1PおよびC1Nが差動増幅器150に帰還キャパシタとして接続された第2の状態に切り換え可能である。制御部400は、A/D変換サイクル単位で、A/D変換のための係数乗算処理時のアナログ信号更新部100を交互に第1の状態とし、または第2の状態とする切り換えを行う。平均化部502は、所定回数に亙るA/D変換結果が得られる毎に、A/D変換結果を平均化して出力する。

(もっと読む)

アナログデジタル変換装置及びアナログデジタル変換方法

【課題】変換対象であるアナログ信号の信号特性に応じた分解能でデジタル信号に変換でき、かつ、その際の消費電力が削減できるようにする。

【解決手段】入力信号G1の所定の特性を検出する信号特性検出部6と、信号特性検出部により検出された信号特性に基づき分解能を設定し、該分解能のアナログデジタル変換に必要な動作のみを指示する制御信号G10を生成し、出力する制御信号生成部7と、複数のレジスタ値が格納されて、レジスタ値に対応したレジスタ信号を出力する逐次比較レジスタと、レジスタ信号をアナログ信号に変換して、基準電圧信号として出力するデジタルアナログ変換器と、入力信号と基準電圧信号とを比較して比較結果信号を出力するコンパレータと、を備える。

(もっと読む)

逐次比較型AD変換器及びその制御方法

【課題】SubDACの出力端子につながる4端子コンパレータのトランジスタのゲート容量が所望の容量比となるように制御して補正し、高精度化を可能とする逐次比較型AD変換器を提供する。

【解決手段】探索範囲を設定するデジタル値DSRを受け、対応する電圧を出力するMainDAC102,103と、探索範囲を設定するための制御信号を受け、対応する電圧を出力するSubDAC101と、MainDAC102,103とSubDAC101からの電圧の比較を行う4端子コンパレータ105,107、MainDAC+(102)と、MainDAC−(103)の出力電圧を比較するコンパレータ106と、切替制御信号に基づきSubDAC101の出力A1,B1,D1,E1又はコモン電圧VCMに切り替えるセレクタ104と、セレクタ104に切替制御信号を与える逐次比較レジスタロジック108を備える。

(もっと読む)

アナログデジタル回路及びそのアナログデジタル回路を用いた受信機

【課題】アナログ電圧を基準電圧と比較する比較器を有し、その比較器を構成するMOSトランジスタの耐圧をアナログ入力信号の信号振幅の最大電圧より低くすることが可能な逐次変換型アナログデジタル変換器を提供する。

【解決手段】共通ノードに第1端子により接続し、2の巾乗の重み付けがされた複数の第1キャパシタ50a〜50eからなるキャパシタアレイ40と、共通ノードの電圧減衰に寄与する第2キャパシタ70と、それぞれの第1キャパシタに、第1基準電圧、第2基準電圧、又は、入力信号の電圧の内の一つの供給又は切断を行う、複数の第1スイッチからなるスイッチアレイと、共通ノードに第3基準電圧を供給又は切断を行う第2スイッチ30と、共通ノードの電圧を、第3基準電圧と比較する比較器と、第1スイッチ、第2スイッチを制御する制御回路と、を備える。

(もっと読む)

AD変換器、情報処理装置

【課題】動作速度の低下や回路所要面積の増大を抑えつつノイズ増加を防ぐことのできるAD変換器、情報処理装置を提供する。

【解決手段】各々の一端が互いに接続され、それぞれ所定の比率で重み付けされた容量値を有し、容量値を低減可能な可変容量キャパシタを少なくとも1つ含む複数の重み付けキャパシタを有するAD変換器は、複数の重み付けキャパシタの互いに接続された一端が入力と接続された比較器と、複数の重み付けキャパシタの互いに接続された一端と異なる他端それぞれを、入力信号が入力される入力端子、入力信号の逐次比較に用いる参照電圧源、グランドおよび開放端子のいずれか1つと接続する複数のスイッチとを有する。また、このAD変換器は、重み付けキャパシタに入力信号をサンプリングするとともに、比較電圧を生成して処理を実行する逐次比較制御部と、可変容量キャパシタの容量値を低減させる容量制御部とを有する。

(もっと読む)

確率的A/D変換器及び確率的A/D変換器を用いる方法

【課題】高精度で低電力のアナログ−デジタル変換器回路を提供する。

【解決手段】アナログ−デジタル変換器回路は、アナログ入力信号1を受信し、変換ビットの第1のセット3と第1の完了信号7とアナログ入力信号及び変換ビットの第1のセットにより表された信号の間の差を表す残差アナログ出力信号4とを発生する第1の変換器ステージ2と、第1の完了信号を受信しクロック信号を発生するクロック発生回路8と、各々が残差アナログ出力信号及び共通参照電圧を受信するよう構成されクロック信号により動作されて複数の比較器決定を出力する複数の比較器と、複数の比較器決定を受信し変換ビットの第2のセットを発生するデジタル処理ステージとを備える第2の変換器ステージ9と、変換ビットの第1及び第2のセットを組み合わせることにより、アナログ入力信号のデジタル表現を発生する手段とを備える。

(もっと読む)

逐次比較型AD変換方法および装置

【課題】システム全体でのオフセット補償とダイナミックレンジの確保を可能とするAD変換装置を提供する。

【解決手段】ブリッジセンサB1から非測定検出信号が入力するとき、第1のサイクルにおいて、高利得差動増幅器2の基準電圧VCOMとして初期値をセットして、逐次比較型AD変換本体部3でAD変換データを求める。・・・。第m(mは3以上の正の整数)のサイクルにおいて、第m−1のサイクルで得られたAD変換データの最上位ビットに応じて、AD変換データが零値に近づくように、基準電圧VCOMとして、第m−1の電圧を所定電圧だけ上昇又は下降させた第mの電圧をセットする。センサB1から実測定検出信号が入力するとき、基準電圧VCOMとして第mの電圧をセットしてAD変換データを求める。

(もっと読む)

A/D変換回路及びそのテスト方法

【課題】コード変化による容量アレイの電位変化が規格範囲内であるか判定可能なA/D変換回路を提供すること。

【解決手段】本発明にかかるA/D変換回路は、外部からのアナログ信号又はデジタル信号に応じた電位をコンパレータ200の非反転入力端子に供給する容量アレイ201と、第1テストモードの場合に第1デジタル信号を前記容量アレイに供給した後、第2テストモードの場合に第2デジタル信号を容量アレイ201に供給するテスト制御回路306と、第1テストモードから第2テストモードにモードが変化した場合に、コンパレータ200の反転入力端子の電位を所定電圧分変化させる規格電圧発生回路305と、非反転入力端子及び反転入力端子に入力される各電位を比較して比較結果を出力する比較部と、を備え、テスト制御回路306は、第1及び第2テストモードにおけるそれぞれの比較結果に基づいて前記容量アレイの良否判定を行う。

(もっと読む)

AD変換回路

【課題】AD変換結果に異常があった場合に、再変換の実行開始までの時間を短縮することのできるAD変換回路を提供する。

【解決手段】実施形態のAD変換回路1は、最上位ビットから順次値が確定する逐次比較レジスタ111を有する逐次比較AD変換部11と、逐次比較AD変換部11の前回の変換結果が書き込まれた変換結果レジスタ12とを備える。このAD変換回路1は、比較部13が、AD変換の途中で、逐次比較レジスタ111の値の確定した範囲のビット値を変換結果レジスタ12の同一範囲のビットの値と比較し、変換開始制御部14が、比較部から比較結果が不一致であることを示す不一致信号UMが出力されたときに、逐次比較AD変換部11へ新たな変換の開始を指示する変換開始信号STを出力する。

(もっと読む)

ADコンバータ、及び、電子装置

【課題】変換精度の高いADコンバータ、及び、電子装置を提供する。

【解決手段】ADコンバータは、第1ビット数分の第1キャパシタで保持するデジタル信号をアナログ変換して得る残差信号を出力する第1DA変換部10と、第2ビット数分の第2キャパシタで保持するデジタル信号をアナログ変換して得る残差信号を出力する第2DA変換部150と、第1DA変換部が出力する残差信号を増幅して第2DA変換部に転送する増幅部140と、第1DA変換部が出力する残差信号と所定の基準レベルとの第1比較結果と、第2DA変換部が出力する残差信号と所定の基準レベルとの第2比較結果とを表す二値信号を出力する比較部120と、第1比較結果を表す二値信号を第1DA変換部に入力するとともに、第2比較結果を表す二値信号を第2DA変換部に入力する逐次制御部130とを含み、第2DA変換部の第2キャパシタは、増幅部のキャパシタと共用である。

(もっと読む)

A/D変換器

【課題】占有面積の大幅な増大を来すことなく、分解能を向上させることができるA/D変換器の提供を図る。

【解決手段】アナログの入力信号を受け取り、該入力信号の入力電圧Vin+,Vin-に応じた電荷を蓄積する複数のキャパシタCP0〜CP10,CN0〜CN10と、前記各キャパシタに対して、前記入力電圧および基準電圧を切り替えて印加する複数のスイッチSWP1〜SWP10,SWN1〜SWN10と、前記複数のスイッチを制御し、前記複数のキャパシタにより電荷再分配を行って逐次比較する比較回路2と、前記比較回路の出力を受け取り、前記複数のスイッチを制御してアナログの前記入力信号に対応したデジタルの出力信号を出力する制御回路3と、前記比較回路による比較時間を利用し、該比較回路の比較判定を超えた分解能で前記入力信号に対応したデジタルの出力信号を規定する分解能向上部4と、を有する。

(もっと読む)

超音波診断装置および超音波画像生成方法

【課題】画像生成処理の高速化と省電力化を図ることができる超音波診断装置を提供する。

【解決手段】アレイトランスデューサから出力される受信信号の振幅に応じて、受信信号処理部による受信信号のA/D変換可能範囲のうち実際にA/D変換が実行されるA/D変換実行範囲を限定し、受信信号のA/D変換を行う。A/D変換実行範囲は、測定深度に関わらずに所定のビット幅を有し、A/D開始ビットおよびA/D終了ビットで特定され、測定深度が増すほど、A/D変換実行範囲のA/D開始ビットおよびA/D終了ビットが漸減される。

(もっと読む)

AD変換器およびAD変換方法

【課題】先行する先行入力信号に対する現在の入力信号の差分信号の大きさや符号に関わらずAD変換を可能とするAD変換器およびAD変化何方法を提供すること。

【解決手段】サンプリング容量で先行入力信号に対する入力信号の差分信号をサンプリングする。オフセット回路でサンプリングされた差分信号にオフセットを付与する。検出回路でオフセットの付与された差分信号が規定の信号範囲にあるか否かを検出する。検出回路により規定の信号範囲にあると判断される場合には規定ビット分解能から規定の信号範囲に対応するビット数を縮小した縮小ビット分解能で差分信号のAD変換を行なう。規定の信号範囲にないと判断される場合には、規定ビット分解能で入力信号のAD変換を行なう。

(もっと読む)

A/Dコンバータ、マイコン、故障判定方法

【課題】AD変換中にアナログ入力の値が変動したことをより高精度に判別可能なA/Dコンバータを提供すること。

【解決手段】アナログ入力の下限値と上限値が登録された判定テーブル28と、アナログ入力と、アナログ値に変換された基準値を比較する比較手段24と、前記比較手段がアナログ入力の方が基準値より大きいと判定するとより大きい基準値に変更し、アナログ入力の方が基準値より小さいと判定するとより小さい基準値に変更する基準値変更手段26と、比較結果及び基準値を取得し、アナログ入力の方が基準値より小さい場合は前記判定テーブルの前記上限値に基準値を設定し、アナログ入力の方が基準値より大きい場合は前記判定テーブルの前記下限値に基準値を設定するテーブル更新手段27と、アナログ入力が前記下限値と前記上限値の範囲に入るか否かを判定する異常判定手段29と、有する。

(もっと読む)

比較回路及びアナログデジタル変換回路

【課題】動作電圧に対して入力電圧範囲を拡大し、低消費電力化を図ること。

【解決手段】比較回路10の電圧制御部12は、キャパシタC11の第1端子に、クロック信号CKに応答して高電位電圧AVDと低電位電圧(グランドGND)を供給する。キャパシタC11の第2端子に接続されたトランジスタT23は、反転クロック信号XCKに応答してオンオフする。入力トランジスタT11,T12のしきい値電圧と等しく設定されたトランジスタT23は、グランドGNDの電圧とノードN21の電圧に応じて反転状態となり、比較部11に供給する制御電圧VCM(ノードN21の電圧)をグランドGNDからトランジスタT23のしきい値電圧低い電圧に安定させる。

(もっと読む)

逐次比較型ADコンバータおよびその検査方法

【課題】ADコンバータの変換時間および検査時間を削減する。

【解決手段】

本発明にかかる逐次比較型ADコンバータ10は、アナログ入力をサンプルホールドするサンプルホールド回路13と、サンプルホールド回路13から出力された電位と基準電位とを逐次比較する比較器14と、比較器14による比較結果を記憶する逐次比較レジスタ15と、逐次比較レジスタから出力された比較結果のうち上位ビットの値を記憶するSAR上位ビットレジスタ17と、逐次比較レジスタ15から出力された比較結果の下位ビットの値に基づいて、比較器14における次回以降の逐次比較を全ビットについて行うか、または下位ビットについてのみ行うかを設定するスキップフラグ設定回路18と、を備える。

(もっと読む)

1 - 20 / 179

[ Back to top ]