Fターム[5J022AC02]の内容

アナログ←→デジタル変換 (13,545) | A/D、D/Aの共通装置 (390) | A/D→D/A伝送・データ処理 (42)

Fターム[5J022AC02]に分類される特許

1 - 20 / 42

音声信号伝送システム

【課題】簡便な構成で音声信号を伝送可能な音声信号伝送システムを提供する。

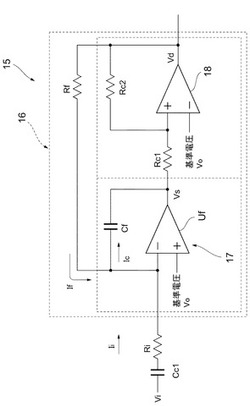

【解決手段】アナログ音声信号をデジタル音声信号に変換して出力するアナログ・デジタ

ル変換器15と、アナログ・デジタル変換器15から出力されたデジタル音声信号をアナ

ログ音声信号に変換して出力するデジタル・アナログ変換器とを備え、アナログ・デジタ

ル変換器15は、比較器18と積分器17とを有し、比較器18および積分器17により

発振回路16を構成することで、アナログ音声信号を当該アナログ音声信号に応じてパル

ス幅が変化するデジタル音声信号に変換し、デジタル・アナログ変換器は、デジタル音声

信号をアナログ音声信号に変換するローパスフィルタ回路を有している。

(もっと読む)

周波数変調装置

【課題】音声信号がアナログ形式で入力される場合であっても、送信周波数をずらすことなく周波数変調を行うことが可能な周波数変調装置を提供する。

【解決手段】周波数変調装置は、アナログ−デジタル変換部(ADC)、DC除去部、中心周波数加算部、振幅−周波数変換部、デジタル−アナログ変換部(DAC)及び送信周波数変換部を具備する。DC除去部は、ADCでデジタル化された信号に含まれる直流成分を除去した減算信号を出力する。中心周波数加算部は、減算信号に、所定の周波数に対応する値を加算した加算信号を出力する。振幅−周波数変換部は、加算信号が示す振幅値情報を周波数値情報に変換する。デジタル−アナログ変換部は、振幅−周波数変換部からの信号をアナログ変換し、送信周波数変換部は、アナログ変換後の信号の周波数を周波数変換し、周波数変調信号として出力する。

(もっと読む)

リモコンおよびリモコンシステム

【課題】アナログ音声信号をA/D変換して利用するリモコンにおいて、A/D変換時における中点電位の偏位量を製品ごとに検出し、D/A変換時に有効なノイズリダクション処理を実行できるようにする。

【解決手段】マイクロフォン13から入力されるアナログ音声信号をデジタルデータに変換するA/D変換部14と、デジタルデータをアナログ音声信号に変換するD/A変換部16とを有するリモコン2において、入力されるアナログ音声信号を無信号入力状態とし、このときのA/D変換部14におけるA/D変換値の平均値を中点電位とするとともに、上記A/D変換値の最大値と最小値とから上記中点電位に対する偏位量を求め、これら中点電位および中点電位に対する偏位量を、上記デジタルデータをD/A変換するD/A変換部16におけるノイズリダクション処理用のデータとして用いる。

(もっと読む)

電源回路

【課題】1V以下という低電圧動作においても安定に所望の出力電圧を得ることができる電源回路を提供する。

【解決手段】電源回路において、複数のスイッチ103を並列に接続したスイッチアレイ部104と、スイッチアレイ部104の各スイッチ103のオンまたはオフの状態を記憶するスイッチ状態レジスタ106と、参照電圧とスイッチアレイ部104の出力に接続される出力端子の電圧とを比較し、この比較結果をデジタル値として出力する比較回路105とを有する。そして、比較回路105からのデジタル値の出力により、スイッチ状態レジスタ106の値を更新することで、スイッチアレイ部104の各スイッチ103の状態を変更する。

(もっと読む)

線形性改善回路、ΣΔA/D変換器、および受信装置

【課題】バイナリコードで演算する加算器が不要で、高速、低消費電力で動作することが可能な線形性改善回路、ΣΔA/D変換器、および受信装置を提供する。

【解決手段】線形性改善回路10は、nビットのA/D変換器の前回の出力コードに応じた第1シフト量を生成する第1シフト量生成部12と、入力コードデータを、供給される第1シフト量をもってビットシフトして出力する第1シフタ回路13と、第1シフタ回路の出力を格納し、格納データを第1シフタ回路の入力コードデータとして出力して第1シフタ回路とループ回路を形成し、かつ、格納コードデータを第2シフト量として出力するレジスタと、A/D変換器の出力コードを供給される第2シフト量をもってビットシフトしてnビットのD/A変換器に出力する第2シフタ回路16と、を有する。

(もっと読む)

信号変換装置,信号変換方法及び信号変換プログラム

【課題】共通構成で異なる電子制御装置の評価を行えるようにする。

【解決手段】電子制御装置20とその評価を行う評価装置40との間に介装される信号変換装置60において、評価装置40からスイッチ信号値(デジタル信号値)若しくはセンサ信号値(アナログ信号値)を受信したとき、又は、電子制御装置20からデジタル制御信号値若しくはアナログ制御信号値を受信したとき、デジタル信号の設定位置が設定されたデジタル信号割当テーブルA又はアナログ信号に対してその分解能が関連付けられたアナログ信号割当テーブルBを参照し、その信号割当ルールに従って受信信号を適宜変換する。そして、外部信号I/F70又はデジタル信号I/F62を介して、変換した信号を電子制御装置20又は評価装置40へと送信する。

(もっと読む)

楽音信号送信装置及び楽音信号受信装置

【課題】 部品点数が少なく、簡単な回路で構成でき、複数の楽音信号を1本の信号経路で送信又は受信できる楽音信号送信装置及び楽音信号受信装置を提供する。

【解決手段】 1ビットA/D変換部1L及び1Rにより、電子楽器などから入力された複数のアナログ楽音信号は各々1ビットデジタル信号に変換され、重み付け部2L及び2Rによりこれらの各1ビットデジタル信号は重み付け加算されて、出力部3により出力されることになると共に、受信部4により受信された重み付け加算信号は、分離部5により各1ビットデジタル信号に分離変換され、さらにD/A変換部6により、アナログ信号に復調されることになる。

(もっと読む)

A/D変換での信号伝送補正システム及びその方法

【課題】送信手段で認識された伝送元の信号を、受信手段にて正しく認識できるように信号のレベル補正を行い、さらには、アナログ伝送された信号に購入される外来ノイズが、A/D変換時の分解能幅の中に収まるように信号のオフセットを実施してノイズの無効化を図る。

【解決手段】受信側ブロック4の信号入力側の直近に、補正ブロック8が配置された点にある。補正ブロック8には、送信側ブロック2で認識された伝送元の信号が受信側ブロック4でも正しく認識されるように信号レベルを補正するレベル補正部9と、ノイズを無効化するためのオフセット部10が設けられている。

(もっと読む)

インターフェース回路およびデータ処理装置

【課題】LSI間、ボード間、装置(ユニット)間などのインターフェースにおいて、信号線1本当りのデータ転送効率を向上させる。

【解決手段】シフト回路710−0は、1本のデジタル信号D1(0)をシフトさせて、3本のデジタル信号D1S(00)乃至(02)として出力する。アナログ変換回路720−0は、3本のデジタル信号D1S(00)乃至(02)を1本のアナログ信号A2(0)に変換して転送する。デジタル変換回路730−0は、1本のアナログ信号A2(0)を3本のデジタル信号D3(00)乃至(02)に変換する。選択回路740−0は、3本のデジタル信号D3(00)乃至(02)から順次選択して1本のデジタル信号D4(0)を出力する。

(もっと読む)

コンバータ

【課題】高精度のA/D変換又はD/A変換を行うコンバータに関し、処理時間を短縮すると共に不要信号の混入を防止する。

【解決手段】アンチエイリアシング用のフィルタ2と、オーバーサンプリングしてデジタル信号に変換するA/Dコンバータ3と、伝送速度の偶数倍の速度に相当するサンプリング周波数として処理する第1のデジタルフィルタ4と、伝送速度の1/2に相当する周波数以上の周波数成分を完全に減衰させる第2のデジタルフィルタ7と、間引き処理により、所定の伝送速度のデジタル信号とするデジメーション部8とを含む構成、及び受信デジタル信号にゼロ挿入を行うインタポレーション部17と、伝送速度の1/2の速度に相当する周波数以上の周波数成分を完全に減衰させる第2のデジタルフィルタ16と、第1のデジタルフィルタ14と、D/Aコンバータ13と、ポストフィルタ12とを含む構成を備えている。

(もっと読む)

集積回路装置及び電子機器

【課題】回路規模の増加を抑えながら高い精度のオフセット調整等を実現できる集積回路装置及び電子機器の提供。

【解決手段】集積回路装置は、カスケード接続された第1〜第Nの増幅器AM1〜AM3を有し、入力信号が入力される増幅回路10と、増幅回路10により増幅された信号に対するA/D変換を行うA/D変換器50と、第1〜第Nの増幅器AM1〜AM3に対応して設けられ、第1〜第Nの増幅器AM1〜AM3のオフセット調整を行うための第1〜第NのD/A変換器DAC1〜DAC3と、第1〜第NのD/A変換器DAC1〜DAC3を用いた第1〜第Nの増幅器AM1〜AM3のオフセット調整の設定とゲイン調整の設定を行う制御回路70を含む。

(もっと読む)

適応可能な高次のデジタル・アナログ変換

信号再構成のための単純なアナログ回路を使用しフィードバック制御技術を採用して1次以上のホールドでデジタル/アナログ変換を実行するための技術が開示される。

1つの設計において、デジタル/アナログ変換回路は、逆モデル回路、フィードバック回路、ゼロ次のホールド(ZOH)回路、およびアナログ回路を含む。

逆モデル回路は、デジタル入力信号を処理し、第1のデジタル信号を供給する。

フィードバック回路は、第1のデジタル信号とアナログ回路からのアナログ出力信号を受信し、低周波ノイズ・フィルタリング実行し、第2のデジタル信号を供給する。

ZOH回路は、ゼロ次のホールドでデジタルからアナログに第2のデジタル信号を変換し、アナログ回路のためのアナログ入力信号を供給する。

アナログ回路は、アナログ入力信号上で作動し、アナログ出力信号を供給する。

アナログ回路は、1つ以上のポールを含み得る。  (もっと読む)

(もっと読む)

超音波アナログ信号の分周方法

【課題】超音波アナログ信号を分周して、可聴周波数に変換するとき、周波数スペクトルが低域に移行しても変わらないようにする。

【解決手段】超音波アナログ信号を分周する時、アナログのゼロを横切る点から、次にゼロを横切る点までの高速クロックでアナログ−デジタル変換を行い、180°又は180°の倍数の単位で、メモリーした波形を任意の低速のクロック再生しながら繋ぐ時、極性を合わせながら速やかに繋いでいく様にした超音波アナログ分周方法である。

(もっと読む)

ディジタル制御装置の自動調整方式

【課題】D/A変換のオフセットとゲインの自動調整のためのハードウェアおよびソフトウェアをディジタル制御装置に設けることなく自動調整できる。

【解決手段】ディジタル形保護継電装置の保護継電部10a〜10dの自動試験を行う自動試験装置(コンピュータ11やインターフェース12)は、保護継電部内のD/A変換器の入力として2点のディジタルデータを設定し、このデータ設定に対する保護継電部からのA/Oとの差からオフセットとゲインの補正値を求め、この補正値で保護継電部内のD/A変換器のオフセットとゲインを補正する。オフセットとゲイン補正は、D/A変換器の入力をスケール変換する変換器の変換特性の補正、またはD/A変換器自体のオフセットとゲイン調整をする。

(もっと読む)

半導体集積回路

【課題】A/Dコンバータ及びD/Aコンバータをいずれも含んだアナログモジュールを備えた半導体集積回路において、アナログモジュールの検査コストを低減する。

【解決手段】テスト起動端子TSから起動指令が入力されると、テスト制御回路20は、スイッチ16〜19を切り替えることで、テストパターン生成回路15,アナログモジュール(A/Dコンバータ10,D/Aコンバータ11),判定回路14を接続するループバック経路を設定すると共に、テストパターン生成回路15,判定回路14を起動することでテスト動作を実行し、そのテスト動作によって判定回路14から出力される測定結果(アナログモジュールの動作特性の良否)を、テスト結果端子TRを介して出力する。つまり、テスト起動端子TSに起動指令を入力してテスト結果端子TRを監視するだけでアナログモジュールの検査を実施することができる。

(もっと読む)

低電力DC−DCSMPSのためのプログラマブルアナログデジタル変換器

電圧時間変換に基づく窓付きアナログデジタル変換器(ADC)は、プログラマブル基準電圧、変換時間、及び電圧調節精度を有することができる。ADCは、小さいシリコン面積上に完全に実施することができ、かつ高周波低電力スイッチモード電源(SMPS)のための様々な集積デジタルコントローラに実施にするのに適している。そのプログラマブル特性は、遅延線又は他の電圧時間変換構造の固有の平均化効果の利用を通じて、かつ代替構造における遅延セルの伝播時間又は有効電圧時間変換比の調節を通じて達成することができる。 (もっと読む)

信号変換伝達装置

【課題】簡素な構成で複数のA/Dコンバータまたは複数のD/Aコンバータと接続して信号の入出力を行う信号変換伝達装置を得る。

【解決手段】オーディオ信号Lch101,Rch102をシリアルデータに変換するADC1から出力されるPCMデータとオーディオ信号Lch103,Rch104をシリアルデータに変換するADC2から出力されたPCMデータとをORゲート6が加算し、

DSP3が、BCK信号及びLRCK信号を用いて、ADC1,2ならびにDAC4,5の動作を制御し、ADC1とADC2から異なるタイミングで出力されたPCMデータを一連のシリアルデータとしてORゲート6から入力し、またDAC4,5の動作を制御して一連のPMCデータからアナログ信号のオーディオ信号Lch101〜Rch104を各々出力させる。

(もっと読む)

信号処理システム

本発明は、多数の狭帯域アナログ入力又は出力信号の処理に必要とされるデジタル信号プロセッサの実装に関する。アナログ処理では、(重複しない周波数帯域を有した)複数のアナログ信号を1つの合成信号に合成し、1つのADCに送る。これらの信号は異なるソースから届いたものであり、従来の実装では個別のコンバータを使用していた。アナログ信号処理がデジタル信号プロセッサの外部で使用され、かつデジタル処理が内部で使用されることによって、元のアナログ信号は、個別のコンバータが使用される場合と同一の形式でデジタル領域に再構成される。同様の技術がD/A変換インタフェースに適用できる。デジタル合成動作では、複数のデジタル副帯域信号を1つの合成信号に合成する。この動作は、信号をアナログ領域への変換のために1つのDACに入力し、続いて、複数のアナログ信号への分離のためにアナログ分配デバイスに入力するより前に行われる。  (もっと読む)

(もっと読む)

高オーバサンプリング型のデジタル処理に基づいた低遅延の信号処理

低遅延の信号処理システムおよび方法が提供され、該システムは、デルタシグマA−D変換器と、オーバサンプリングプロセッサと、デルタシグマD−A変換器とを含む。デルタシグマA−D変換器は、入力またはオーディオ信号を受信し、高オーバサンプリングレートでデジタルのサンプル信号を生成する。オーバサンプリングプロセッサは、低遅延を有する高オーバサンプリングレートでデジタルサンプル信号を処理するために、A−D変換器に接続される。アナログ信号を生成するデルタシグマD−A変換器は、低遅延を有する高オーバサンプリングレートでデジタルサンプル信号を受信するために、オーバサンプリングプロセッサに接続される。オーバサンプリングプロセッサは、低遅延フィルタとプログラマブル遅延要素とを含む。この方法において、アナログ信号は、低遅延かつ高精度に作り出される。  (もっと読む)

(もっと読む)

AD変換制御装置、光受信装置、光受信方法および波形歪み補償装置

【課題】AD変換のサンプリングレートが受信信号のシンボルレートに近い値である場合であっても正確なタイミングでのAD変換を可能とする。

【解決手段】本発明の光受信装置は、各符号の光強度波形がRZパルスである変調方式を併用した光送信装置からの光信号をAD(Analog to Digital)変換部の変換処理によってデジタル信号へと変換する。AD変換部の後段の制御値算出部で、デジタル信号をデジタル処理してデジタル信号の絶対値または該デジタル信号の絶対値と一対一に対応する値を取得し、デジタル信号の絶対値または該デジタル信号の絶対値と一対一に対応する値に基づいてAD変換部でのサンプリングタイミングの最適タイミングからの誤差を推定し、該誤差に基づいて該サンプリングタイミングを制御する制御値を算出する。この制御値に基づいてAD変換のサンプリングタイミングを規定するパルスの位相を補正することが可能となる。

(もっと読む)

1 - 20 / 42

[ Back to top ]