Fターム[5J022BA06]の内容

アナログ←→デジタル変換 (13,545) | 目的、効果 (2,366) | 小型・集積・低消費電力化 (530)

Fターム[5J022BA06]に分類される特許

1 - 20 / 530

固体撮像装置

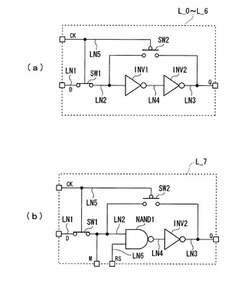

【課題】消費電流を低減することができる固体撮像装置を提供する。

【解決手段】画素信号のレベルに応じた論理状態の信号を出力する複数の遅延ユニットのいずれかの出力信号の論理状態をラッチするラッチ回路L_7において、複数の遅延ユニットのいずれかの出力信号が入力端子Dに入力される。NAND回路NAND1およびINV回路INV2は、画素信号のレベルに応じた制御信号が出力される制御信号出力タイミングまでは停止しており、制御信号出力タイミングの後に動作する。スイッチ回路SW1,SW2は、制御信号出力タイミングまでは複数の遅延ユニットのいずれかの出力信号を、信号線LN2を介して出力端子Mから出力し、制御信号出力タイミングから所定時間が経過した後のラッチタイミングで複数の遅延ユニットのいずれかの出力信号の論理状態をNAND回路NAND1およびINV回路INV2がラッチするように接続の切替を行う。

(もっと読む)

固体撮像装置

【課題】低周波ノイズ除去に伴う消費電力の増加を最小限に抑えることができる固体撮像装置を提供する。

【解決手段】画素部100は、入射した光の大きさに応じた画素信号を出力する画素101と、補正用基準電圧に応じた補正用画素信号を出力する補正用画素102とを有する。AD変換回路105は、複数の遅延素子が接続された遅延回路を有し、画素信号または補正用画素信号のレベルに対応する数の遅延素子をパルス信号が通過すると、パルス信号が通過した遅延素子の数に応じたデジタル信号を出力する。制御部111は、1フレーム内でm(mは2以上の自然数)行の画素信号のAD変換に対応して1行の補正用画素信号のAD変換を行うように垂直走査部103およびAD変換部105を制御する。ノイズ除去部109は、補正用画素信号のAD変換結果を用いて画素信号のAD変換結果からノイズを除去する。

(もっと読む)

アナログ・デジタル変換装置

【課題】予測変換を行なう逐次変換方式のAD変換装置において、従来よりも予測精度を向上させる。

【解決手段】アナログ・デジタル変換装置1において、変化量算出部22は、変換部11によって入力信号のAD変換が実行される度に、新たに得られたAD変換結果と1つ前に得られたAD変換結果との変化量を算出する。変化量記憶部23は、前回までのAD変換結果に基づいて算出された所定数の変化量を記憶する。最大変化量抽出部24は、変化量記憶部23に記憶されている所定数の変化量のうちで最大変化量を抽出する。変換値予測部30は、抽出された最大変化量に基づいて、AD変換によって求める全ビットのうちの1または複数ビットの予測値を決定する。変換部11は、変換値予測部30によって予測値が決定された1または複数ビットを除く残余のビットの値を逐次比較方式によって決定する。

(もっと読む)

アナログデジタル変換装置及びアナログデジタル変換方法

【課題】変換対象であるアナログ信号の信号特性に応じた分解能でデジタル信号に変換でき、かつ、その際の消費電力が削減できるようにする。

【解決手段】入力信号G1の所定の特性を検出する信号特性検出部6と、信号特性検出部により検出された信号特性に基づき分解能を設定し、該分解能のアナログデジタル変換に必要な動作のみを指示する制御信号G10を生成し、出力する制御信号生成部7と、複数のレジスタ値が格納されて、レジスタ値に対応したレジスタ信号を出力する逐次比較レジスタと、レジスタ信号をアナログ信号に変換して、基準電圧信号として出力するデジタルアナログ変換器と、入力信号と基準電圧信号とを比較して比較結果信号を出力するコンパレータと、を備える。

(もっと読む)

液晶表示装置の駆動装置

【課題】オフセットの影響、回路規模の増大、フリッカ等を抑制し、画質の向上に好適なドライバの提供。

【解決手段】切換制御信号が第1の論理値のとき、第1、第3の電圧が第1、第3の差動段に、第2、第4の電圧が第2、第4の差動段に入力され、第1、第3の差動段の出力が第1、第3の出力段の入力に、第2、第4の差動段の出力が第2、第4の出力段の入力にそれぞれ接続され、ガンマ抵抗1両端には第1、第2の電圧が、ガンマ抵抗2両端には第3、第4の電圧が印加され、切換制御信号が第2の論理値のとき、第1、第3の電圧が第3、第1の差動段に、第2、第4の電圧が第4、第2の差動段に入力され、第3、第1の差動段の出力が第1、第3の出力段の入力に、第4、第2の差動段の出力が第2、第4の出力段の入力にそれぞれ接続され、ガンマ抵抗1両端には第1、第2の電圧が、ガンマ抵抗2両端には第3、第4の電圧が印加される。

(もっと読む)

サンプリング回路

【課題】サンプリング回路の低消費電力化を図る。

【解決手段】サンプリングスイッチSW1を介してサンプリングキャパシタC1が接続される出力端子2に、トランジスタM1のソースとトランジスタM2のソースを接続する。さらに、トランジスタM1のゲートと入力端子1との電位差がトランジスタM3の閾値電圧にほぼ等しくなるように制御するダイオード接続のトランジスタM3と、入力端子1と出力端子2の電位が等しくなるよう制御し、トランジスタM1のドレイン電流とトランジスタM2のドレイン電流が等しくなるように制御する演算増幅器4とを設ける。

(もっと読む)

パイプライン型A/D変換回路

【課題】セットリング誤差を線形化でき、高速で消費電力の小さいパイプライン型A/D変換回路を提供する。

【解決手段】パイプライン型A/D変換回路において、各段のA/D変換回路部に、複数の比較器を含み、入力信号をA/D変換するサブA/D変換回路と、サブA/D変換回路からのデジタル信号を、正負の参照電圧を基準値として用いて生成したアナログ制御信号にD/A変換し、アナログ制御信号に基づき、入力信号を、複数のサンプリングキャパシタを用いてサンプリングし、ホールドし、増幅してD/A変換する乗算型D/A変換回路と、後段側の乗算型D/A変換回路でサンプリングをする前に、後段側のサンプリングキャパシタを、サブA/D変換回路に含まれる複数の比較器の出力する比較結果信号に応じて、正負の参照電圧の中間電圧値に予め充電するプリチャージ回路と、を設け、セットリング誤差を線形化する。

(もっと読む)

逐次比較型AD変換器および無線受信機

【課題】容量DA変換器を駆動するドライバを低消費電力化しつつ、低誤差のAD変換を行う。

【解決手段】バイナリ重み型容量DA変換器は、アナログ入力信号と、参照電圧とに基づき、Nビットの各ビットに対応するサイクル毎に、残差信号を生成する。第1比較器は、前記サイクル内の第1の時点における前記残差信号を、所定電圧と比較して、論理値を表す第1比較結果を得る。レジスタは、前記第1比較結果を保持する。第2比較器は、前記サイクル内における前記第1の時点より後の第2の時点における前記残差信号を、前記所定電圧と比較して、論理値を表す第2比較結果を得る。誤り判定回路は、前記第1比較結果が前記第2比較結果と異なるとき、誤り検出信号を発生させる。誤り訂正回路は、前記誤り判定回路により前記誤り検出信号が発生させられたとき、前記レジスタから読み出し第1比較結果を反転して出力する。

(もっと読む)

歪み補正装置

【課題】小面積および低消費電力な、A/D変換器の歪み補正装置を提供する。

【解決手段】本発明の一態様としての歪み補正装置は、第一A/D変換器と、第二A/D変換器と、べき乗器と、適応相関制御手段と、歪み除去手段とを備える。前記第一A/D変換器は、第一入力信号をA/D変換して第一変換信号を得る。前記第二A/D変換器は、第二入力信号をA/D変換して第二変換信号を得る。前記第二入力信号は、前記第一入力信号の振幅を低減した信号、または前記第一入力信号は、前記第二入力信号の振幅を増大した信号である。前記べき乗器は、前記第二変換信号をn乗(nは2以上の整数)することにより、べき乗信号を得る。前記適応相関制御手段は、前記べき乗信号と、前記第二変換信号に基づき適応相関制御を行うことにより、前記べき乗信号に含まれるn乗成分である歪み信号を生成する。前記歪み除去手段は、前記第一変換信号から、前記適応相関制御手段で生成された歪み信号を除去する。

(もっと読む)

ニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器

【課題】回路規模の増大を抑制し、低消費電力化を実現するフラッシュ型AD変換器を提供すること。

【解決手段】本発明の一実施形態によると、第1のCMOS回路と、共通するローティングゲートを有し、3個のゲートが前記フローティングゲートに配置され、アナログ入力電圧を入力する端子と前記第1のCMOS回路とに並列に接続する2n−1−1個(nは3以上の整数)のニューロンCMOS回路と、を備える量子化出力部と、前記量子化出力部から出力される量子化出力電圧を演算するエンコード部と、前記量子化出力部又は前記エンコード部に接続するn個のデジタル変換出力端子と、を備えることを特徴とするニューロンCMOS回路を備えるフラッシュ型アナログ−デジタル変換器が提供される。

(もっと読む)

確率的A/D変換器及び確率的A/D変換器を用いる方法

【課題】高精度で低電力のアナログ−デジタル変換器回路を提供する。

【解決手段】アナログ−デジタル変換器回路は、アナログ入力信号1を受信し、変換ビットの第1のセット3と第1の完了信号7とアナログ入力信号及び変換ビットの第1のセットにより表された信号の間の差を表す残差アナログ出力信号4とを発生する第1の変換器ステージ2と、第1の完了信号を受信しクロック信号を発生するクロック発生回路8と、各々が残差アナログ出力信号及び共通参照電圧を受信するよう構成されクロック信号により動作されて複数の比較器決定を出力する複数の比較器と、複数の比較器決定を受信し変換ビットの第2のセットを発生するデジタル処理ステージとを備える第2の変換器ステージ9と、変換ビットの第1及び第2のセットを組み合わせることにより、アナログ入力信号のデジタル表現を発生する手段とを備える。

(もっと読む)

AD変換器、情報処理装置

【課題】動作速度の低下や回路所要面積の増大を抑えつつノイズ増加を防ぐことのできるAD変換器、情報処理装置を提供する。

【解決手段】各々の一端が互いに接続され、それぞれ所定の比率で重み付けされた容量値を有し、容量値を低減可能な可変容量キャパシタを少なくとも1つ含む複数の重み付けキャパシタを有するAD変換器は、複数の重み付けキャパシタの互いに接続された一端が入力と接続された比較器と、複数の重み付けキャパシタの互いに接続された一端と異なる他端それぞれを、入力信号が入力される入力端子、入力信号の逐次比較に用いる参照電圧源、グランドおよび開放端子のいずれか1つと接続する複数のスイッチとを有する。また、このAD変換器は、重み付けキャパシタに入力信号をサンプリングするとともに、比較電圧を生成して処理を実行する逐次比較制御部と、可変容量キャパシタの容量値を低減させる容量制御部とを有する。

(もっと読む)

アナログ−デジタル変換装置及びアナログ−デジタル変換方法

【課題】 複数の受信経路から供給されるアナログ信号を一装置でデジタル化することで、受信装置の大型化を回避でき、かつ、量子化雑音の増大を抑えることが可能なアナログ−デジタル変換装置を提供する。

【解決手段】 アナログ−デジタル(A/D)変換装置は、バンド選択部、第1及び第2の切替部、A/D変換部及びチャネル選択部を具備する。バンド選択部は、複数の入力チャネルからアナログ信号を受信し、各アナログ信号から所定の帯域幅で信号を抽出する。第1の切替部は複数の入力チャネルの受信経路との接続を切り替え、複数の抽出信号を多重する。A/D変換部は、第1の切替部から出力される多重信号を、所定サンプリング周波数でデジタル信号へ変換する。第2の切替部は、複数の送信経路との接続を順次切り替え、受信経路と対応する送信経路へデジタル信号を出力する。チャネル選択部は、供給されたデジタル信号を、所定のサンプルタイミングでリサンプルする。

(もっと読む)

AD変換回路および固体撮像装置

【課題】消費電流を低減することができるAD変換回路および固体撮像装置を提供する。

【解決手段】比較部109は、AD変換の対象となるアナログ信号と、時間の経過とともに増加または減少する参照信号とを比較し、参照信号がアナログ信号に対して所定の条件を満たしたタイミングで比較処理を終了する。第1のカウント部18は、所定の周波数のクロック信号をカウントクロックとしてカウントを行い、カウント値を出力する。ラッチ部108は、第1のカウント部18から出力されるカウント値をラッチする。ラッチ制御部105は、比較処理の終了に係る第1のタイミングでラッチ部108を有効にし、第1のタイミングを所定の時間だけ遅延させた第2のタイミングでラッチ部108にラッチを実行させる。

(もっと読む)

音声信号伝送システム

【課題】簡便な構成で音声信号を伝送可能な音声信号伝送システムを提供する。

【解決手段】アナログ音声信号をデジタル音声信号に変換して出力するアナログ・デジタ

ル変換器15と、アナログ・デジタル変換器15から出力されたデジタル音声信号をアナ

ログ音声信号に変換して出力するデジタル・アナログ変換器とを備え、アナログ・デジタ

ル変換器15は、比較器18と積分器17とを有し、比較器18および積分器17により

発振回路16を構成することで、アナログ音声信号を当該アナログ音声信号に応じてパル

ス幅が変化するデジタル音声信号に変換し、デジタル・アナログ変換器は、デジタル音声

信号をアナログ音声信号に変換するローパスフィルタ回路を有している。

(もっと読む)

ADコンバータ

【課題】高精度で小型のADコンバータを提供する。

【解決手段】このADコンバータは、アナログ電圧VinをNビットのデジタルコードDCに変換するものであり、メモリブロックMB1〜MB(2N−1)を備える。各メモリブロックMB(2n−1)は、(2n−1)個のMRAM用のメモリセル1を含む。メモリセル1の記憶データを「0」にリセットした後に、アナログ電圧Vinに比例するアナログ電流Iinを、各メモリブロックMB(2n−1)の(2n−1)本のビット線BLに分流させる。メモリブロックMB1〜MB(2N−1)のメモリセル1の記憶データを読み出してデジタルコードDCを生成する。したがって、ラダー抵抗は不要である。

(もっと読む)

A/D変換装置、A/D変換方法および固体撮像装置

【課題】出力分解能を犠牲にすることなく、消費電力を低減することができるA/D変換装置、A/D変換方法および固体撮像装置を提供する。

【解決手段】

アナログ入力信号に応じてパルス信号を遅延させるn(n:正の整数、n≧2)個の遅延素子が円環状に接続され、第1の時刻から第2の時刻までパルス信号を伝播させるパルス遅延回路と、第1の時刻から第2の時刻よりも短い第3の時刻までの周回数をカウントするカウンタ回路と、第3の時刻までの周回数を上位ビットラッチ値として出力する上位ビットラッチ回路と、第3の時刻の位置を第1の下位ビットラッチ値として出力し、第2の時刻の位置を第2の下位ビットラッチ値として出力する下位ビットラッチ回路と、第1の時刻から第2の時刻までの周回数の上位ビット推定値と第2の下位ビットラッチ値とに基づいて、アナログ入力信号の大きさに応じたデジタル出力値を生成するデジタル演算回路と、を備える。

(もっと読む)

超音波診断装置および超音波画像生成方法

【課題】画像生成処理の高速化と省電力化を図ることができる超音波診断装置を提供する。

【解決手段】アレイトランスデューサから出力される受信信号の振幅に応じて、受信信号処理部による受信信号のA/D変換可能範囲のうち実際にA/D変換が実行されるA/D変換実行範囲を限定し、受信信号のA/D変換を行う。A/D変換実行範囲は、測定深度に関わらずに所定のビット幅を有し、A/D開始ビットおよびA/D終了ビットで特定され、測定深度が増すほど、A/D変換実行範囲のA/D開始ビットおよびA/D終了ビットが漸減される。

(もっと読む)

撮像装置

【課題】A/D変換回路によるアナログ・デジタル変換動作に伴う消費電力を低減し、かつ、高い精度の変換結果を得ることができる撮像装置を提供する。

【解決手段】画素が行列状に複数配置された画素部と、対応する列の画素信号の大きさに応じた遅延時間でパルス信号を走行させる遅延素子が円環状に複数段連結された複数のパルス走行回路と、対応する1つの遅延素子からの遅延出力信号が入力され、入力信号を反転した第1の反転信号を出力する第1の反転回路と、第1の反転信号を反転した第2の反転信号を出力する第2の反転回路とを具備した複数のラッチ回路と、ラッチ回路による反転動作を制御するラッチ制御回路と、を備え、パルス走行期間に遅延出力信号の反転動作を禁止し、パルス走行期間が終了する前の予め定めたラッチタイミングのときに遅延出力信号の反転動作を許可し、ラッチ期間に第1の反転回路に第2の反転信号の反転動作を行わせる。

(もっと読む)

信号処理装置

【課題】2個のチップを接続する配線本数を削減しつつ、SN比の低下を抑制する。

【解決手段】第1のチップ10は、第2データD2を1ビットの第3データD3に変換するノイズシェーパー14と、第1信号配線L1を介して送信信号YPDMを送信し、第2信号配線L2を介してクロック信号YCLKを送信するPDM送信回路15とを備え、第2のチップ20は、第3データD3を6ビットのデータに変換する移動平均フィルター22と、5ビットの第5データD5を出力するクリップ回路24とDEM−DAC25とを備える。

(もっと読む)

1 - 20 / 530

[ Back to top ]