Fターム[5J024KA01]の内容

Fターム[5J024KA01]の下位に属するFターム

Fターム[5J024KA01]に分類される特許

41 - 60 / 69

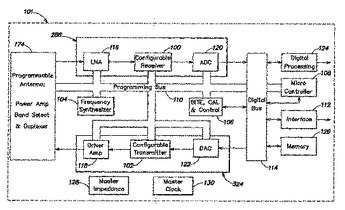

プログラム可能無線送受信機

完全に集積されたプログラム可能混合信号送受信機は、デジタル入力および出力を有する、周波数およびプロトコルにとらわれない無線周波数集積回路(RFIC)を備え、送受信機は、多数の無線周波数帯域および標準についてプログラム可能であるとともに構成可能であり、多くのネットワークおよびサービスプロバイダに接続することができる。RFICは、スパイラルインダクタを使用せず、その代りに向上された拡張性を可能にする伝送路インダクタを含む。送受信機の構成要素は、送受信機が異なる動作周波数帯域間で切り替わることを可能にするようにプログラム可能である。構成要素に結合されるデジタルレジスタのコンテンツを通じて周波数切り替えを達成することができる。  (もっと読む)

(もっと読む)

ノイズ除去回路構造及びノイズ除去方法

【課題】 コモンモードチョークコイルの反射特性に方向性を持たせることで、ノーマルモードノイズの効率的除去を図ったノイズ除去回路構造及びノイズ除去方法を提供する。

【解決手段】 送信器1と、受信器2と、伝送路3と、受信器2の入力部に実装されたコモンモードチョークコイル4とを備える。そして、高周波の信号に対するコモンモードチョークコイル4の反射特性に方向性を持たせた。具体的には、外部電極41a,42a側から見たコモンモードチョークコイル4の反射係数を小さく設定し、外部電極41b,42b側から見た反射係数を大きく設定した。これにより、受信器2のレシーバIC21側から戻ってきたノーマルモードノイズをコモンモードチョークコイル4で反射するようにしている。

(もっと読む)

インダクタンス素子及び信号伝送回路

【課題】 ESD対策として容量性素子を用いた場合でも、特性インピーダンスの低下を抑制することが可能な信号伝送回路を提供する。

【解決手段】 第1及び第2のインダクタ11,12は、互いに磁気結合している。第3及び第4のインダクタ13,14も互いに磁気結合している。第1のバリスタ31は、第1のインダクタ11の後段に位置し、当該第1のインダクタ11,21に電気的に並列接続される。第3のインダクタ21は、第1のインダクタ11と第1のバリスタ31との間に位置し、第1のインダクタ11に電気的に直列接続される。第2のバリスタ32は、第2のインダクタ12の後段に位置し、当該第2のインダクタ12に電気的に並列接続される。第4のインダクタ22は、第2のインダクタ12と第2のバリスタ32との間に位置し、第2のインダクタ12に電気的に直列接続される。

(もっと読む)

サージ吸収回路

【課題】

ICやLSI等の半導体デバイスは高圧の静電気によって破壊されたり、特性が劣化したりするため、静電気対策としてバリスタ等のサージ吸収素子が使用されている。バリスタを始めとするサージ吸収素子は浮遊容量成分や浮遊誘導成分を持つため、高速信号を扱う回路に適用すると信号を劣化させてしまう。浮遊容量と制御電圧・エネルギー耐量はトレードオフの関係にあるため、差動入力の高速信号用途に対して特性のよいサージ吸収素子を適用できないという課題があった。

【解決手段】

上記目的を達成するために、本願発明に係るサージ吸収回路は、相互誘導素子等を利用してサージ吸収素子の浮遊容量成分の影響をキャンセルする。

(もっと読む)

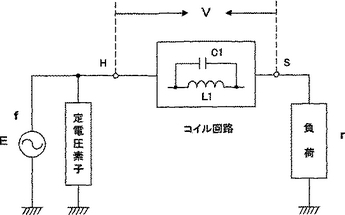

ノイズ防止コイル回路

通信入力部と通信回路の間に接続するコイル回路で、高周波信号の交流電圧をE、コイル回路の端子HS間の電圧をV、負荷の内部抵抗をrとする通信回路において、入力の高周波信号に対して信号の交流電圧Eと端子HS間の電圧の比がV/E<=0.1になり、インピーダンスが小さく、高周波信号を負荷に流すことができ、異常な大きいノイズに対しては、インピーダンスが非常に大きくなって、ノイズが負荷に流れるのを防止するノイズ防止コイル回路である。  (もっと読む)

(もっと読む)

フィルタ組立体

本発明では、電気フィルタ、該フィルタを有する回路、前記フィルタを有するコネクタ、これらを製作する方法およびこれらを使用する方法が提供される。フィルタは、G導電体、A導電体およびB導電体を有し、前記3導電体は、前記フィルタが回路に接続されていない場合、相互に電気的に絶縁される。 (もっと読む)

同調可能な回路構成とそのような回路構成を提供する方法

本発明は、少なくとも同調可能な第1のキャパシタ(C1)と同調適用手段を備える少なくとも1つの容量性分岐を含む同調可能な回路構成、または、アドミタンス回路構成に関する。本発明は、さらに、少なくとも第2のキャパシタ(C2)とインダクタ(L)を含む少なくとも1つの共振分岐を含む。第2のキャパシタ(C2)とインダクタ(L)とは直列に接続される。前記少なくとも1つの容量性分岐と前記少なくとも1つの共振分岐は並列に接続され、前記同調適用手段は、DCチューニング電圧(VDC)を印加するように適合される。前記第1と第2の内、少なくともいずれかのキャパシタのキャパシタンス(C1、C2)と、前記インダクタのインダクタンス(L)との内、少なくともいずれかは、アドミタンス回路構成を等価バラクタ構成を形成するバラクタ構成の同調能力の周波数依存性が、少なくとも選択された周波数範囲において制御可能であるように選択される。  (もっと読む)

(もっと読む)

LC複合部品及びそれを用いた実装部品

【課題】本発明は、バンドパスフィルタに用いられる性能を確保しつつ、電子機器の短小化、小型化を実現するLC複合部品及びそれを用いた実装部品を提供することを目的とする。

【解決手段】本発明は、基体2と基体2に設けられた第一〜第三端子部と、基体2上に設けられたヘリカル導体部と、基体内部であって、基体2上に設けられたヘリカル導体部と対向する第一内層導体6a,6bを有し、前記基体内部であって、基体内部に設けられた第一内層導体と対向し第三端子部に電気的に導通する第二内層導体7a,7bを有し、第一〜第三端子部がそれぞれ相互に電気的に非導通であり、ヘリカル導体部が、第一〜第三端子部の間のいずれかの位置に設けられた構成とする。

(もっと読む)

可変容量回路および可変容量回路の制御方法

【課題】 低電源電圧においても、可変容量素子の素子面積を増大させることや、制御電圧のレベル変換を行うことなく、可変容量素子の可変容量幅を最大限に広げることが可能な可変容量回路および可変容量の制御方法を提供すること。

【解決手段】 可変容量回路2は、容量値制御回路11、バラクタVA1およびVA2、抵抗素子R1およびR2を備える。容量値制御回路11は、入力される制御電圧VTに応じて、可変な出力電圧CNTOUTを出力することで、バラクタの両端の電位を同時に制御する。出力電圧CNTOUTは、制御電圧VTに対して、負の相関を有するように可変に調整される。端子間電圧VDの変動幅を、変動幅SA1から変動幅SA1a(レンジは±(Vcc1))へ拡大することができる。すると図5(B)に示すように、バラクタ容量値CVの可変領域を、可変領域CA1から可変領域CA1aへ広げることができる。

(もっと読む)

遅延線

【課題】簡単な構成で、通過帯域の広帯域化、絶対遅延時間偏差の低減化、絶対遅延時間の増大化を実現させる。

【解決手段】遅延線10Aは、第1の遅延回路12と第2の遅延回路14とを有する。第1の遅延回路12は、入力端子16と出力端子18とを有する帯域通過遅延線やその他の遅延線で構成される。第2の遅延回路14は、入力端子20、第1の出力端子22a、第2の出力端子22b及びアイソレーション端子24を備えたハイブリッドカプラ26と、第1の出力端子22aに接続された第1のリアクタンス部28Aと、第2の出力端子22bに接続された第2のリアクタンス部28Bとを有する。さらに、第1の遅延回路12の出力端子18と第2の遅延回路14におけるハイブリッドカプラ26の入力端子20とが電気的に接続されている。

(もっと読む)

フィルタ回路

【課題】 フィルタ回路に用いられる導線を細くしインダクタの大きさを小さくすることができ、また、電力線搬送通信の信号減衰比あるいは高周波電磁ノイズの除去比を、バイパス回路及び主回路のインピーダンスの差によって決めることができ、主回路のインダクタを小さくしたフィルタ回路を提供する。

【解決手段】 商用電源周波数と異なる周波数の信号を商用電源周波数に重畳して通信を行う電力線搬送通信の伝送路に配置され、電力線搬送通信の信号と、商用電源周波数に含まれる電磁ノイズと、を共に遮断するためのフィルタ回路であって、商用電源周波数を有する商用電源電流のみを遮断することなく通過させるための主回路と、電力線搬送通信の信号および電磁ノイズのみを遮断するためのバイパス回路と、を有する。

(もっと読む)

低域通過フィルタ、モジュール部品、及び、低域通過フィルタの製造方法

【課題】製品の小型化を図り得る低域通過フィルタ、及び、モジュール部品を提供する。

【解決手段】誘電体基体11は、第1の誘電体部分111と、第2の誘電体部分112とを含む。第2の誘電体部分112は、第1の誘電体部分111よりも高い比誘電率を持つ。信号線20は、第1の誘電体部分111の一面側、及び、第2の誘電体部分112の一面側に連続して形成されている。接地導体31は、第2の誘電体部分112の他面側に形成されている。

(もっと読む)

ノイズ削減用回路、デジタル増幅器、電子機器

【課題】 高周波成分を低減できると共に小型化できるノイズ削減用回路、デジタル増幅器、電子機器を提供する。

【解決手段】 厚さ方向に貫通する取り付け孔2aを備えた電気回路基板2を設ける。電気回路基板2の外縁から取り付け孔2aにかけてコア状に電気回路基板2を覆うように形成された磁性体からなる分割コア6を設ける。分割コア6の内部を通るように、取り付け孔2aの周囲を1回もしくは複数回巻き回して設けられた配線パターン5を設ける。

(もっと読む)

トラップ回路及びこれを備えた混合器

【課題】特性に優れ微調整が容易であり且つ安価なトラップ回路及びこれを用いた混合器を構成する。

【解決手段】コンデンサーとコイルとから成る並列共振回路を容量性リアクタンスを介して伝送経路に接続するように構成したトラップ回路において,前記容量性リアクタンスは一方は前記共振回路に接続されると共に,他方は自由端として伝送線路に容量結合するように形成され,絶縁体を被覆したジャンパー線であるように構成し可変自在の微小容量を形成した。

(もっと読む)

フィルタ回路

【課題】特性に優れ微調整が容易であり且つ安価なフィルタ回路及びこれを用いた共同受信用フィルタ回路を提供する。

【解決手段】 少なくとも絶縁板に形成した共振回路を容量性リアクタンスを介して前記絶縁板に形成した伝送経路に接続するように構成したフィルタ回路からなる共同受信用フィルタ回路において,

前記容量性リアクタンスは,一方は前記共振回路に接続されると共に,他方側は伝送線路の配設方向と略同じ方向となるように相互に沿わせるように配設したジャンパー線で,前記伝送線路に容量結合するように構成し可変自在の微小容量を形成した。

(もっと読む)

ラインフィルタ

【課題】 ライン上で複数のインダクタを近接配置して小型化を図ったとしても、各インダクタ同士の静電的な分離を行ってフィルタとしての高域特性の改善を行うことができるようにしたラインフィルタを提供する。

【解決手段】 第1および第2の巻線11,12をそれぞれ別々のコア21,22に巻いて第1および第2のインダクタを構成したことで、各インダクタが磁気的に分離される。また金属からなる遮蔽部材20が各コア21,22に近接すると共に接地されていることで、各インダクタが静電的にも分離される。さらに各コア21,22と接地面との間で浮遊容量が形成されることで、別途キャパシタを追加しなくとも、その浮遊容量と各インダクタとで等価的にT型フィルタが形成され、高域特性が改善される。

(もっと読む)

電子部品及びその製造方法

【課題】 従来技術より簡単な方法かつ簡単な構造を有し、高い信頼性の電子部品及びその製造方法を提供すること。

【解決手段】 絶縁基板10と、絶縁基板10上に直接設けられた1つ以上のキャパシタ12、13及びインダクタ14と、キャパシタ及びインダクタの上側方向からこれらを接続する配線15、16、17と、これらの配線と同一種類の導体で絶縁基板10上に形成された外部接続用のパッド部18〜21とを有する電子部品。例えば、電子部品は更にキャパシタ及びインダクタを覆う絶縁膜を有し、この絶縁膜上に前記配線が設けられている。

(もっと読む)

フィルタ素子

【課題】高い周波数において優れた減衰特性を有するフィルタ素子を提供する。

【解決手段】信号用導電体9と接地用導電体8とを帯状絶縁体7a,7bを介して重ねた状態で巻回することによって全体として筒状に形成されたコイル部5を備え、信号用導電体9は、外部に接続される出力部位Bが内周部に規定されると共に外部に接続される入力部位Aが外周部に規定され、接地用導電体8は、外部に接続される接地部位Cが外周部に規定され、コイル部5には、信号用導電体9の内周部に対向するようにしてシート状の補助接地用導電体10が巻き込まれている。

(もっと読む)

フィルタ素子

【課題】コモンモードノイズに対して優れたノイズ減衰特性を有するフィルタ素子を提供する。

【解決手段】各信号用導電体9a,9bは、帯状絶縁体7bを介して各接地用導電体8a,8bとそれぞれ対向し、各帯状導電体10a,10bは、帯状絶縁体7bを介して各帯状導電体10c,10dとそれぞれ対向し、帯状導電体10aは、一端側において信号用導電体9aおよび帯状導電体10dと接続され、帯状導電体10bは、一端側において信号用導電体9bおよび帯状導電体10cと接続されている。

(もっと読む)

極低温動作ローパスフィルタを備えた極低温電子素子・回路の極低温計測器

【課題】 極低温動作に適するローパスフィルタを登載した極低温計測器を提供する。

【解決手段】 本発明は、極低温電子素子或いは回路に、室温測定系から直流バイアス電流を供給する配線に侵入する雑音を除去するローパスフィルタを備えて、上記極低温電子素子或いは回路の特性を測定する。上記ローパスフィルタを極低温環境下に配置し、かつ上記ローパスフィルタを、バイアス供給入力側で2本の配線間に並列に接続されたキャパシタと、該配線の一方内に挿入された互いに並列に接続された抵抗及びインダクタンスにより構成する。

(もっと読む)

41 - 60 / 69

[ Back to top ]