Fターム[5J039AA04]の内容

パルスの操作 (9,993) | 直流レベルの移動 (50) | 結合コンデンサを持つもの(クランプ回路) (29) | ダイオード接続との組合せ (13)

Fターム[5J039AA04]に分類される特許

1 - 13 / 13

半導体装置

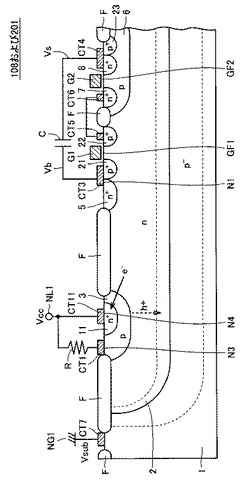

【課題】充電対象素子へ充電電流を効率的に供給することが可能な半導体装置を提供する。

【解決手段】充電対象素子Cに充電電流を供給する半導体装置1は、第1導電型の半導体層1と、充電対象素子Cの第1電極に結合される第1ノードN1を有し、半導体層1の主表面上に形成される第2導電型の第1の半導体領域2と、電源電圧が供給される電源電位ノードNL1に結合される第2ノードN3および第3ノードN4を有し、第1の半導体領域2の表面において半導体層1と間隔をあけて形成される第1導電型の第2の半導体領域3と、第2ノードN3および第3ノードN4から半導体層1への電荷キャリアの移動を制限する電荷キャリア移動制限部とを備える。

(もっと読む)

ゲート駆動回路及び半導体装置

【課題】応答性を損なうことなく能動クランプ素子の損失電力を低減できる能動クランプ回路を用いたゲート駆動回路及び半導体装置を提供する。

【解決手段】スイッチ素子Tr7のゲートを駆動するゲート駆動回路であって、制御信号に基づいてスイッチ素子Tr7を駆動する駆動部(トランジスタTr1,Tr2,Tr4,Tr5)と、スイッチ素子Tr7の第1主端子(ドレイン)と第2主端子(ソース)との間に印加される電圧が所定電圧以上の場合に、駆動部によるスイッチ素子Tr7に対する駆動動作を強制的に遮断して、スイッチ素子Tr7の第1主端子と第2主端子との間の電圧がクランプされるようにスイッチ素子Tr7を駆動するアクティブクランプ回路(ダイオードD1、ツェナーダイオードZD1、抵抗R1、トランジスタTr3,Tr6)とを備える。

(もっと読む)

比較回路

【課題】消費電流および回路規模をほとんど増大させることなく、容易に容量の充電時間を短くすることの出来る比較回路を提供する。

【解決手段】差動増幅回路10の出力が入力される単相増幅回路20の出力をNチャネルMOSトランジスタMN5からなるソースフォロワによるクランプ回路41に入力し、当該クランプ回路41により単相増幅回路20の入力を制限することにより、新たに定電圧源を設けることなく必要な充電電圧幅を狭めて容量Cpの充電時間を短くすることができる。また、単相増幅回路10の出力に応じて単相増幅回路10の入力を制限するので、単相増幅回路10の閾値電圧のばらつきや電源電圧の影響が問題にならない。

(もっと読む)

信号生成回路

【課題】回路に設けた容量をソフトスタート機能と共用可能でき、タイマ時間の設定の自由度が高くて精度の良いタイマ機能を実現可能な信号生成回路を提供する。

【解決手段】電流供給回路11から供給する電流Issを、回路に設けた共用する容量(Css)12に供給するとともに、差動増幅器21の比較入力としてクランプ回路20に加える。クランプ回路20は、容量(Css)12の電流供給回路11側端子電圧Vssとソフトスタート完了指示電圧Vc10を比較することにより、端子電圧Vssがソフトスタート完了電圧Vc1を上回った場合に、容量(Css)12に供給される電流Issを全て引き込むようしてクランプ機能を働かせる。クランプ回路20がクランプ作動状態に入る少し前に、差動増幅器21の出力Vo1が単相増幅器31のしきい値電圧Vtaを過ぎると、電流Issの切り替え(電流値Iss1から電流値Iss2への切り替え)が行われる。

(もっと読む)

ドライブ回路

【課題】低電圧の制御信号を高電圧の制御信号に変換して出力する高圧用のドライブ回路において、待機時の消費電力を削減することができるようにする。

【解決手段】低圧部1からの制御信号a1〜d1及びa2〜d2により高圧部2のトランジスタMN1〜MN8を駆動し、操作対象3に駆動信号を出力する。その際、低圧部1からの制御信号a1〜d1をそれぞれ論理積ゲートQ1〜Q4の一方の入力端子を介して高圧部2のトランジスタMN1,MN3,MN5,MN7のゲートに入力し、論理積ゲートQ1〜Q4の他方の入力端子には高圧部2のオン/オフ信号を入力する。

(もっと読む)

レベルシフト回路

【課題】外的要因による誤動作を防止して確実な信号伝達を行うレベルシフト回路。

【解決手段】第1電圧レベルを第1電圧レベルとは異なる第2電圧レベルに変換するレベルシフト回路であって、第2電圧レベルの論理電圧状態をセットするセット信号を送信するセットレベル回路21と、第2電圧レベルの論理電圧状態をリセットするリセット信号を送信するリセットレベル回路22と、第2電圧レベルでセット信号及びリセット信号を検出するための基準値を設定する基準レベル回路C3とを有し、セットレベル回路とリセットレベル回路と基準レベル回路との各々は、それぞれコンデンサC1〜C3を介して第1電圧レベルから第2電圧レベルに信号を伝達する。

(もっと読む)

高電圧、高速、高パルス繰返し数のパルス発生器

【課題】RF電力増幅器と関連する高パルス繰返し数の制限を解決する高電圧、高速、および高繰返し数パルス発生器(30)を提供する。

【解決手段】パルス発生器(30)は共振技術を利用して、短絡および開回路の双方の負荷状態中に、パルス発生器(30)の機能障害なしに、パルス発生器(30)の継続的な高電圧、高速、および高繰返しパルス数動作を可能にする電流制限特徴をもたらす。本発明の好適な実施例において、パルス発生器(30)は、DC電圧を高周波AC電圧に変換するように構成されているインバータ(40)と、前記AC電圧に応答して、AC電流源として動作するように構成されているコンバータ(50)と、前記AC電流源によって発生するAC入力電流に応答して、高電圧、高速、高繰返し数電圧パルスを発生させるように構成されているパルス整形部分(60)とを備える。

(もっと読む)

半導体素子制御装置

【課題】電源電圧が低下した場合でも、制御対象とする半導体素子を適切に制御することができる半導体素子制御装置を提供する。

【解決手段】電圧付与回路18は、電源電圧Vccを所定の閾値電圧Vthと比較して、Vcc≦Vthであれば、プリドライブ回路2のグランド側端子にグランドレベル近傍の電圧である仮想グランド電圧Vcpを付与し、Vcc>Vthであれば、前記グランド側端子に電源電圧Vccとクランプ制御用電圧Vgsとの差電圧を付与する。

(もっと読む)

バッファ回路、増幅回路、および、試験装置

【課題】出力信号の信号レベルを、設定されるクランプ電圧に応じて精度よく制御するバッファ回路を実現する。

【解決手段】入力信号に応じた信号を出力するバッファ回路であって、入力信号をベース端子に受け取る第1受信トランジスタと、エミッタ端子およびコレクタ端子が第1受信トランジスタの対応する端子に接続され、バッファ回路が出力する信号レベルを制限する第1クランプ電圧をベース端子に受け取る、第1受信トランジスタと同一極性の第1クランプトランジスタと、第1受信トランジスタおよび第1クランプトランジスタに対して共通に設けられ、第1受信トランジスタおよび第1クランプトランジスタに流れるエミッタ電流の総量を規定する第1電流規定部とを備え、第1受信トランジスタのエミッタ電圧に応じた出力信号を出力するバッファ回路を提供する。

(もっと読む)

電流クランプ回路

【課題】 バッファと抵抗の直列回路に並列にダイオードを接続し、この回路に入力信号が入力される増幅器の出力を入力する構成の電流クランプ回路は、負荷の電位が変動するとクランプ電位を一定値に保つことができなくなるという課題を解決する。

【解決手段】 入力信号が入力される増幅器の出力を定電流回路に入力し、この定電流回路の出力を、バッファと抵抗の直列回路にダイオードを並列接続した回路に入力するようにした。負荷の電位が変化してもダイオードの順方向電流が変化しないのでその順方向電圧が変化せず、クランプ電流を一定値に保つことができるという効果がある。

(もっと読む)

波形改善回路

【課題】コンデンサに充電された電荷の放電タイミングを最適にし、高速信号に対応できるようにした波形改善回路を提供する。

【解決手段】信号線4に伝送されるデジタルの信号Stの波形を改善する波形改善回路1は、信号Stのレベルが所定値を超えたことをレベル検出回路11Aが検出すると、その出力電圧Vdに基づいてスイッチ回路12Aが導通状態になり、電源電圧VBを充電回路13Aのコンデンサ131に印加してコンデンサ131を充電する。信号Stの電圧レベルが、コンデンサ131の充電電圧Vcよりも低くなったタイミングでコンデンサ131から信号線4へ、放電回路14Aのダイオード141を介して放電が行われ、アンダーシュートが改善される。

(もっと読む)

ビデオアンプ

【課題】ビデオアンプにおける非活性ラインのエミッタフォロアのベースエミッタ逆バイアスを排除する。

【解決手段】モード制御信号2によりスルーモード時には、ダイオード9が活性ライン側(エミッタフォロア13のベース)の電位をVf だけシフトダウンし、スイッチ10はVf シフトを非活性ライン側(エミッタフォロア14のベース)に伝達する。また、ローパスフィルタモード選択時には、ダイオード12が活性ライン側(エミッタフォロア14のベース)の電位をVf だけシフトダウンし、スイッチ11はVf シフトを非活性ライン側(エミッタフォロア13のベース)に伝達する。これにより、エミッタフォロア14または13のベースとエミッタが同電位になる。

(もっと読む)

電圧クランプ回路、スイッチング電源装置、半導体集積回路装置及び電圧レベル変換回路

【課題】 簡単な構成で安定的に動作する電圧クランプ回路と、高速動作を可能としたスイッチング電源装置を提供する。

【解決手段】 入力電圧が供給される入力端子にソース,ドレイン経路の一方を接続し、ゲートに制限すべき所定電圧を与え、ソース,ドレイン経路の他方と回路の接地電位との間に電流源を設けたMOSFETを用いて、上記ソース,ドレイン経路の他方から入力電圧に対応したクランプ出力電圧を得る。インダクタに流す電流を制御して上記出力電圧が所定電圧となるようにする第1スイッチ素子と、上記第1スイッチ素子がオフ状態のときに上記インダクタに発生する逆起電圧を所定電位にクランプする第2スイッチ素子を備えたスイッチング電源装置において、デッドタイムを設定する帰還経路に前記電圧クランプ回路を用いる。

(もっと読む)

1 - 13 / 13

[ Back to top ]