Fターム[5J039EE27]の内容

Fターム[5J039EE27]に分類される特許

1 - 20 / 25

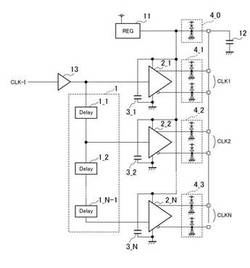

半導体装置、電子機器、及び出力波形歪み改善方法

【課題】N本のクロック信号を出力した際に生ずる出力波形歪みを改善した装置構成を提供する。

【解決手段】半導体装置は、所定周波数の入力クロック信号CLK−Iを入力して同一周波数の複数のクロック信号CLK1からCLKNを出力する。前記入力クロック信号は遅延部1_1から遅延部1_N−1により所定の遅延時間差を与えられ、前記複数のクロック信号として出力される。前記複数のクロック信号の立ち上がり及び立ち下がりを分散することで、共通の電源レギュレータ11への負荷が低減する。

(もっと読む)

クロックバッファ回路及びクロック分配回路

【課題】クロック源の消費電力を増大させることなく、動作クロック周波数に応じて駆動能力を変化させることにより消費電力低減可能なクロックバッファ回路を提供すること。

【解決手段】クロック信号を伝達するバッファ部102と、クロック信号の参照クロック信号に対する逓倍数をカウントし、バッファ部102に対して逓倍数に基づいたイネーブル信号を出力する駆動能力切替部101と、を備え、バッファ部102は、当該バッファ部102の入力に接続された入力インバータ7と、イネーブル信号によりオンオフが可能であって、それぞれの出力が当該バッファ部の出力に共通に接続された複数の出力インバータ13〜28と、を備え、入力インバータ7が1個のCMOSインバータからなるクロックバッファ回路。

(もっと読む)

半導体装置

【課題】立ち上がり時間と立ち下がり時間の差を解消しつつ、動作に伴う貫通電流の発生が防止されたレベルシフト回路を提供する。

【解決手段】互いに同じ回路構成を有するレベルシフト回路LV1,LV2と、レベルシフト回路LV1,LV2に相補の入力信号をそれぞれ供給する入力回路と、レベルシフト回路LV1,LV2から出力される相補の出力信号を同相に変換した後に短絡する出力回路とを備える。本発明によれば、同じ回路構成を有する2つのレベルシフト回路LV1,LV2を用いるとともに、これらレベルシフト回路LV1,LV2から出力される相補の出力信号を同相に変換した後に短絡していることから、レベルシフト回路LV1,LV2の動作速度差による貫通電流の発生がほとんど生じない。

(もっと読む)

半導体装置

【課題】スタンバイ時のサブスレッショルドリーク電流およびゲートリーク電流を低減させ、スタンバイモードからの復帰時の貫通電流の発生を防ぐことのできる半導体装置を提供する。

【解決手段】クロックゲート信号Gにより出力レベルが固定されるNANDゲート1およびインバータ2〜6と高電位電源線VDDとの間に接続された高閾値のPMOSトランジスタPH1〜PH6、および低電位電源線VSSとの間に接続された高閾値のNMOSトランジスタNH1〜NH6のスイッチングを、スタンバイ制御信号SB1、SB2およびそれぞれの反転信号SB1N、SB2Nで制御する。

(もっと読む)

インダクタオーバーヘッドなしで共振クロック分配ネットワークの固有周波数を選択する方法

共振クロック分配ネットワークのためのインダクタアーキテクチャが提示される。このアーキテクチャにより、選択的にインダクタを切り離すことによって共振クロック分配ネットワークの固有周波数の調整が可能になり、複数のクロック周波数でエネルギ効率の良い作動が実現する。提示されたアーキテクチャは、主として統合されたインダクタを備える共振クロックネットワーク設計を対象としており、面積オーバヘッドが現れない。このようなアーキテクチャは一般に、複数のクロック周波数を有しマイクロプロセッサ、ASIC、及びSOC等の高性能かつ低電力のクロッキング要件の半導体デバイスに適用可能である。更に、達成可能な性能レベルの応じた半導体デバイスのビニングに適用可能である。 (もっと読む)

共振クロック分配ネットワークの周波数スケール調整された作動のためのアーキテクチャ

共振クロック分配ネットワークのためのアーキテクチャが提示される。このアーキテクチャにより、選択的にイネーブルされるフリップフロップの導入によって、複数のクロック周波数での共振クロック分配ネットワークのエネルギ効率の良い作動が可能になる。提示されたアーキテクチャは、主として一体化インダクタを有する共振クロックネットワーク設計を目的としており、インダクタのオーバヘッドが出現しない。このようなアーキテクチャは一般に、複数のクロック周波数を有しマイクロプロセッサ、ASIC、及びSOC等の高性能かつ低電力のクロッキング要件の半導体デバイスに適用可能である。更に、達成可能な性能レベルの応じた半導体デバイスのビニングに適用可能である。 (もっと読む)

プログラム可能な駆動回路を備えた共振クロック分配ネットワークアーキテクチャ

プログラム可能なサイズのクロック駆動回路及びプログラム可能なデューティサイクルの基準クロックを使用して、共振又は非共振モードで複数のクロック周波数の中の任意の1つの周波数で作動する場合に小さなエネルギ消費で目標クロック立ち上がり時間及びクロック振幅を実現する共振クロック分配ネットワークアーキテクチャが開示さる。一般に、このネットワークは、複数のクロック周波数をもつ半導体デバイス、及び高性能で低電力クロックを必要とするマイクロプロセッサ、ASIC、及びSOC等に適用可能である。 (もっと読む)

共振クロックネットワークを従来モードで作動させるためのアーキテクチャ

共振クロック分配ネットワークのためのアーキテクチャが提示される。提示されたアーキテクチャにより、共振クロック分配ネットワークの従来モードでのエネルギ効率の良い作動が可能になり、クロック波形の目標仕様を満たすことができる。このようなアーキテクチャは一般に、複数のクロック周波数を有しマイクロプロセッサ、ASIC、及びSOC等の高性能かつ低電力のクロッキング要件の半導体デバイスに適用可能である。更に、アットスピード試験及び達成可能な性能レベルの応じた半導体デバイスのビニングに適用可能である。 (もっと読む)

入力インターフェース回路

【課題】有効なセットアップ特性及びホールド特性を良好に確保することが可能な入力インターフェース回路を提供すること。

【解決手段】本発明に係る入力インターフェース回路100は、データが外部入力される信号端子に接続される入力初段回路と、外部入力されるクロックと、入力初段回路に含まれるラッチ回路3、4へのラッチタイミング信号とを同位相に調整する位相調整回路6と、を備える。位相調整回路6は、クロックと当該クロックから擬似する擬似遅延回路の出力との比較結果に基づいてクロックツリー回路7を通過してラッチ回路3、4へと供給されるラッチタイミング信号の遅延時間を調整する。

(もっと読む)

ラッチ回路、フリップフロップ回路および半導体装置

【課題】ラッチ回路およびフリップフロップ回路のソフトエラー耐性の向上。

【解決手段】複数の回路ユニットIV1-IV4を有し、複数の回路ユニットの出力が他の反転回路の入力にフィードバックされ、2以上の入力端子1,2を有するデータ保持回路11と、2以上のクロックCK01,XCK01;CK02,XCK02にそれぞれ同期して、データ保持回路の2以上の入力端子に入力信号を入力する2以上の入力回路TG1,TG2と、を備え、データ保持回路は、2以上の入力端子に同時に入力信号Dinが入力されかつ2以上のクロックが同時に変化した時のみ、2以上の入力端子に正帰還がかかる。

(もっと読む)

スキャナー、電気光学パネル、電気光学表示装置及び電子機器

【課題】双方向転送機能を有したスキャナーで信号数を削減するとともに出力電位を安定化させる。

【解決手段】同一導電型のトランジスターで構成された複数の単位回路510からなる双方向転送可能なスキャナーであって、前記スキャナーを構成する前記単位回路510は、外部から与えられる信号を選択的に出力端子に出力する出力トランジスターを有し、前記出力トランジスターのゲート電極は第1の方向スイッチを介して他の単位回路510の出力端子である第1の端子に電気的に接続され、前記出力トランジスターのゲート電極は第2の方向スイッチを介してさらに他の単位回路510の出力端子である第2の端子にも電気的に接続される。

(もっと読む)

改良クロック・ゲーティング・セルを用いるシステム、及び方法

【解決手段】クロック・ゲーティング・セルは、入力イネーブル・ロジック及び出力ロジック回路と接続しているラッチを備え、ラッチは、出力ロジック回路の入力ノードでプル・アップ及び/またはプル・ダウン回路、及びクロック・ゲーティングセルが有効である場合、プル・アップ及び/またはプル・ダウン回路によって、出力ロジック回路入力ノードの早期充電または早期放電を防止する回路を備えている。 (もっと読む)

ミキサ

【課題】ダイレクトコンバージョン方式や低IF方式では局部発振器信号の高調波成分によるノイズを低減させる。

【解決手段】位相差がそれぞれ120°異なる3相信号を局部発振信号として受信信号と乗算し、それぞれの復調波の同相信号をキャンセルすることで、局部発振信号の高調波成分のうち、第3高調波によるノイズ成分をキャンセルすることができるミキサを提供する。

(もっと読む)

クロック信号生成回路、表示パネルモジュール、撮像デバイス及び電子機器

【課題】従来型のクロック信号生成回路は回路規模が大きく製造コストが高くなる。

【解決手段】遅延同期ループ型のクロック信号生成回路を、第1のクロック信号を遅延して第2のクロック信号を生成するディジタル型の遅延線路と、ディジタル型の遅延線路の遅延時間長を、各段のフリップフロップ出力により設定するリング型シフトレジスタと、第1のクロック信号と前記第2のクロック信号の位相関係に基づいて、リング型シフトレジスタに対するシフトクロックの供給を制御する遅延量制御部とで構成する。

(もっと読む)

クロック分配回路およびそれを用いたインターフェース装置

【課題】データの伝送速度および信頼性の低下を防止できるようにしたクロック分配回路およびそれを用いたインターフェース装置を提供する。

【解決手段】入力されたクロックを制御電圧によって可変とされた遅延を有するようにして分配クロックとして出力する電圧制御分配手段、及び前記データと前記分配クロックの位相差を用いて前記制御電圧を生成する制御電圧生成手段を備える。

(もっと読む)

半導体装置、半導体集積回路装置、及び許容位相差測定回路

【課題】低コストで電流ピークを効果的に抑制することができる半導体装置を得る。

【解決手段】ステップST1において、モジュールA21とモジュールB22とのクロック位相を一致させた後、ステップST2において、モジュールA21からモジュールB22にデータ転送を行う。その後、ステップST3において、モジュールA21のクロックCLKAとモジュールB22のクロックCLKBとのクロック位相差を所定の大きさに設定した後、ステップST4において、モジュールA21とモジュールB22とがそれぞれ独立に所定の演算処理を行う。そして、ステップST5において、モジュールA21のクロックCLKAとCPU25のクロックCLKPとの位相を一致させた後、ステップST6においてモジュールA21の演算結果をCPU25で読み取る。

(もっと読む)

ASIC及び画像形成装置

【課題】 スイッチング電流(過渡的な貫通電流)等による瞬間の過渡電流が、内部配線を流れる事による配線からの電磁波の直接輻射、及びその結果生じる内部電源の電圧降下や、急激な電圧変化によって、その信号がIO出力端子に重畳され出力される事で生じる間接輻射による不要輻射が、無視できないレベルとなってきている。

【解決手段】 エーシック内部のクロックのスキュー調整を分散化させそのエーシックを用いたシステムでエーシックで不要輻射が生じないようにする。特に同一のクロック端子に接続されてその端子からのクロックスキューが互いに異なるブロックを少なくとも2つ以上形成させ互いにクロックオンするタイミングがことならせ少なくとも同じ電源ライン間に複数のブロックにまたがって配置してコンタクトで電源接続されていることを特徴とする。

(もっと読む)

相補信号生成回路

【課題】

同相信号と逆相信号とのスルーレート差や遅延差を低減するとともに、製造ばらつきによる影響を低減できる相補信号生成回路を提供することができる。

【解決手段】

本発明にかかる相補信号生成回路は、入力信号に基づく逆相信号S21を反転した同相信号S22を生成するインバータ22と、逆相信号S21に応じて電源電位VDDとBAR端子間を導通させるトランジスタN12と、同相信号S22に応じてBAR端子と接地電位GND間を導通させるトランジスタN12と、同相信号S22に応じて電源電位VDDとTRUE端子間を導通させるトランジスタN13と、逆相信号S21に応じてTRUE端子と接地電位GND間を導通させるトランジスタN14と、を備えるものである。

(もっと読む)

半導体装置、表示装置、及び電子機器

【課題】ノイズによって誤動作することが少なく安定に動作し、消費電力が少なく、特性変動の少ない半導体装置、および前記半導体装置を有する表示装置、ならびに前記表示装置を有する電子機器を提供する。

【解決手段】出力端子を電源線に接続し、出力端子の電位変動を抑える。さらに、トランジスタの容量により、該トランジスタがオン状態となるゲート電極電位を維持する。また、逆バイアス用信号線により、トランジスタの特性変動を抑える。

(もっと読む)

シングルイベント耐性のラッチ回路及びフリップフロップ回路

【課題】シングルイベント現象が発生しにくく、シングルイベントトランジェント(SET)現象が発生してもそれの回路への影響を排除することができるラッチ回路及びフリップフロップ回路を提供する。

【解決手段】形成される強電界領域を狭くするために、ラッチ回路をデュアルポートインバータと、トランスミッションゲートを含まないデュアルポートクロックドインバータとから構成する。SET現象の影響をクロックに遅延時間を設けることにより排除するが、その遅延時間によってホールド時間が増加させられることを防止するために、一方の記憶ノードへは、その記憶ノード及び全体のラッチモードからスルーモードへの移行が遅延させられるような前縁エッジ遅延クロックが入力される。

(もっと読む)

1 - 20 / 25

[ Back to top ]