Fターム[5J039KK19]の内容

Fターム[5J039KK19]に分類される特許

41 - 60 / 72

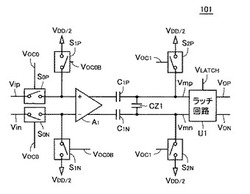

半導体集積回路

【課題】オフセット電圧の補正精度の劣化を防ぐことにより、電圧比較精度の向上を図ることが可能な半導体集積回路を提供する。

【解決手段】半導体集積回路101は、第1の入力電圧を第1のスイッチS0Pを介して受け、第2の入力電圧を第2のスイッチS0Nを介して受ける差動増幅回路A1と、第1のキャパシタC1Pを介して差動増幅回路A1の第1出力端子から受けた電圧および第2のキャパシタC1Nを介して差動増幅回路A1の第2出力端子から受けた電圧に基づいて第1の入力電圧および第2の入力電圧の比較結果を表わすデジタル信号を出力するラッチ回路U1と、第1のキャパシタC1Pの第2端子に結合される第1端子、および第2のキャパシタC1Nの第2端子に結合される第2端子を有する第3のキャパシタCZ1とを備える。

(もっと読む)

光センサ回路および光センサアレイ

【課題】光センサ回路のレイアウト面積を増大させることなく、光センサ回路の消費電流を一定に保ち、熱平衡状態を維持することのできる光センサ回路および光センサアレイを提供する。

【解決手段】光センサ回路は受光した光量に応じた値の光電流を生成する光電変換手段,増幅回路,増幅回路の入出力端子間に接続されて前記光電流を積分するコンデンサおよびコンデンサの両端に接続されたリセットトランジスタを有し、リセットトランジスタを待機モードでオンさせる。また、この光センサ回路を複数有する光センサアレイについても適用できる。

(もっと読む)

電流クランプ回路

【課題】 バッファと抵抗の直列回路に並列にダイオードを接続し、この回路に入力信号が入力される増幅器の出力を入力する構成の電流クランプ回路は、負荷の電位が変動するとクランプ電位を一定値に保つことができなくなるという課題を解決する。

【解決手段】 入力信号が入力される増幅器の出力を定電流回路に入力し、この定電流回路の出力を、バッファと抵抗の直列回路にダイオードを並列接続した回路に入力するようにした。負荷の電位が変化してもダイオードの順方向電流が変化しないのでその順方向電圧が変化せず、クランプ電流を一定値に保つことができるという効果がある。

(もっと読む)

入力切替方法および入力切替回路

【課題】 入力切替時に発生するボツ音ノイズを低減させる。

【解決手段】スイッチS11〜S14を有する第1の切替回路15と、演算増幅器16と、スイッチS15,S16を有する第2の切替回路17とを設け、第1の切替回路15のスイッチの1個をオフさせ別の1個をオンさせて入力切替を行うとき、第2の切替回路17のスイッチの1個をオフさせ別の1個をオンさせてボツ音ノイズを発生させ、該ボツ音ノイズにより第1の切替回路15の入力切替時に発生するボツ音ノイズを、演算増幅器16において同相除去させる。

(もっと読む)

半導体装置

【課題】デバイスの使用環境に応じて、動的にコンデンサの容量を変更し、ノイズを低減

する。

【解決手段】第1電源(110)と第2電源(111)との間に設けられたデカップリン

グ容量を有する半導体回路であって、半導体装置のノイズ量を測定する手段(102)と

、ノイズ量の測定結果に応じてデカップリング容量の容量値を可変させる手段(104)

とを備えることを特徴とする。

(もっと読む)

AD変換器、無線受信機

【課題】消費電力の増大を招くことなく、受動素子の数を削減しチップ占有面積を小さくして低コスト化を図ることが可能なAD変換回路を提供すること。

【解決手段】n次元ベクトルを表すm(n<m<2n)個のアナログ信号のそれぞれを1ビット以上に量子化してm個並列の量子化信号を生成する量子化部と、このm個並列の量子化信号をそれぞれ復号してm個の復号アナログ信号を生成する復号部と、このm個のアナログ信号のそれぞれと上記m個の復号アナログ信号のそれぞれとの差のそれぞれを定数倍してm個の増幅残差信号を出力する残差増幅部と、を有する変換ステージを複数縦続接続して備えた変換部と、この変換部の変換ステージそれぞれにおけるm個並列の量子化信号を該変換ステージの縦続位置に応じた遅延量を考慮して並列位置ごとに合成し、m個並列のディジタル信号を生成する合成部とを具備する。

(もっと読む)

電流電圧変換回路及び電流電圧変換方法

【課題】従来の電流電圧変換回路は、電源投入直後の初期状態に誤出力が発生する場合があった。

【解決手段】電流電圧変換回路は、入力電流に基づいて第1の電圧を生成する第1の電圧生成部と、第1の電圧生成部の入力電位と前記第1の電圧の昇圧側に所定の電圧差を有する第1の基準電圧を出力する基準電圧生成部と、前記第1の電圧と第1の電圧の降圧側に所定の電圧差を有し、前記第1の電圧の変動に対して遅延を有して変動する第2の電圧を生成する第2の電圧生成部と、前記第1の基準電圧と前記第2の電圧との大小関係に基づいて、いずれか一方を選択して第2の基準電圧を出力する第1の比較部と、前記第2の基準電圧と前記第1の電圧を比較する第2の比較部とを有する。

(もっと読む)

ピーク検波回路

【課題】ピーク検波回路が、ノイズに追従してピークを検出してしまう場合があった。

【解決手段】ピーク検波回路は、電源電位と出力端子の間に接続された第1のトランジスタと、入力信号と出力信号の差に基づいて、前記第1のトランジスタを駆動する増幅器と、前記第1のトランジスタに接続された第2のトランジスタと、前記第2のトランジスタにカレントミラー接続された第3のトランジスタと、前記第3のトランジスタに流れる電流値を設定する電流源とを有する。

(もっと読む)

MOSトランジスタ特性検出装置及びCMOS回路特性自動調整装置

【課題】回路規模及び消費電力の増大を抑えつつ、対象回路中のMOSトランジスタが飽和領域で動作するようにCMOS回路の動作状態を自動調整する。

【解決手段】CMOS回路特性自動調整装置は、対象回路(100)中のMOSトランジスタ(101a)のドレイン電圧を最小にするレプリカ信号を生成するレプリカ信号生成回路(10)と、レプリカ信号を受けるレプリカ回路(20)と、対象回路及びレプリカ回路中のMOSトランジスタのドレイン電圧をそれぞれ受ける電圧バッファ(30a,30b)と、これら電圧バッファの出力電圧をそれぞれのドレインに受けるMOSトランジスタ(101c,101d)と、これらMOSトランジスタに流れる電流の大小を比較する比較回路(40)と、その比較結果に基づいて対象回路及びレプリカ回路の動作状態を調整する調整回路(50)とを備えている。

(もっと読む)

クランプ回路および試験信号発生装置

【課題】ツエナーダイオードを用いたクランプ回路においては、動的抵抗によりクランプ電圧が変動し、クランプ波形上にこぶが発生する。また、従来のフィードバック方式のクランプ回路においては、サージ吸収用半導体素子をオフとするための遅延により、パルス幅が短縮したりフィードバックループ動作が不安定になったりする問題があった。平坦な正確なロードダンプサージ試験電圧を再現性良く発生させることは困難だった。

【解決手段】第1の基準電圧と第2の基準電圧が入力されるウィンドコンパレータの出力を、フィードバックループ回路のループ動作基準電圧として使用する。2つの基準電圧よって規定される電圧幅範囲に、ロードダンプサージ波形の検出電圧がフィードバック制御され、平坦なクランプ波形が得られる。ループ動作基準電圧はほぼ一定に保たれるので、広範なサージ電圧、サージ吸収電流の範囲において、ループ動作が安定化する。

(もっと読む)

サンプルホールド回路およびマルチプライングD/Aコンバータ

【課題】ホールド動作時におけるオペアンプの同相入力電圧を所定値に保つ。

【解決手段】サンプリング動作時に電圧Va〜Vfのうち少なくとも1つを入力電圧Vinとし、ホールド動作時にVg〜Vjのうち少なくとも1つを入力電圧Vin+ΔVとする。サンプリング動作時に入力電圧Vinが印加されるキャパシタの総容量値とホールド動作時に入力電圧Vin+ΔVが印加されるキャパシタの総容量値とを等しく設定し(第1条件)、ホールド動作時に入力電圧Vin+ΔVが印加される反転側キャパシタの総容量値と非反転側キャパシタの総容量値とを等しく設定し(第2条件)、サンプリング動作時に入力電圧Vinが印加される反転側キャパシタの総容量値と非反転側キャパシタの総容量値とが異なるように設定する(第3条件)。

(もっと読む)

発振器

【課題】素子特性のばらつき及び温度又は電源電圧の変動による影響を低減し、より安定した発振周波数を得られる発振器を提供することを目的とする。

【解決手段】入力される電流又は電圧により発振周波数foscが制御される可変周波数発振手段21を有する発振器であって、可変周波数発振手段21の発振周波数foscに応じた電圧V1を出力する周波数‐電圧変換手段22と、周波数‐電圧変換手段21の出力電圧V1と基準電圧Vref2とを比較して、それらの差を出力する比較手段23とを有し、比較手段23の出力を可変周波数発振手段21に供給して、可変周波数発振手段21の発振周波数foscを制御する発振器である。

(もっと読む)

ダイレクトチャージ型スイッチト・キャパシタ回路を含む電気回路

【課題】スイッチト・キャパシタ回路における寄生容量の影響を抑制する。

【解決手段】 キャパシタCの第1の端子に入力信号を供給し、第2の端子を基準電位に維持させることによってキャパシタCに入力信号の強度に応じた電荷を蓄積させる第1のモードと、キャパシタCの第1の端子をオペアンプ50bの出力端子TbOUTに接続し、第2の端子をオペアンプ50bの反転入力端子Tb(−)に接続する第2のモードとを選択可能とするスイッチング素子Toa,Tia,Tob,Tibとを含むメモリ単位52を少なくとも1つ備え、メモリ単位52に含まれるキャパシタCは、半導体基板の表面のウェル、ウェル上に形成された絶縁膜及び電極層とによって構成され、電極層をキャパシタの第1の端子とし、ウェルをキャパシタの第2の端子とすることによって上記課題を解決することができる。

(もっと読む)

チョッパアンプ回路および半導体装置

【課題】 センサブリッジのオフセット電圧及びオフセット電圧の温度特性を低減可能なチョッパアンプ回路の提供。

【解決手段】 センサブリッジのオフセット電圧と等しい電圧を発生するオフセット調整電圧発生回路と、オフセット電圧の温度特性と等しい電圧を発生するオフセット温度特性調整電圧発生回路とを設け、これらの出力電圧をチョッパ変調して、チョッパ変調されたセンサブリッジの出力信号から減算する構成とした。

(もっと読む)

スイッチ制御回路、ΔΣ変調回路、及びΔΣ変調型ADコンバータ

【課題】積分器の積分精度及びΔΣ変調回路の変調精度を向上させ、ΔΣ変調型ADコンバータにおける歪率劣化を抑制する。

【解決手段】第1〜第4スイッチを有するスイッチドキャパシタを用いて構成される積分器の前記第2及び第3スイッチと、前記第1及び第4スイッチとを相補的にオンオフするスイッチ制御回路であって、前記第1及び第4スイッチをオフ、前記第2及び第3スイッチをオンにする際には、前記第4スイッチをオフにする前に、前記第2スイッチをオンにする。

(もっと読む)

ゼロ交差検出を用いたサンプル値回路

【課題】仮想接地ノードを適切なレベルに維持すること等ができるサンプル値回路を提供すること。

【解決手段】サンプル値アナログ回路はレベル交差検出手段(30)を含む。レベル交差検出手段はサンプリングスイッチ(s22n、s23n、s22p、s23p)を制御して、入力信号が所定レベルと交差したことがレベル交差検出手段により検出された際に、出力電圧の正確なサンプルを供給する。レベル交差検出はゼロ交差検出であり得る。任意の同相帰還回路(400)により、出力同相電圧を略一定に保つことができる。

(もっと読む)

データスライサ

【課題】入力信号を適切にスライス可能なデータスライサを実現する。

【解決手段】現在の入力電圧信号の最大値と最小値とだけではなく、入力電圧信号に含まれるヘッダパターンにおける平均電圧と、ヘッダパターン検出完了時のピーク電圧・ボトム電圧とにも基づいて、スライスレベルを算出する。具体的には、スライスレベルをS15、ヘッダパターンの平均電圧をS6、ヘッダパターン検出完了時のピーク電圧をS7、ヘッダパターン検出完了時のボトム電圧をS8、最大電圧検出・保持部に保持された最大電圧をS10、最小電圧検出・保持部に保持された最小電圧をS11として、スライスレベルの電圧値を、S15=S6+(S10+S11)/2−(S7+S8)/2と算出する。

(もっと読む)

オフセット補正回路

【課題】 頻繁なリフレッシュを必要とせず、小さな回路規模でオフセットばらつきを吸収してオフセット補正を行うことのできるオフセット補正回路を実現する。

【解決手段】 オペアンプ回路1において、スイッチ素子S1を閉じてスイッチ素子S2を開く。ラッチ回路DLはオペアンプ1aの出力電圧をラッチしてそれに応じたQ出力を行い、制御回路2aはオフセット補正用信号s1をオペアンプ1aのオフセット調整入力端子ORに入力する。それによってオフセット補正された出力電圧をさらにラッチ回路DLによりラッチし、残りのオフセットを補正するためにオフセット補正用信号s1を微調整していく。このようにして、そのときのラッチが何回目であるかに応じて重み付けされた補正量でオペアンプ1aの出力電圧のオフセットを量子化し、2値の論理信号として制御回路2a内に記憶する。

(もっと読む)

オフセットエラー修正およびそれに同一のものを使用するシステムを用いるサンプル&ホールド回路および方法

サンプル&ホールド回路は、入力信号のサンプルを格納するサンプリングコンデンサと、サンプリングコンデンサに格納されるサンプルを出力する出力ステージと、入力信号をサンプリングし、サンプリングコンデンサにサンプルを格納する入力回路を含む。入力回路は、第1の動作段階中に入力信号を選択的にサンプリングし、第2の動作段階中に入力信号のサンプルをホールドする自動ゼロ化入力バッファを含む。自動ゼロ化入力バッファは任意のオフセットエラーをキャンセルする。入力回路はまた、第2の動作段階中に、サンプリングコンデンサをサンプル&ホールド回路の入力と選択的に結合するため、また、第1の動作段階中にサンプリングコンデンサを自動ゼロ化入力バッファの出力と選択的に結合するためのスイッチング回路を含む。  (もっと読む)

(もっと読む)

振幅検出回路、振幅検出方法及び光通信装置

【課題】 ピーク検出に必要なキャパシタを用いることなく時定数を大幅に小さくできる振幅検出回路を実現する。

【解決手段】 aに示す入力信号(入力in)を折り返してbに示す折り返し信号を得る。この折り返し信号波形は、入力inのハイからロウ、ロウからハイへの遷移点で入力の立ち上がり・立下り時間のためへこみqが生じており、検出した振幅値に誤差が生じる。一方、入力inを微分してcに示す微分波形を得、さらにこれを折り返してdに示す折り返し信号を得る。次に、bとdとを加算することにより、へこみqがdにより補正され、ピーク値Pに示すような入力inのピーク値に対応する平坦な出力を得ることができる。即ち、キャパシタを用いないで入力inの振幅を検出することができる。

(もっと読む)

41 - 60 / 72

[ Back to top ]