Fターム[5J039KK23]の内容

Fターム[5J039KK23]の下位に属するFターム

リングカウンタ (3)

アップダウンカウンタ (37)

Fターム[5J039KK23]に分類される特許

241 - 259 / 259

パルス生成装置及びパルス生成方法

【課題】メモリ素子を用いて複数個のパルスを生成しうる多重パルス生成装置及びパルス生成方法を提供する。

【解決手段】複数個のパルス信号を生成するためのものであって、複数個の時間間隔信号及び第1選択信号を受信し、第1選択信号に応じて前記複数個の時間間隔信号のうち何れか一つを選択し、選択された時間間隔信号を出力する第1スイッチング部及び複数のパルス状態及び第2選択信号を受信し、第2選択信号によって前記複数のパルス状態のうち何れか一つを選択し、選択された時間間隔信号により決定される第1時間間隔の間に選択されたパルス状態を出力する第2スイッチング部を備えることを特徴とするパルス生成器。

(もっと読む)

デュアルループPLLおよび逓倍クロック発生装置

【課題】 初期起動においてロックアップ時間を短縮できるデュアルループPLL(Phase Looked Loop)を提供すること、および消費電力低減に寄与する逓倍クロック発生装置を提供すること。

【解決手段】 デュアルループPLLは、位相を比較する位相比較器1を有する位相比較ループと、周波数を比較する周波数比較器7を有する周波数比較ループとを有するデュアルループPLLを備え、周波数比較器7は、位相比較器1に用いる、外部基準クロックラインCLex11から入力される基準クロック信号と異なる、キャリブレーションクロックラインCLcal18から入力される入力信号を用いて周波数比較を行う。また、上記デュアルループPLLを用いて、逓倍クロック発生装置を構成する。

(もっと読む)

半導体装置

【課題】

オシレータから出力されるクロックに発振異常が発生した場合、その異常に対応してマイクロコンピュータの動作を適切に停止させる。

【解決手段】

発振器と、発振異常検出部とを具備する半導体装置を構成する。発振異常検出部は、その発振器から出力されるクロックを計測して得られたカウント値に基づいてその発振器の周波数を特定する。そして、その周波数が所定の周波数範囲外のときに、発振異常信号を生成する。

(もっと読む)

電源装置

【課題】 商用電源等の交流電源から供給される交流電力の周波数検出を、コストアップを最小に抑えまた簡易な構成で実現出来る電源装置を提供する。

【解決手段】 交流電力を整流する整流回路2と、前記交流電力の周波数を検出する周波数検出装置4、5、6、8と、前記整流回路から供給される直流電力により動作し、所要の電力を負荷に供給する電源回路3、7とを備えた電源装置において、前記電源回路は、前記交流電力投入時に当該電源回路を起動させるために必要となる電圧を発生させる起動抵抗4を有し、該起動抵抗は前記整流回路2の入力側に接続されており、前記周波数検出装置は、前記抵抗に直列に接続した発光素子5と、該発光素子近傍に配置した光電変換素子6と、該光電変換素子の出力により動作するパルスカウント手段8とを有する構成として、前記課題を解決する。

(もっと読む)

確率的パルス発生器と差分絶対値演算器及びこれを用いたマンハッタン距離演算装置

本発明の確率的パルス発生器(1)は、ランダムに変動する変動信号(VC)を発生する変動信号発生器(61)と、一方の入力信号と他方の入力信号との大小に応じてHighまたはLowの2値信号(Vout)を出力する比較器(3)とを備え、比較器(3)に変動信号発生器(61)から変動信号(VC)が前記一方の入力信号として入力され、それにより、比較器(3)が前記他方の入力信号(VS)の大きさに対応した数のパルスを確率的に出力する。  (もっと読む)

(もっと読む)

遅延同期ループ及びこれを具備した半導体メモリー装置

【課題】 互いに異なる位相を有した複数個のクロック信号を発生することができる遅延同期ループを提供する。

【解決手段】 クロック信号とフィードバッククロック信号との位相差を検出し、前記位相差によって変化する複数ビットの遅延制御信号を発生する位相検出器12と、前記複数ビットの遅延制御信号に応答して前記クロック信号を遅延させて複数個の出力クロック信号及び前記フィードバッククロック信号を発生する所定個数の縦続接続された第1の遅延セルを具備する第1の遅延器18と、前記複数個の遅延制御信号に応答して反転クロック信号を遅延させて複数個の反転出力クロック信号を発生する所定個数の縦続接続された第2の遅延セルを具備する第2の遅延器22と、前記複数個の出力クロック信号及び前記複数個の反転出力クロック信号の中で関連があるクロック信号を位相混合して補正された複数個の出力クロック信号を発生する位相混合器24とを含む。

(もっと読む)

周波数ロック検出器

【課題】 1つのカウンタとクロック個数差検出部とを利用して、位相が同期されない2クロック信号の周波数を比較して、周波数ロックを判別(所望の周波数精度内にあるか否かを判別)することにより、集積化が容易な周波数ロック検出器を提供すること。

【解決手段】 本発明は、周波数ロック検出器において、外部から基準クロック信号を受け取って、基準クロック信号のクロック個数をカウントするためのカウンタと、前記外部から受け取った基準クロック信号と、前記基準クロック信号と互いに位相が同期されない復元されたクロック信号とのクロック個数の差を検出するためのクロック個数差検出部と、前記カウンタと前記クロック個数差検出部の結果値とを利用して、周波数ロックを判別するためのロック判別部とを備える。

(もっと読む)

集積回路

【課題】 内部回路が逓倍クロック信号に基づいて動作することによる電源変動の影響が、クロック信号出力回路に及ぶことを極力回避できる集積回路を提供する。

【解決手段】 電源配線14がデジタル回路群17を経由してクロック信号出力回路11に電源供給を行う経路中にローパスフィルタ22を配置し、電源配線14を伝搬しようとするノイズ成分をアナロググランド側に逃がして除去する。そして、クロック信号出力回路11による逓倍クロック信号fmの発振精度を向上させ、その逓倍クロック信号fmに同期して動作するデジタル回路群17における通信ブロック16の通信精度等を向上させる。

(もっと読む)

電力計測装置

【課題】 バースト波の判別とデューティ比を検出することができる電力計測装置を提供する。

【解決手段】 バースト波のデューティ比を計測する電力計測装置であって、入力されたバースト波を検波し、得られる検波電圧を出力する検波部3と、検波電圧が所定の検波電圧閾値を超える場合に周期Sのクロックでカウントを行い、得られるカウント値Nを出力し、バースト波の周期Tを持つパルス列でカウントのクリアを行うデューティ比検出部5と、(S×N/T×100)をデューティ比[%]として算出する計測部4とを備えた

(もっと読む)

クロック信号出力回路

【課題】 電源電圧が変動する場合でも、逓倍クロック信号の出力精度を極力維持することができるクロック信号出力回路を提供する。

【解決手段】 周期カウンタ4では、基準クロック信号fsの周期をリングオシレータ1より出力される高速クロック信号frでカウントし、周期カウンタ24ではN分周された基準クロック信号fsの周期をN分周した高速クロック信号frでカウントする。そして、有効判定回路25は、周波数逓倍動作を開始した直後はマルチプレクサ26により周期カウンタ4側の周期データD1を選択して逓倍クロック信号fmを迅速に出力し、それ以降、周期カウンタ24によってカウントされた周期データD1’が有効になる時間が経過すると、当該周期データD1’を選択するようにマルチプレクサ26を切替えて周波数逓倍演算処理の対象とする。

(もっと読む)

2つのPLLを用いた微小時間差回路及び時間測定回路

【課題】1桁以上時間分解能を向上させることができる微小時間差回路及び時間測定回路を提供する。

【解決手段】所定の基準クロック信号を受け、第1発振周波数を発生する電圧制御発振回路を具える第1位相同期ループ回路と、前記第1位相同期ループ回路と同じ基準クロック信号を受け、前記第1発振周波数と異なる第2発振周波数を発生する電圧制御発振回路を具える第2位相同期ループ回路とを具え、前記第1位相同期ループ回路と前記第2位相同期ループ回路の出力信号の遅延時間差から微小時間を得る。

(もっと読む)

PWM信号の量子化装置及び量子化方法

【課題】 PWM信号の量子化処理時の量子化精度を向上した量子化装置及び量子化方法を提供する。

【解決手段】 量子化装置(1)は、PWM信号を入力し、入力したPWM信号を時間軸方向に所定数倍した信号を生成する増幅器(16)と、増幅器(16)からの出力信号を受け、出力信号の”H”または”L”区間の時間幅を量子化し、デジタル信号として出力する量子化回路(6)とを備える。

(もっと読む)

接点入力装置

【課題】 DIモジュールには接点入力信号に重畳するノイズを除去する機能はあるが、どの程度ノイズが重畳しているかを知ることはできなかった。そのため、機器の老朽化や環境の変化によって徐々に増加するノイズを早期に発見することができなかったという課題を解決する。

【解決手段】 接点入力信号の変化をカウントする入力値変化カウンタと、この接点入力信号の確定値の変化をカウントする入力確定値変化カウンタを有し、入力確定値変化カウンタと入力値変化カウンタのカウント値の差が設定値を越えると警報メッセージを出力する。接点入力信号にどの程度ノイズが重畳しているかを知ることができる。

(もっと読む)

データ処理方法

【課題】 DIデータの取りこぼしの発生を防止する。

【解決手段】 水晶振動子23のクロック周波数を分周回路31で分周し、パルス信号を生成する。一方、STB信号検出部回路33は、STB DI更新信号を検出し、この検出部回路33の出力には、STB LOCK信号が送出される。カウンタ34は、STB信号検出後、一定時間の間“High”状態で、その後、次のSTB信号が到来するまで“Low”状態の信号を生成する。この “Low”状態の信号の後のSTB LOCK信号と分周回路31で生成されたパルス信号は、ダブルラッチ信号発生回路32に入力されると、ダブルラッチ信号発生回路32は、DIオン/オフ時間比選択信号によるDIオン時間の間にダブルラッチ信号を2回発生する。このラッチ信号が入力データラッチ回路35に与えられると、その出力にはデータ取りこぼしが回避されたデータ得られる。

(もっと読む)

ディジタルシステムパフォーマンス向上のシステムおよび方法

本発明は、ワーストケース要求クロックよりも低い周期を使用してディジタル計算を実行し、同時に、同じハードウェアを有する第2のシステム上で、ワーストケース想定クロックよりも大きな周期を使用して同じ計算をする。計算の出力は、エラーが生じたかどうかを決定するため比較される。2つの答えに差異が存在すれば、より速い計算がエラーでなければならず、システムは遅い方のシステムからの答えを使用する。一実施形態において、本発明は、より遅いシステムの2つのコピーを利用し、各々のコピーは、メインシステムの半分の速さで実行される。しかし、2つのコピーは、全体としてメインシステムと同じレートで結果を生成する。メインシステムは、従来のレートよりもはるかに速いレートで実行する。したがって、本発明は、ハードウェアの数が多くなるにしても、パフォーマンスを改善する。  (もっと読む)

(もっと読む)

分周器

奇数の除数を有する分周器は、周波数を持つ周期クロック信号(Ck)を受信するためのクロック入力を有し、第1の偶数は前記奇数の除数より小さい、偶数の除数を有するバイナリカウンタ(10)を備える。回路はさらにバイナリカウンタに結合され、前記カウンタ(10)の入力(IN)に入力されるカウント終了信号(EOC)を、クロック信号(Ck)の偶数周期毎にクロック(Ck)の間生成するカウント終了回路(20)を備える。回路はさらにバイナリカウンタ及びクロック信号(Ck)に結合され、奇数の除数によって分割された周波数信号(Ck)の周波数と実質的に同じ周波数を有する出力信号(OUT)を生成する出力生成器(30)を含む。  (もっと読む)

(もっと読む)

クロックフィルタ回路及びクロックフィルタテスト回路

【課題】 入力信号に対する位相遅延の少ない、不要な高周波信号を除去したクロック信号を得ることができるクロックフィルタ回路を提供することを課題とする。

【解決手段】 ドレイン間が抵抗素子102を介して接続され、ゲートに入力クロック信号CLK1が入力される、ソースがVDDに接続されたトランジスタ100及び、ソースが接地されたトランジスタ102、トランジスタ102のドレインと接地とに接続されたコンデンサ103、トランジスタ100のドレインに接続されたCMOSインバータ104を備えた遅延回路2、遅延回路2と同様の構成で信号CLK1の代わりに、信号CLK1の反転が入力される遅延回路3、信号CLK1の反転と遅延回路2の出力とを入力とするAND回路4、入力クロック信号CLK1と遅延回路3の出力とを入力とするAND回路5、及びAND回路4の出力をRESETとし、AND回路5の出力をSETとするRS型フリップフロップを備えた。

(もっと読む)

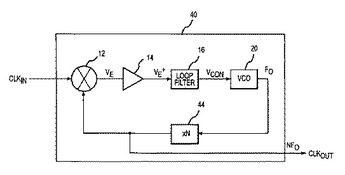

低電力と低いタイミング・ジッタのフェーズ・ロック・ループと方法

フェーズ・ロック・ループは、入力クロック信号から出力クロック信号を生成する。出力クロック信号は、クロック・ツリーを通して結合されて、出力クロック信号の位相を入力クロック信号の位相と比較する位相検出器にフィード・バックされる。出力クロック信号は、位相検出器から出力を受け取るように結合された制御入力を有する電圧制御発振器と、電圧制御発振器の出力に結合された周波数逓倍器とによって生成される。を持っている電圧制御発振器によって生成される。結果として、電圧制御発振器が相対的に低い周波数で動作することによって相対的に小さな電力を使用する一方、周波数逓倍器により生成されたCLKOUT信号は、相対的に高い周波数を持っている。  (もっと読む)

(もっと読む)

妨害耐性を向上させるための方法及び集積回路

少なくとも一つのマイクロプロセッサチップ又はマルチプロセッサマイクロコントローラ(1)と少なくとも一つの別のモジュール(2)との間で、誤り信号が一つ以上の誤り信号の形で伝送される、集積回路(16)の妨害耐性を改善する方法であって、その伝送に関して、このマイクロプロセッサ又はこれらのマイクロプロセッサのクロック周波数に依存しない最小パルス長を規定して、その最小パルス長以降において、誤り配線上で所定のパルス長を持つ信号を誤りと解釈する方法を記載している。また、この発明は、特に、前記の方法を実行するための集積回路であって、特に、分離して配置された電力部品を有する、少なくとも一つのマイクロプロセッサチップ又はマルチプロセッサマイクロコントローラ(1)及び少なくとも一つの別のモジュール(2)と、少なくとも一つの誤り配線(3,4)を介して、誤りパルス(6,6’)を順番に出力するための一つ以上のパルス拡大機器と信号遅延機器の両方又は一方とを備えた集積回路に関する。  (もっと読む)

(もっと読む)

241 - 259 / 259

[ Back to top ]