Fターム[5J039KK23]の内容

Fターム[5J039KK23]の下位に属するFターム

リングカウンタ (3)

アップダウンカウンタ (37)

Fターム[5J039KK23]に分類される特許

121 - 140 / 259

カウンタ回路、レイテンシカウンタ及びこれを備える半導体記憶装置、並びに、データ処理システム

【課題】ハザードなどが発生しやすい高周波信号を正しくカウントすることが可能なカウンタ回路を提供する。

【解決手段】クロック信号LCLKに基づいて、互いに位相の異なる分周クロックLCLKE,LCLKOを生成する分周回路100と、分周クロックLCLKEをカウントする第1のカウンタ210と、分周クロックLCLKOに同期して第1のカウンタ210のカウント値を取り込む第2のカウンタ220と、第1及び第2のカウンタ210,220のカウント値を排他的に選択する選択回路230とを備える。本発明によれば、第1及び第2のカウンタ210,220のカウント値の関係が常に一定に保たれることから、ハザードが生じた場合であってもカウント値がジャンプするのみであり、カウント値が不定となることがない。

(もっと読む)

DLL回路、および半導体装置

【課題】DLLクロックが消失した場合に、位相検知における誤判定の結果を基に、遅延量が更新されることを回避し、ロック制御におけるDLLクロックサイクルの短縮化と、DLL回路の動作安定性の向上を図る。

【解決手段】本発明のDLL回路は、入力されるクロック信号の遅延量を制御する遅延信号を出力する遅延制御回路13と、この遅延信号に基づいた遅延量をクロック信号に付加し、DLLクロックとして出力する遅延回路12と、DLLクロック信号のクロッキング動作の有無を検知するDLLクロック検知回路31とを備える。そして、DLLクロック検知回路31は、DLLクロックのクロッキング動作が検知されない場合に、遅延制御回路13による遅延量の更新制御を停止させる。

(もっと読む)

小数位相検出器を用いたクロック生成

入力信号から、低減されたスキューを有する1つまたはより多くの出力クロック信号を生成する回路が提供される。入力信号は、出力クロック信号の周波数とは異なった周波数を有するオリジナルクロックの遷移から導き出される遷移を有する。出力クロック信号の周波数は、入力信号についての周波数と、整数比との乗算からの積である。回路は、積算器と、小数位相検出器と、ループフィルタを含む。積算器は、数値的オフセット値を数値的位相値に周期的に追加する。出力クロック信号は、この数値的位相値から生成される。小数位相検出器は、数値的位相値から、入力信号の遷移の各々についてのそれぞれの数値的位相誤差を生成する。ループフィルタは、それぞれの数値的位相誤差のフィルタリングから数値的オフセット値を生成する。  (もっと読む)

(もっと読む)

周波数異常検出回路

【課題】従来の、監視クロックが被監視クロックよりも高い周波数を使用する周波数異常検出回路は、高コストかつノイズ対策が必要で実装が困難であり、また、監視クロックが被監視クロックよりも低い周波数を使用する周波数異常検出回路は、クロック固着のタイミングによっては異常を検出できないだけでなく、リセット時にシフトレジスタを構成するすべてのレジスタ出力が“0”となるので、警報が発出されないようにする構成を別途設けなければならない問題があった。

【解決手段】クロック周波数の上限異常は被監視クロック数のカウント数と上限値との大小比較にて検出し、下限異常は、同期化した監視クロックの立ち上がりエッジにて出力する正極性パルスと、当該パルス出力で”High”を出力する初回エッジホールド回路出力と、下限値と被監視クロック数のカウント値の大小を比較するコンパレータ出力との論理積の出力にて検出すること。

(もっと読む)

デューティ補正回路

【課題】伝送速度が異なる複数のマンチェスタ符号化信号のデューティ比を補正可能なデューティ補正回路を得ること。

【解決手段】本発明にかかるデューティ補正回路は、マンチェスタ符号化された受信信号の連続する2つの立上りエッジの間隔または立下りエッジの間隔に基づいて受信信号の伝送速度を判定するシンボル周期判定回路7と、受信信号の“Hレベル”または“Lレベル”の継続時間を観測するエッジ検出回路2およびカウンタ3と、観測結果および判定結果に基づいて波形歪みを検出する波形歪み検出回路4と、波形歪みが検出された場合に波形歪み発生期間、受信信号を反転することにより波形の補正を行うセレクタ5と、を備えることとした。

(もっと読む)

デューティ補正装置

【課題】同一の符号化方式で符号化され、かつ伝送速度が任意の複数種存在する受信信号のいずれに対してもデューティ比を補正可能にする。

【解決手段】符号化された受信信号の“H”または“L”の継続時間を観測する観測手段と、受信信号の符号シンボル周期に関する長パルス用設定値と短パルス用設定値に基づいて、観測された“H”または“L”の継続時間から波形歪みを検出する波形歪み検出手段と、波形歪みが検出された場合に、波形歪み発生期間の受信信号を反転することにより波形の補正を行う波形補正手段と、受信信号の立上りまたは立下りを検出し、その次の立上りまたは立下り検出までの間隔に基づいて判定した現在の受信信号の符号シンボル周期に基づいて上記長パルス用設定値と短パルス用設定値を設定する符号シンボル周期判定手段を備えた。

(もっと読む)

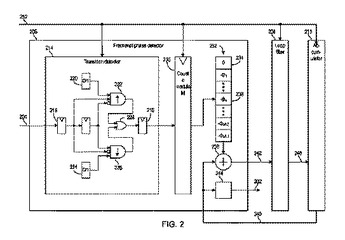

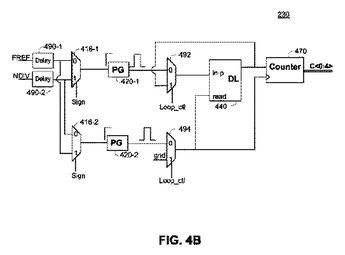

完全デジタル位相ロックループにおける位相デジタル変換器

位相デジタル変換器と、完全デジタル位相ロックループと、完全デジタル位相ロックループを有する装置とについて、本明細書で説明する。位相デジタル変換器は、時間デジタル変換器を駆動する位相周波数変換器を含む。時間デジタル変換器は、位相周波数変換器によって出力された位相差の絶対値と符号とを判断する。時間デジタル変換器は、タップ付き遅延線とループフィードバックカウンタとを利用して、ループ追跡プロセスによくある小さいタイミング差およびループ収集プロセスによくある大きいタイミング差の測定を可能にする。タップ付き遅延線は、基準期間の部分の測定を可能にし、基準クロックの速度に関する要件を低減することによって位相デジタル変換器のより低電力の動作を可能にする。  (もっと読む)

(もっと読む)

デューティ検出回路およびCDR回路

【課題】入力データが交播パターン以外の場合であっても、高速かつ高精度にデューティを検出する。

【解決手段】デューティ検出回路は、入力データDinのデューティの変動に応じてパルス幅が増減するパルス信号Errと基準パルス幅を示すパルス信号Refとを出力するパルス信号生成回路1と、パルス信号Errまたはパルス信号Refのいずれかを選択的に出力するセレクタ2と、パルス信号Refの遷移がない場合はセレクタ2にパルス信号Refを選択させ、パルス信号Refの遷移がある場合にはセレクタ2にパルス信号Errを選択させるパルス信号遷移判定回路3と、セレクタ2から出力された信号の平均電圧レベルとパルス信号Refの平均電圧レベルとの差を、入力データDinのデューティ100%からの変動分を表す検出信号Outとして出力する出力回路4とを備える。

(もっと読む)

接点信号の入力装置

【課題】接点信号からチャタリングを除去した入力ができ、かつ継続的にオン/オフ状態が繰り返される異常接点信号の入力を防止できる。

【解決手段】接点信号の入力装置は、論理部1に接点のオン信号が入力された時点から起動するメカニカルチャタリング防止用タイマと、接点のオン信号が入力された時点から起動するチャタリング継続検出用タイマと、カウンタおよびディジタル処理手段を備える。

接点のオン信号が入力された時点からメカニカルチャタリング防止用タイマのタイマ時間ΔT1後もオン信号が入力されたときにチャタリングを除去したオン出力信号を生成する。接点のオン信号が入力された時点からチャタリング継続検出用タイマのタイマ時間ΔT2後まで継続的にオン出力信号を生成したときに接点入力異常の出力を生成する。

(もっと読む)

クロック信号分周回路および方法

【課題】大きな回路規模を必要とすることなく、有理数分周した出力クロック信号のサイクル時間変動を抑制するとともに、分周時に出力クロック信号の位相を調整する。

【解決手段】クロック選択制御回路100により、入力クロック信号のサイクルごとに、分周比に応じた一定サイクル時間を有する基準分周クロック信号と入力クロック信号との位相関係を示す位相計算値111を計算するとともに、位相調整信号に応じてその値を増減し、この位相計算値111に基づいて、出力動作のうち、基準分周クロック信号の位相と近いクロック信号を生成するための出力動作を指示する制御信号102,103を生成する。クロック選択回路101により、制御信号102,103に基づいて、入力クロック信号のクロックパルスをそのまま非反転で出力するか、反転して出力するか、マスクして出力しないか、のいずれかの出力動作を選択して実行することにより、出力クロック信号を生成する。

(もっと読む)

半導体装置

【課題】 この発明は、テスト兼用端子に高電圧のノイズが入力された場合でも容易にテストモードに入ることのない半導体装置を提供する。

【解決手段】 この発明は、通常動作モードと、テストモードを備えた半導体装置において、前記半導体装置は、振幅が電源電圧以内の通常信号と振幅が前記電源電圧より高い高電圧信号の入力が可能なテスト兼用入力端子Aと、テスト兼用入力端子Aに入力される高電圧信号を検出する高電圧検出回路10と、高電圧検出回路10からの高電圧信号が所定のパターンで変化したことを検出するパターン検出回路20と、検出したテスト兼用入力端子Aから高電圧信号が所定のパターンで印加された場合に、前記通常動作モードから前記テストモードに切り換える切り替え手段30と、備えた。

(もっと読む)

クーロンカウンタ

【課題】回路規模の縮小を可能としたクーロンカウンタを提供する。

【解決手段】センス抵抗Rsの両端に生じる電位差を入力電圧とし、入力電圧に比例したカウント値を出力するクーロンカウンタ100であって、サンプリング容量Cs1と、積分容量Ci1とを有し、入力電圧をサンプリング容量Cs1でサンプリングすると共に、サンプリングされた入力電圧に比例する電圧を積分容量Ci1で積分するスイッチト・キャパシタ方式の積分回路と、積分容量Ci1で積分された電圧を反映して積分回路から出力される出力電圧Vout-がVCM以上の場合は信号Qを出力し、出力電圧Vout-がVCMよりも低い場合は信号QBを出力するコンパレータ5と、信号Q、QBとを一定時間カウントしてその差をカウント値として出力するロジック回路10と、を備える。

(もっと読む)

半導体装置

【課題】コストの増加を抑制しつつ、高いチューニング精度を維持するとともに、チューニングに要する時間の増加を抑制できる半導体装置を提供する。

【解決手段】レベルシフト回路5を構成する可変抵抗R1およびR2に加えて、BGR回路1のVBGR電圧の出力ノードと可変抵抗R1との間に接続された付加抵抗RUと、可変抵抗R2と基準電圧との間に接続された付加抵抗RDとを有し、付加抵抗RUおよびRDのそれぞれに並列して、Nチャネル型のMOSトランジスタTUおよびTDが接続されている。

(もっと読む)

クロック発振回路

【課題】簡単な回路構成でスペクトラム拡散を行うことが可能なクロック発振回路を提供する。

【解決手段】基本クロック信号を発振する基本クロック発振器と、基本クロック信号と非同期で、かつ基本クロック信号より短い周期としたクロック調整信号を発振する調整クロック発振器と、基本クロック信号をクロック調整信号の1周期分シフトして、クロックシフト信号として出力するシフト回路23cと、基本クロック信号およびクロックシフト信号を1周期ごとに切り替えて、調整クロック信号として出力する切替回路として機能するカウンタ回路23aおよびセレクタ回路23bとを備えている。シフト回路23cは、基本クロック信号をクロック調整信号の立ち上がりで同期する第2フリップフロップ23c1で形成され、カウンタ回路23aは、基本クロック信号を2分周する第1フリップフロップ23a1および第1インバータ23a2で形成されている。

(もっと読む)

物体検出回路及びそれを備えた物体検出装置

【課題】受光素子にて検知されたパルス光の波長が判別可能であり、外乱光による影響をさらに低減し、検出精度の高い物体検出回路を実現する。

【解決手段】物体検出回路1は、パルス変調された光を照射する発光素子12と、被検出物体の有無に応じて発光素子12からの出力パルス光を受光する受光素子13と、受光素子13にて検知されたパルス光の波長を判別する信号検出回路19とを備える。

(もっと読む)

イコライザのテスト回路および集積回路の評価システム

【課題】量産テストでの使用に適したイコライザのテスト回路および集積回路の評価システムを提供する。

【解決手段】テスト回路1は、擬似乱数データ生成部11が、擬似乱数データを生成し、重み付け係数生成部12が、符号間干渉の干渉強度設定用の重み付け係数を生成し、擬似符号間干渉データ生成部13が、擬似乱数データのビット系列に応じて擬似乱数データに擬似的な符号間干渉を発生させ、重み付け係数により振幅を変化させた擬似符号間干渉データを生成し、ドライバ14が、生成された擬似符号間干渉データを差動信号として出力する。比較部15は、イコライザ100の出力をサンプリング回路200によりサンプリングしたデータを、符号間干渉発生前の元の擬似乱数データと比較し、カウント部16が、比較部15により検出された不一致の数をカウントする。

(もっと読む)

同期クロック生成回路及び同期クロック生成回路を備えたアナログ/ディジタル角度変換器と角度検出装置

【課題】安価に構成することができる同期クロック生成回路を提供する。

【解決手段】角度検出器10の出力する2相の角度信号S1とS2を、第1二乗回路11と第2二乗回路12でそれぞれ二乗し、それぞれの二乗信号を加算回路14で加算し、加算回路14の出力信号の直流成分をフィルタ16で除去する。フィルタ16の出力信号と基準電位とを比較するコンパレータ18で矩形波に変換し、その矩形波の位相を移相器20で所定量遅らせる。移相器20の出力信号を、同期化分周回路22で角度検出器10に供給する励磁信号に同期して1/2分周して同期クロックSQ3を得る。

(もっと読む)

パルス出力装置

【課題】適正なパルス数のパルス信号が出力されない状態を検知可能なパルス出力装置を提供する。

【解決手段】 CPU3は、入力信号に応じたパルス数を算出するパルス数算出手段31と、パルス数算出手段31により算出されたパルス数のパルス信号を出力するパルス出力手段32と、後述するパルス用カウンタ61によりカウントされたパルス数と、パルス数算出手段31により算出されたパルス数とを照合する照合手段33を構成する。外部回路6には、パルス出力手段32から出力されたパルス信号のパルス数をカウントするパルス用カウンタ61と、パルス用カウンタ61によりカウントされたカウント数を格納するレジスタ62と、レジスタ62に格納されたカウント数をシリアル通信によりCPU3に向けて送信する通信手段63と、が設けられる。

(もっと読む)

クロック生成回路およびその使用方法

【課題】基準信号の周波数を逓倍又は分周したクロック信号を生成するクロック生成回路において、一つの基準信号から任意周波数のクロック信号を発生可能とする。

【解決手段】クロック生成回路1は、リング状に連結したm個の遅延素子DUからなるパルス遅延回路10と、各遅延素子DUから順次出力される通過信号P1〜Pmに基づき、基準信号CKIの周期を遅延素子DUでの遅延時間を単位として表した周期データDTを生成する周期測定部20と、除数又は乗数として使用される設定値MNを格納する設定値レジスタ50と、周期データDTに、設定値MNを乗・除してクロック信号の出力周期を表す制御データCDを生成する制御部30と、制御データCDと通過信号P1〜Pmとに基づき、基準信号CKIを分周又は逓倍したクロック信号CKOを出力する出力部40とを備え、実数で表された設定値MNを用いる。

(もっと読む)

信号伝達回路

【課題】新たな構成で複数種類の入力信号を1つのトランスを介して入力側から出力側へ伝達することが可能な信号伝達回路を提供することを目的とする。

【解決手段】温度入力信号が立ち上がると、トランス4の1次側コイルに第1のパルス電圧を発生させ、温度入力信号が立ち下がると、1次側コイルに第2のパルス電圧を発生させる1次側回路2と、トランス4の2次側コイルに第1のパルス電圧に対応するパルス電圧が発生すると、温度出力信号を立ち上がらせ、2次側コイルに第2のパルス電圧に対応するパルス電圧が発生すると、温度出力信号を立ち下がらせる2次側回路3とを有して信号伝達回路1を構成し、FAIL入力信号が立ち上がると、1次側コイルに第3又は第4のパルス電圧を発生させ、2次側コイルに第3又は第4のパルス電圧に対応するパルス電圧が発生すると、FAIL出力信号を立ち上がらせる。

(もっと読む)

121 - 140 / 259

[ Back to top ]