Fターム[5J039KK23]の内容

Fターム[5J039KK23]の下位に属するFターム

リングカウンタ (3)

アップダウンカウンタ (37)

Fターム[5J039KK23]に分類される特許

41 - 60 / 259

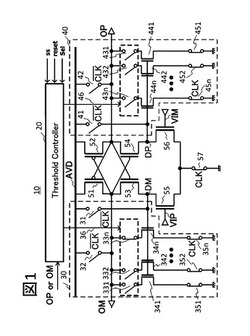

増幅回路及びその増幅回路を含むアナログデジタル変換回路

【課題】オフセットキャンセル動作において発生する消費電力を低減可能なコンパレータを提供する。

【解決手段】差動入力信号を受ける一対のMOSトランジスタのドレインと高電位電源線に接続し、一対のMOSトランジスタのドレインに接続する差動出力ノード間の電位差を増幅し、増幅後の電位を差動出力ノードに保持する増幅部と、差動出力ノード間の電圧増幅時に、差動出力ノードにキャンセル電流を流し、増幅部による増幅動作後に、一対のMOSトランジスタのドレイン電圧に応じて差動出力ノードへのキャンセル電流の流入を遮断するキャンセル回路と、差動入力信号の一方の信号の電位を他方の信号の電位と等しく設定し、差動出力ノード間の電位差を増幅したときに、差動出力ノード間の電位が、キャンセル電流を注入する前に比較し、キャンセル電流の注入後に逆転するように、キャンセル電流を設定するコントローラと、を備える増幅回路。

(もっと読む)

クロック発生回路

【課題】ピーク電力の抑制が可能なクロック発生回路を提供すること。

【解決手段】基準クロック11のエッジをカウントし所定のクロックサイクル数毎にタイミング信号を生成するカウンタ回路5と、所定のクロックサイクル数と等しいビット数を有するビットマップ情報14aを記憶するビットマップ回路4aと、基準クロック11からビットマップ情報14aが示す組み合わせでパルスを間引きして間欠するパルス列である間欠クロック12aを生成しタイミング信号に応じて出力する間欠クロック生成回路2aと、所定のクロックサイクル数と等しいビット数を有するビットマップ情報14bを記憶するビットマップ回路4bと、基準クロック11からビットマップ情報14bが示す組み合わせでパルスを間引きして間欠するパルス列である間欠クロック12bを生成しタイミング信号に応じて出力する間欠クロック生成回路2bと、を有する。

(もっと読む)

局部発振器

【課題】デジタル制御発振器の出力と参照信号とが非同期であっても、安定したPLL動作を確立できる局部発振器を提供することを目的とする。

【解決手段】デジタル制御発振器の発振信号と前記参照信号との位相差を発振器分数位相として出力し、また、前記発振信号の位相が、前記参照信号の位相に対して、前記発振信号の半周期よりも位相が遅れている場合に「−1」、遅れていない場合に「+1」の補整情報を出力する時間デジタル変換器と、|前記補整情報−予測位相情報|>|前記補整情報+前記第1位相情報−前記予測位相情報|の場合に、前記第1位相情報に前記補整情報を加算したものを第2位相情報として出力し、|補整情報−発振器予測位相|>|補整情報+第1位相情報−発振器予測位相|でない場合に、前記第1位相情報を第2位相情報として出力する補正部と、を備えている。

(もっと読む)

局部発振器

【課題】消費電力を増大させることなく、TDCレスが可能な局部発振器を提供することを目的とする。

【解決手段】発振器制御ワードに応じた発振周波数のN倍の周波数の発振信号を出力するデジタル制御発振器と、前記発振信号をN分周して、2N相のクロックを出力する分周器と、前記クロックを前記参照信号でラッチして、第1位相情報として出力する第1のフリップと、前記参照信号を遅延させて、遅延参照信号として出力する可変遅延回路と、前記クロックを遅延参照信号でラッチして、第2位相情報として出力する第2のフリップフロップと、前記可変遅延回路の遅延量を制御する遅延制御手段と、前記1および第2の位相情報に基づいて、発振器整数位相を出力するデータ変換手段と、発振器整数位相と前記発振器分数位相とを加算し、加算値を第3位相情報として出力する加算器とを備えている。

(もっと読む)

クロックシステム

【課題】第2の発振回路の起動を待つことなく第1の発振回路の出力により高精度なクロック信号を得る。

【解決手段】クロックシステム1は、CR発振回路11、水晶発振回路12、及びトリミング回路15を含む。CR発振回路11は、内部回路17に供給されるクロックCLK1を生成する。水晶発振回路12は、CR発振回路11の発振周波数の調整に使用される。トリミング回路15は、CR発振回路11と水晶発振回路12の間の発振周波数差の検出結果に基づいて、CR発振回路11の発振周波数を調整する。

(もっと読む)

パワーオンリセット信号を制御するためのシステムおよび方法

クロック異常検出回路

【課題】クロック異常を検出する精度を向上させる技術を提供する。

【解決手段】被検査クロックを遅延させる第1の遅延回路の出力と第2の遅延回路の出力よりLow期間を決める。定められたLow期間に信号変化をカウントする。被検査クロックとカウント値により異常検出する。第1の遅延回路の出力と第2の遅延回路の出力よりHigh期間を決める。定められたHigh期間に信号変化をカウントする。被検査クロックとカウント値により異常検出する。Low期間の異常とHigh期間の異常を統合する。

(もっと読む)

クロック制御回路およびマイクロコンピュータ

【課題】消費電力の低減を図る。

【解決手段】クロック補正回路30に第1クロック信号の周波数の補正を実施させる補正間隔を計時する補正間隔タイマ80と、クロック補正回路30による第1クロック信号の周波数の補正に要する補正時間を計時する補正時間タイマ70と、補正間隔タイマ80により計時される補正間隔毎に、補正時間タイマ70に補正時間の計時を開始させるとともに第2クロック発振回路20を動作状態にさせてクロック補正回路30に第1クロック信号の周波数の補正を実施させ、補正時間タイマ70により補正時間の計時が通知されると第2クロック発振回路20を停止状態にさせる制御手段40、50、60を備える。

(もっと読む)

受信装置及びゲイン設定方法

【課題】受信特性を向上させることのできる受信装置を提供する。

【解決手段】受信装置は、受信データD1に基づいて抽出クロックCLKを生成するクロックデータリカバリ回路2と、受信データD1のジッタ量に応じて、上記クロックデータリカバリ回路2内のフィルタ回路11のゲインパラメータG1を設定するゲイン設定部3とを有する。

(もっと読む)

クロック分周回路、クロック分周方法及びプログラム

【課題】クロック分周回路において動作電圧を低下させて消費電力を削減すること。

【解決手段】クロック分周回路は、入力クロック信号をカウントしてD進カウント値とするカウンタと、出力クロック信号をカウントしてN進カウント値とするカウンタと、出力クロック信号と出力クロックの最小周期と出力クロックの半周期精度差分とD進カウント値とN進カウント値とから立ち上がり及び立ち下がりトグルイネーブル信号を求めるトグル位置解析部と、入力クロック信号の立ち上がりエッジにおいて立ち上がりトグルイネーブル信号に応じてトグルする第1のフリップフロップと、入力クロック信号の立ち下がりエッジにおいて立ち下がりトグルイネーブル信号に応じてトグルする第2のフリップフロップと、第1及び第2のフリップフロップの出力の間における排他的論理和を求めて出力クロックする排他的論理和回路と、を備えている。

(もっと読む)

半導体装置、及びそのテスト方法

【課題】シリアルインタフェース回路におけるCDR回路の位相追従機能を、ループバックテストによって検査する。

【解決手段】本発明による半導体装置において、PLL回路2は、周波数変調された参照クロック1に基づいて、受信用クロック21及び送信用クロック22を生成する。シリアライザ3は、送信用クロック22に応じたタイミングでパラレルデータ33をシリアル化して出力する。CDR回路8は、受信用クロック21に基づいて、受信データ20に対するクロックデータリカバリを実行し、再生データ24を生成する。デシリアライザ14は、再生データ24をパラレル化する。ループバック回線19は、シリアライザ7から出力されたシリアルデータ18を、受信データ20としてCDR回路8に入力する。

(もっと読む)

擬似ランダム信号発生装置、通信システム、及び画像形成システム

【課題】放射ノイズを低減する。

【解決手段】N段のDフリップフロップ(DFF)を備え、隣り合う前段のDFFの非反転端子が隣り合う後段のDFFの入力端子に接続され、最終段のDFFの非反転端子及び最終段以外の1つの段のDFFの非反転端子がEXORを介して最初の段のDFFの入力端子に接続され、最終段のDFFの非反転端子から2N−1ビットのビットパターンを繰り返したパターン信号を出力するパターン信号出力回路10、パターン信号が2N−1ビット出力される毎にビットパターン長を示す信号を出力するビットパターン長カウント回路12、ビットパターン長を示す信号に基づきパターン信号出力回路10の非反転端子及び反転端子から複数の端子を複数個ずつ繰り返し選択するための選択信号を出力するM進カウンタ回路14、及び選択信号に応じて該複数の端子から出力された信号を選択し、選択した信号を擬似ランダム信号として出力するタップ出力シフト回路16を含む。

(もっと読む)

電子回路、電子機器、デジタル信号処理方法

【課題】多相クロックを使用してデジタル信号処理を行なう場合に、クロック信号の各位相関係を正しく保ったまま高速動作が要求される各デジタル信号処理部まで多相クロックを分配できるようにする。

【解決手段】基準タイミング生成部110は、高速信号処理部140全体のトグル頻度よりもトグル頻度の低い基準タイミング信号J0を生成して局所タイミング再生部120に供給する。局所タイミング再生部120は、高速信号処理部140全体のトグル頻度よりもトグル頻度の低いクロック信号であって、高速信号処理部140におけるデジタル信号処理の基準となる複数のクロック信号でなる多相タイミング信号J2を生成して高速信号処理部140に供給する。高速信号処理部140と局所タイミング再生部120を1対1で設け、1つの局所タイミング再生部120から複数の高速信号処理部140へ多相タイミング信号J2を分配しないようにする。

(もっと読む)

PLLロック検出回路、及びPLLロック検出回路を有するPLLシンセサイザ回路

【課題】適切にPLL回路ロックがなされているか否かを検出する。

【解決手段】PLL回路ロックがなされているか否かを検出するPLLロック検出回路を構築する。ここにおいて、そのPLLロック検出回路は、基準発振器から供給される基準発振周波数を示す基準発振周波数信号と、前記基準発振周波数を分周して得られたリファレンス周波数を示し位相比較器に供給されるリファレンス周波数信号と、VCOから供給される電圧制御発振周波数を分周して得られた比較周波数を示し前記位相比較器に供給される比較周波数信号とを受ける、そして、前記リファレンス周波数信号と前記比較周波数信号とに基づいて、前記PLL回路ロックを示すロック検出信号を出力する。

(もっと読む)

スプレッドスペクトルクロック発生器及びそれを含む電子装置

【課題】新しい変調率及び変調周波数を有するスプレッドスペクトルクロック信号を生成することができるスプレッドスペクトルクロック発生器を提供する。

【解決手段】スプレッドスペクトルクロック発生器は、第1スプレッドスペクトルクロック信号を受信して第1スプレッドスペクトルクロック信号の平均周波数に対応する周波数信号を出力する発振回路と、周波数信号を受信して第2スプレッドスペクトルクロック信号を発生する位相固定ループと、第1及び第2スプレッドスペクトルクロック信号を受信して、第2スプレッドスペクトルクロック信号の平均周波数が第1スプレッドスペクトルクロック信号の平均周波数と近接するように位相固定ループを制御する制御回路を含む。このようなスプレッドスペクトルクロック発生器は、スプレッドスペクトルクロック信号を受信して、希望する変調率及び変調周波数を有する新しいスプレッドスペクトルクロック信号を発生する。

(もっと読む)

スペクトラム拡散クロックジェネレータ

【課題】入力クロックの周波数変化に依存して変調プロファイルが変化しないスペクトラム拡散クロックジェネレータを提供する。

【解決手段】スペクトラム拡散クロックジェネレータは、切替信号に応じて入力クロックを遅延し、出力クロックとして出力する遅延ラインと、入力クロックの周期を計測する入力クロック周期計測部と、入力クロック周期計測部の計測結果に応じて、1変調周期当たりの出力クロックのサイクル数、および、あらかじめ設定された変調度に対応する入力クロックの所定サイクル当たりの出力クロックの周期の変調ステップ幅を算出し、算出されたクロックサイクル数および変調ステップ幅に基づいて切替信号を生成する遅延ライン制御部とを備えている。

(もっと読む)

位相周波数比較器およびシリアル伝送装置

【課題】ループ帯域幅を安定させる位相周波数比較器を簡易な回路で提供する。

【解決手段】基準クロック102とフィードバッククロック103とを入力とし、周波数シンセサイザへのアップ信号と周波数シンセサイザへのダウン信号とを出力する位相周波数比較器において、第1位相周波数比較回路106と、第2位相比較回路107と、前記基準クロック102と前記フィードバッククロック103とを入力とし、前記第1位相周波数比較回路106の入力と前記第2位相比較回路107の入力とに、所定の相対的な遅延を与える遅延回路部108とを備え、周波数比較を前記第1位相周波数比較回路106で行い、位相比較を前記第1位相周波数比較回路106とラッチを制御した前記第2位相比較回路107とで行う位相周波数比較器。

(もっと読む)

データ送出装置、データ受信装置、及びデータ送受信システム

【課題】従来のHDMIのオーディオクロック伝送システムでは、サイクルタイムスタンプ値が変動してオーディオクロックの精度が劣化してしまう。

【解決手段】データのサンプルクロックを所定の分周比で分周してクロックを生成するクロック分周手段と、クロック分周手段で生成したクロックをカウントするカウント手段と、カウント生成手段で計測したカウント値を平均化する平均化手段と、平均化手段で取得した平均カウント値のビット数を削減するノイズシェーピング手段と、基本クロック、ノイズシェーピング手段で生成したカウント値及びクロック分周手段で使用した分周比を送出する送出手段を備える。

(もっと読む)

動的バスクロックを制御するための装置及び方法

【課題】本発明は動的バスクロックを制御するための装置及び方法に関する。

【解決手段】本発明による動作バスクロックを制御するための装置は、少なくとも一つのマスターモジュールと、少なくとも一つのスレーブモジュールと、前記少なくとも一つのマスターモジュールと前記少なくとも一つのスレーブモジュールが送受信するデータを媒介するバスと、前記少なくとも一つのマスターモジュールの動作情報(Activity)を考慮してバスクロックの周波数を決定するバス周波数制御機と、前記バス周波数制御機で決定した周波数を発生させて生成したクロックを前記少なくとも一つのマスターモジュールと前記少なくとも一つのスレーブモジュール及び前記バスに提供するクロック発生器と、を含む。

(もっと読む)

雑音除去回路及び雑音除去回路を備えた半導体装置

【課題】高い周波数のクロックを用いずに雑音を除去できる雑音除去回路及び雑音除去回路を備えた半導体装置を提供する。

【解決手段】データ入力信号がロウレベル又はハイレベルになると活性化しハイレベル又はロウレベルを維持するとクロック信号に同期して非活性化する第一及び第二のリセット信号を生成する第一及び第二のリセット信号生成回路と、クロック信号の反転信号を計数し第一又は第二のリセット信号によりリセットされる第一及び第二のカウンタ回路と、セレクタ回路とセレクタ回路の選択した信号をクロックに同期して出力する出力フリップフロップ回路とを備え、セレクタ回路がハイレベル又はロウレベルに固定された信号、出力フリップフロップの出力信号のいずれかを第一及び第二のカウンタ回路の出力信号の論理レベルにより選択して出力するデータ出力回路と、を備える。

(もっと読む)

41 - 60 / 259

[ Back to top ]